安路科技亮相ICCAD-Expo 2024 展示安路科技在FPGA领域创新产品威廉希尔官方网站

12月11-12日,“上海集成电路2024年度产业发展论坛暨第三十届集成电路设计业展览会”(ICCAD-Expo 2024)在上海世博展览馆隆重举行,安路科技精彩亮相本次展会,向业内展示安路科技在FPGA领域创新的产品威廉希尔官方网站

及全面的解决方案,吸引了参展观众的广泛关注。 FPGA芯片以其灵活可编程特性广泛应用于工业控制、汽车电子、机器视觉、视频显示等多领域。安路科技专注于FPGA硬件及软件威廉希尔官方网站

的研发,为客户提供丰富的产品矩阵及高性价比的解决方案。在本次展

- 专栏安路科技官微

- 6天前

- 327

- 0

- 0

FPGA厂商安路科技荣获“2025 IC风云榜年度国际市场先锋奖”

12月14日,由中国半导体投资联盟、爱集微网共同举办的“2025半导体投资年会暨IC风云榜颁奖典礼”在上海中心隆重举行,安路科技荣膺“年度国际市场先锋奖”。 作为一家专注于FPGA领域的民营企业,安路科技自成立以来,始终坚持创新驱动,致力于成为全球领先的FPGA芯片供应商。为此,公司紧贴市场动态,快速迭代芯片产品,提升性能、降低功耗,增强市场竞争力。公司还积极拓宽产品线,巩固并扩大市场份额,覆盖更多应用场景,如汽车电子、数据

- 专栏安路科技官微

- 6天前

- 374

- 0

- 0

芯华章发布FPGA验证系统新品HuaProP3

近日,国内EDA(电子设计自动化)领域的佼佼者芯华章公司,正式对外宣布其最新研发的FPGA验证系统——HuaProP3已正式面世。这款产品的推出,标志着芯华章在FPGA验证威廉希尔官方网站

上的又一次重大突破,也是其在数字验证EDA全流程工具链研发领域的又一重要里程碑。 自2020年成立以来,芯华章始终专注于数字验证EDA全流程工具链的研发工作,致力于为客户提供高效、可靠的解决方案。在过去的时间里,芯华章凭借深厚的威廉希尔官方网站

积累和不断创新的精神,成功在EDA领域取

- 专栏科技绿洲

- 9天前

- 304

- 0

- 0

如何在8位MCU中集成可编程逻辑

在半导体领域,微控制器(MCU)是一个很卷的赛道。为了能够从众多竞争者中脱颖而出,MCU产品一直在不断添加新“技能”,以适应市场环境的新要求。因此,时至今日,如果你“打开”一颗MCU,会发现其早已不再是一颗传统意义上简单的计算和控制芯片,而是集成了CPU内核以及丰富外设功能模块的SoC。

- 专栏贸泽电子

- 11天前

- 273

- 0

- 0

ED6H系列FPGA口袋实验室

01.产品概述ED6H系列FPGA口袋实验室是中科亿海微自主研发的基于“FPGA在线教学平台”的教学实践工具,专为高校电子相关专业师生打造,旨在为高校师生创造更具创新性与高效性的教学场景。具有高集成度、小巧便携、可扩展设计及自主可控等特点。本系列共推出三款产品,均搭载亿海神针系列FPGA芯片,可覆盖差异化需求,集成大量数字电路、信号处理等实验所需的核心接口及

- 企业中科亿海微

- 18天前

- 253

- 0

- 0

易灵思FPGA产品的主要特点

近年来,全球半导体供应链屡受挑战,芯片短缺问题一度对行业产生深远影响。易灵思通过优化供应链管理、强化产能规划,确保客户的FPGA需求得到及时满足。面向工业控制、机器视觉、医疗影像、消费电子、汽车智驾等一众终端领域,易灵思始终与客户并肩同行,确保产品准时交付。

- 专栏易灵思官微

- 18天前

- 375

- 0

- 0

原programmer烧写用户数据到flash-v1

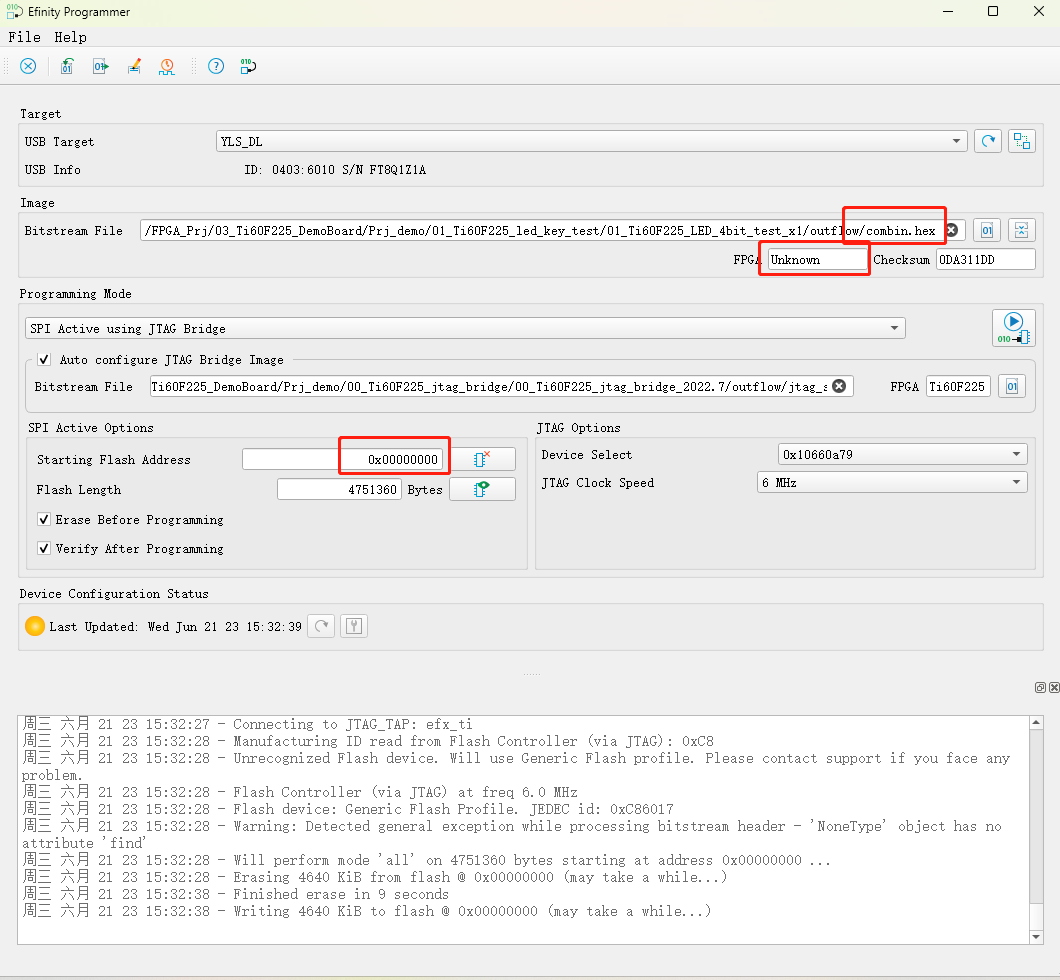

今天有客户提出怎样把用户数据写入到flash的操作,本来以为写的programmer都不支持了,但是经过多次验证发现还是可以的,可能之前的验证哪里有点问题吧。 一、通过SPI Active或者SPI Active using JTAG Bridge方式。 如下图,和正常通过 SPI Active using JTAG Bridge配置 程序一样的,只是我们看到FPGA显示的是unKnown。另外在下面的starting Flash Address位置指定flash的写入地址。 二、与程序合成。 选择combine Multiple Image Files。打开combine Multiple Image Files对话框。 点击右

- 专栏XL FPGA威廉希尔官方网站 交流

- 24天前

- 790

- 0

- 0

TI 的 PLD 可将总体电路板空间减少 90% 或更多,同时元件数量也至少减少 80%

Russell Crane 我们常说逻辑器件是每个电子产品设计的“粘合剂”,但在为系统选择元件时,它们通常是您最后考虑的部分。确实有很多经过验证的标准逻辑器件可供选择。但是,随着设计变得越来越复杂,我们需要在电路板上集成逻辑元件,以便为更多功能留出空间。 越来越多的工程师选择可编程逻辑器件 (PLD)、复杂 PLD (CPLD) 或现场可编程门阵列 (FPGA),从而帮助减小解决方案尺寸、降低设计和制造成本、管理其供应链,并缩短产品上市时间。在使用

- 专栏eeDesigner

- 27天前

- 422

- 0

- 0

后摩尔时代的创新:在米尔FPGA上实现Tiny YOLO V4,助力AIoT应用

学习如何在MYIR的ZU3EGFPGA开发板上部署TinyYOLOv4,对比FPGA、GPU、CPU的性能,助力AIoT边缘计算应用。(文末有彩蛋)一、为什么选择FPGA:应对7nm制程与AI限制在全球半导体制程限制和高端GPU受限的大环境下,FPGA成为了中国企业发展的重要路径之一。它可支持灵活的AIoT应用,其灵活性与可编程性使其可以在国内成熟的28nm

- 企业米尔电子

- 1月前

- 688

- 0

- 1

AMD推出了Versal Premium Series Gen 2,这是业界第一个支持CXL 3.1和PCIe Gen6的FPGA平台。

AMD推出了Versal Premium Series Gen 2,这是业界第一个支持CXL 3.1和PCIe Gen6的FPGA平台。 AMD为数据中心、航空航天、通信和T M市场设计了Versal Premium系列Gen 2。 随着人工智能和数据分析的加强,这些威廉希尔官方网站

背后的基础设施必须跟上繁重的数据需求。数据中心互连系统的兴起提升了FPGA在处理复杂任务中的作用。随着内存可扩展性和安全性的进步,AMD推出了可扩展的Versal Premium Series Gen 2,以满足依赖快速、安全数据流的行业的需求。 所有关于电路与迈克,AMD的高级产

- 专栏eeDesigner

- 1月前

- 431

- 0

- 0

多平台FPGA工程快速移植与构建

作为一名FPGA工程师,经常需要在多个FPGA设备之间移植项目,核心的问题是IP的管理和移植,今天通过安装和使用 FuseSoC 在多个 AMD FPGA 之间移植一个简单的项目。从 AMD Spartan 7 更改为 AMD Artix 7 设备,然后是 AMD Kintex UltraSacle。

- 专栏FPGA威廉希尔官方网站 江湖

- 1月前

- 815

- 0

- 0

Microchip PolarFire® FPGA以太网传感器桥与NVIDIA Holoscan传感器处理平台兼容的人工智能(AI)驱动的传感器处理系统

Microchip Technology推出了PolarFire® FPGA以太网传感器桥,以帮助开发人员创建与NVIDIA Holoscan传感器处理平台兼容的人工智能(AI)驱动的传感器处理系统。 PolarFire FPGA使得多种协议能够协同工作。基于Microchip平台的第一个解决方案与MIPI® CSI-2®传感器和MIPI D-PHY物理层兼容。未来的解决方案将支持具有各种接口的多样化传感器,包括SLVS-EC™ 2.0、12G SDI、CoaXPress® 2.0和JESD204B。该平台使设计者能够在使用NVIDIA Holoscan生态系统特性的同时,还能够利用PolarFire FPGA的节

- 专栏eeDesigner

- 1月前

- 528

- 0

- 0

浅析FPGA的重要用途

FPGA 允许在单个芯片中实现大量数字逻辑,其运行速度相对较高,并且只需很少或不需要在 CPU 内核上运行的传统顺序程序即可完成其工作。

- 专栏FPGA研究院

- 1月前

- 1230

- 0

- 1

易灵思钛金系列加密方案-V1

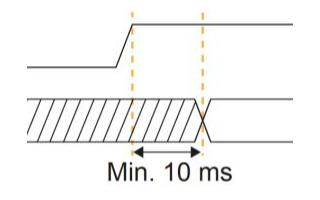

硬件设计要求 在之前的版本中,加密是通过VCC_AUX来供电的。在新的版本中已经通过单独的VQPS管脚来供电来实现。 对于Ti35/Ti60F225,VQPS供电管脚是G6, 对于 Ti35/Ti60F100S3F2,VQPS供电管脚是 A5,这两个脚在之前的版本中都直接接地的。所以对于新设置的硬件或者改版的硬件,如果要使用加密功能就需要注意。 如果需要烧写密钥,可以单独给VQPS供1.8V的电源,VQPS的供电波形如下。可以考虑把VQPS拉到一个排针上或者座子上,烧写密钥时就给VQPS供电1.8V,烧写完

- 专栏XL FPGA威廉希尔官方网站 交流

- 1月前

- 832

- 0

- 0

原方案尺寸缩小94%,数分钟完成原型设计,TI全新PLD让功能开发如此简单

电子发烧友网报道(文/吴子鹏)可编程逻辑器件(PLD,programmable logic device)是一种灵活性很高的器件,内部集成有可编程的逻辑门、时钟资源和互连结构,具有开发周期短、灵活性高、集成度高等优点。在实际开发应用中,工程师可以根据项目需要进行编程和配置,以实现特定的逻辑功能,因此PLD广泛应用于数字逻辑设计、嵌入式系统、通信、工业自动化和消费电子等领域。 不过,目前市场上大部分PLD都有一定的门槛,主要体现在两个方面:其一是

- 专栏Felix分析

- 1月前

- 2979

- 0

- 0

详解FPGA的基本结构

ZYNQ PL 部分等价于 Xilinx 7 系列 FPGA,因此我们将首先介绍 FPGA 的架构。简化的 FPGA 基本结构由 6 部分组成,分别为可编程输入/输出单元、基本可编程逻辑单元、嵌入式块RAM、丰富的布线资源、底层嵌入功能单元和内嵌专用硬核等。

- 专栏Hack电子

- 1月前

- 1053

- 0

- 0

FPGA无芯片怎么进行HDMI信号输入

FPGA 在无外部PHY芯片情况下输出HDMI,目前是比较成熟的方案(外部电路需要转换成TMDS电平)。在无PHY芯片情况下怎么进行HDMI信号输入呢?

- 专栏FPGA威廉希尔官方网站 江湖

- 1月前

- 1314

- 0

- 0

易灵思Efinity入门使用-v8

Step1:点击设置

Step2:在Top level project path中输入路径

Step3:点击File -> Open Project,路径会指向step2中设置的路径

- 专栏XL FPGA威廉希尔官方网站 交流

- 2月前

- 914

- 0

- 0

FPGA软件Efinity入门使用-v7

一、 软件预设置 二、新建工程 三、添加源文件 四、添加管脚约束 五、添加GPIO 六、 PLL设置 七、IPM添加IP 八、 添加debug 九、下载 十、仿真 十一、查看软件版本 一、软件预设置。 选项 说明 User editor 一般软件自带的编辑器功能有限,而外部编辑器功能要强大很多。所以建议大家使用外部编辑器。在User editor中输入编辑器的路径。 Use user editor as default editor for all files。 如果希望每次点击文件时是通过外部编辑器打开的,可以勾选Use user editor as

- 专栏XL FPGA威廉希尔官方网站 交流

- 2月前

- 830

- 0

- 0

原Efinity FIFO IP仿真问题 -v1

Efinity目前不支持联合仿真,只能通过调用源文件仿真。 我们生成一个fifo IP命名为fifo_sim 在Deliverables中保留Testbench的选项。 在IP的生成目录下会有以下几个文件 我们来看下modelsim.do文件,里面vlog了fifo_tb.sv文件,另外还调用了flist文件里的文件,flist只有一个文件那就是fifo_sim.v。所以这个仿真只使用了两个文件。 如果生成默认的IP或者自己的IP,目前FIFO的IP仿真可能会有一个错误 。提示在fifo_tb.sv的409行没有rd_valid_o和almost_empty_o 这是因为仿真文件只能仿真

- 专栏XL FPGA威廉希尔官方网站 交流

- 2月前

- 990

- 0

- 0