多谐振荡器是连续逻辑电路,可在两种不同的HIGH和LOW状态之间连续工作

单个顺序逻辑电路可用于构建更复杂的电路,如多谐振荡器,计数器,移位寄存器,锁存器和存储器。

但是对于这些类型的电路以“顺序”方式工作,它们需要添加时钟脉冲或定时信号以使它们改变它们的状态。州。时钟脉冲通常是连续的方形或矩形波形,由单个脉冲发生器电路(如多谐振荡器)产生。

A 多谐振荡器电路之间振荡“高”状态和“低”状态产生连续输出。稳定的多谐振荡器通常具有甚至50%的占空比,即输出为“高”的循环时间的50%和输出为“关闭”的剩余50%的循环时间。换句话说,非稳态定时脉冲的占空比为1:1。

使用时钟信号进行同步的顺序逻辑电路取决于频率和时钟脉冲宽度,以激活切换动作。顺序电路也可以在上升沿或下降沿或两个实际时钟信号上改变它们的状态,正如我们之前在基本触发器电路中看到的那样。以下列表是与定时脉冲或波形相关的术语。

时钟信号波形

高电平有效 - 如果状态在时钟的脉冲上升沿或时钟宽度从“低电平”变为“高电平”。

低电平有效 - 如果状态变化在时钟的脉冲下降沿从“高”变为“低”。

占空比 - 这是时钟宽度与时钟周期的比率。

时钟宽度 - 这是时间在此期间,时钟信号的值等于逻辑“1”或HIGH。

时钟周期 - 这是连续转换之间的时间。相同的方向,即两个上升沿或两个下降沿之间。

时钟频率 - 时钟频率是时钟周期的倒数,频率= 1 /时钟pe荒漠化问题。 (ƒ= 1 / T)

时钟脉冲发生电路可以是interwetten与威廉的赔率体系 和数字电路的组合,产生连续的脉冲序列(这些称为非稳态多谐振荡器)或脉冲具体持续时间(这些被称为单稳态多谐振荡器)。组合两个或多个多谐振荡器可产生所需的脉冲模式(包括脉冲宽度,脉冲之间的时间和脉冲频率)。

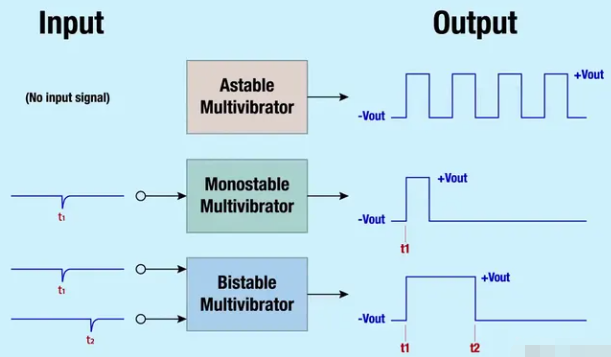

基本上有三种类型的时钟脉冲发生电路:

Astable -A 自由运行多谐振荡器NO稳定状态但是在两个状态之间连续切换,此动作以固定频率产生一系列方波脉冲。

单稳态 -A 单次多谐振荡器

只有 ONE 稳定状态,并在外部触发,返回其第一个稳定状态。

双稳态 - 触发器具有两个稳定状态,产生单个脉冲的正值或负值。

一种生产方式一个非常简单的时钟信号是通过逻辑门的互连。由于 NAND 门包含放大,它们还可以借助单个电容和单个电阻提供时钟信号或定时脉冲,以提供反馈和定时功能。

这些定时电路经常被使用,因为它很简单,并且如果逻辑电路被设计成具有未使用的门,可用于产生单稳态或非稳态振荡器,也是有用的。这种简单类型的 RC 振荡器网络有时称为“弛豫振荡器”。

单稳态多谐振荡器电路

单稳态多谐振荡器或“单次”脉冲发生器通常用于将短尖脉冲转换为更宽的脉冲以用于定时应用。当施加合适的外部触发信号或脉冲 T 时,单稳态多谐振荡器产生单个输出脉冲,“高”或“低”。

此触发脉冲信号启动定时循环导致单稳态的输出在定时周期开始时改变状态( t 1 )并保持在第二状态,直到定时周期结束,( t 2 )由定时电容的时间常数 C T 和电阻确定, R T

单稳态多谐振荡器现在保持在第二个定时状态,直到RC时间常数结束并自动复位或返回自身到其原始(稳定)状态。然后,单稳态电路仅具有一个稳定状态。这种类型电路的一个更常见的名称就是“触发器”,因为它可以由两个交叉耦合的 NAND 门(或 NOR 门)制成,因为我们以前见过。考虑下面的电路。

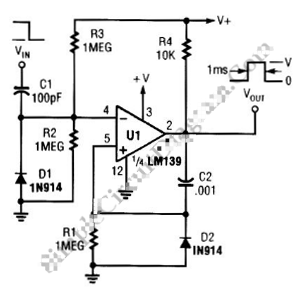

简单的NAND门单稳电路

假设最初是触发输入 T 通过电阻 R 1 保持在逻辑电平“1”为高电平,以便第一个 NAND <的输出/ span> gate U1 在逻辑电平“0”为低电平时,(与非门控原理)。定时电阻 R T 连接到等于逻辑电平“0”的电压电平,这将导致电容 C T 待出院。 U1 的输出为低电平,定时电容 C T 完全放电,因此结 V1 也等于“ 0“导致第二个 NAND 门 U2 的输出,它作为反相 NOT 门连接,因此将为高电平。

第二个 NAND 门的输出( U2 )反馈到 U1 的一个输入,以提供必要的正反馈。由于结 V1 且 U1 的输出均为逻辑“0”,因此电容器中没有电流流过 C T 。这导致电路稳定并且它将保持此状态,直到触发输入 T 发生变化。

如果现在施加负脉冲在外部或通过按钮对 NAND 门 U1 的触发输入的操作, U1 的输出将变为HIGH到逻辑“1”(与非门原理)。

由于电容两端的电压不能瞬间改变(电容充电原理),这将导致 V1 处的结点以及 U2 也变为高电平,这反过来将使 NAND 门 U2 的输出变为低电平为逻辑“0”电路现在将保持不变即使触发输入脉冲 T 被移除,也处于第二状态。这被称为元稳定状态。

当电容 C T 从电阻/电容组合确定的时间常数开始从 U1 的输出充电。此充电过程一直持续到充电电流无法保持输入 U2 ,因此结 V1 HIGH。

当发生这种情况时,输出 U2 再次变为高电平,逻辑“1”,进而导致 U1 的输出变为低电平,电容放电到 U1 在电阻 R T 的影响下。该电路现已切换回其原始稳定状态。

因此,对于每个负向触发脉冲,单稳态多谐振荡器电路产生低电平输出脉冲。输出时间周期的长度由电容器/电阻器组合(RC网络)决定,并以秒为单位给出电路的时间常数T = 0.69RC 。由于 NAND 门的输入阻抗非常高,因此可以实现大的时序周期。

以及上面的 NAND 门单稳态电路,还可以构建简单的单稳态定时电路,使用 NOT 门, NAND 门和 NOR从触发脉冲的上升沿开始其时序门连接为逆变器,如下所示。

NOT门单稳态多谐振荡器

与上面的 NAND 门电路一样,最初触发输入 T 在逻辑电平“1”时为高电平,因此第一个 NOT <的输出/ span> gate U1 在逻辑电平“0”时为低电平。定时电阻 R T 和电容 C T 并联连接在一起,也连接到输入端第二个 NOT 门 U2 。由于 U2 的输入在逻辑“0”为低电平时, Q 的输出在逻辑“1”时为高电平。

当逻辑电平为“ 0“脉冲施加到第一个 NOT 门的触发输入 T ,它改变状态并产生逻辑电平”1“输出。二极管 D1 将此逻辑“1”电压电平传递给 RC 时序网络。电容两端的电压 C T 迅速增加到这个新的电压电平,该电压电平也连接到第二个 NOT 门的输入端。这反过来在 Q 处输出逻辑“0”,并且只要应用了触发输入 T ,电路就会保持在Meta-stable状态电路保持低电平。

当触发信号返回高电平时,第一个 NOT 门的输出变为低电平为逻辑“0”(非门控原理)并且充满电电容, C T 开始通过并联电阻放电, R T 连接在它上面。当电容两端的电压降至低于第二个 NOT 门输入的下限阈值时,其输出再次切换回来,在 Q 处产生逻辑电平“1”。二极管 D1 可防止定时电容通过第一个 NOT 门输出自行放电。

然后,时间常数对于 NOT 门单稳态多谐振荡器以秒为单位给出 T = 0.8RC +触发。

一个主要缺点单稳态多谐振荡器的意思是,施加下一个触发脉冲 T 之间的时间必须大于电路的 RC 时间常数。

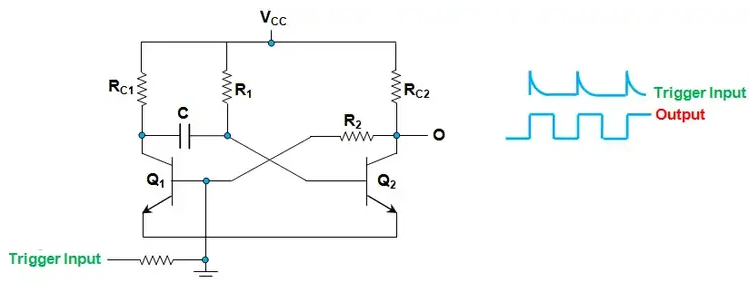

Astable多谐振荡器电路

Astable Multivibrators是最常用的多谐振荡器电路类型。非稳态多谐振荡器是一种自由运行的振荡器,它没有永久的“元”或“稳定”状态,但不断地将输出从一个状态(低)改变到另一个状态(高),然后再返回。这种从“高”到“低”和“低”到“高”的连续切换动作产生连续稳定的方波输出,在两个逻辑电平之间突然切换,使其成为时序和时钟脉冲应用的理想选择。

与上述单稳态多谐振荡器电路一样,时序周期由电阻 - 电容RC网络的RC时间常数决定。然后可以通过改变电路中电阻器和电容器的值来改变输出频率。

NAND门稳压多谐振荡器

>

非稳态多谐振荡器电路使用两个CMOS NOT 门,例如CD4069或74HC04十六进制反相器IC,或者像我们的简单电路中的一对CMOS NAND ,例如CD4011或74LS132和 RC 时序网络。两个 NAND 门连接为反相 NOT 门。

假设最初 NAND 门的输出 U2 在逻辑电平“1”时为高电平,因此输入必须为逻辑电平“0”(与非门原理)的低电平,因为第一个 NAND 门的输出<跨度> U1 。电容 C 连接在第二个 NAND 门 U2 的输出端,其输入端通过定时电阻 R 连接2 。电容现在以 R 2 和 C 的时间常数确定的速率充电。

作为电容器, C 充电,电阻 R 2 与电容 C 之间的连接,也连接通过稳定电阻到 NAND 门 U1 的输入端, R 2 减小,直至下限阈值为到达 U1 此时 U1 改变状态, U1 的输出现在变为HIGH。这导致 NAND 门 U2 也改变状态,因为其输入现在已从逻辑“0”变为逻辑“1”,从而导致 NAND的输出 gate U2 变为低电平,逻辑电平为“0”。

电容 C 现在反向偏置,并通过的输入放电NAND 门 U1 。电容, C 再次向相反方向充电,由 R 2 和 C 的时间常数确定为之前,直到达到 NAND 门 U1 的上限阈值。这会导致 U1 改变状态,并且循环重复自身。

然后, NAND 门的时间常数Astable Multivibrator以秒为单位给出 T = 2.2RC ,输出频率为ƒ= 1 / T 。

例如:如果电阻 R 2 =10kΩ且电容 C = 45nF ,电路的振荡频率如下:

然后输出频率计算为 1kHz ,相当于的时间常数1ms 所以输出波形看起来像:

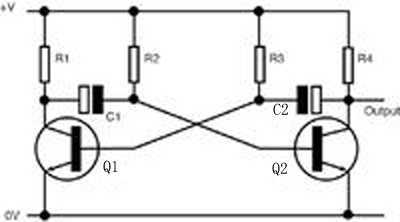

双稳态多谐振荡器电路

双稳态多谐振荡器电路基本上是一个SR触发器,我们在之前的教程中看到了增加一个逆变器或 NOT 门提供必要的切换功能。与触发器一样,双稳态多谐振荡器的两种状态都是稳定的,并且电路将无限期地保持在任一状态。当施加合适的外部触发脉冲 T 并且经过完整的“SET-RESET”循环时,这种类型的多谐振荡器电路从“仅”状态传递到另一个状态2需要触发脉冲。这种类型的电路也称为“双稳态锁存器”,“切换锁存器”或简称为“T锁存器”。

NAND门双稳态多谐振荡器

制作双稳态锁存器的最简单方法是将一对施密特 NAND 门连接在一起形成SR锁存器如上图所示。两个 NAND 门, U2 和 U3 构成双稳态,由输入 NAND 门触发, U1 。这个 U1 NAND 门可以省略,并用一个切换开关代替,以制作一个开关去抖电路,如之前在SR触发器教程中所见。

当输入脉冲变为“低”时,双稳态锁存到其“SET”状态,其输出处于逻辑电平“1”,直到输入变为“高”,导致双稳态锁存到其“复位”状态,其输出为逻辑电平“0”。双稳态多谐振荡器的输出将保持在“RESET”状态,直到施加另一个输入脉冲并且整个序列将再次开始。

然后双稳态锁存器或“切换锁存器” “是一种双态器件,其中正状态或负状态(逻辑”1“或逻辑”0“)都是稳定的。

双稳态多谐振荡器有许多应用,如作为分频器,计数器或计算机存储器中的存储设备,但它们最适用于锁存器和计数器等电路。

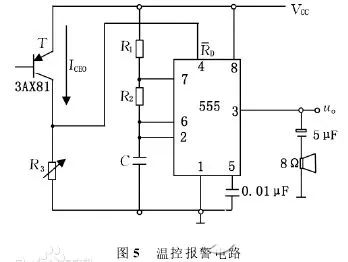

555定时器电路。

现在可以使用标准常用波形发生器IC专门设计简单的单稳态或稳定多谐振荡器,以创建定时和振荡器电路。松弛振荡器可以简单地通过将几个无源元件连接到它们的输入引脚来构建,最常用的波形发生器类型IC是经典的555定时器。

555定时器是一个非常通用的低成本定时IC,可以产生非常精确的定时周期,具有约1%的良好稳定性,并且具有从几微秒到几小时之间的可变定时周期,定时周期由连接的单个RC网络控制单个正电源电压介于4.5和16伏之间。

NE555定时器及其后继产品ICM7555,CMOS LM1455,DUAL NE556等都包含在555振荡器教程和其他基于电子设备的好网站中,所以这里仅包括作为时钟脉冲发生器的参考。作为Astable Multivibrator连接的555如下所示。

NE555 Astable Multivibrator

这里555定时器作为基本的Astable Multivibrator连接,产生连续的输出波形。引脚2和6连接在一起,以便它在每个定时周期重新触发,从而起到Astable振荡器的作用。电容, C1 通过电阻器充电, R1 和电阻器 R2 ,但仅通过电阻器 R2 放电 R2 的另一端连接到 discharge 端子,引脚7.然后 t 1 的定时周期和 t 2 的给出如下:

t 1 = 0.693( [R <子> 1 + R <子> 2 )C <子> 1

<跨度>吨<子> 2 = 0.693(R <子> 2 )C <子> 1

<跨度> T =吨<子> 1 + t 2 = 0.693(R 1 + 2R 2 )C 1

电容两端的电压 C1 的范围为1/3 Vcc至约2/3 Vcc,具体取决于RC定时周期。这种类型的电路非常稳定,因为它采用单电源供电,导致振荡频率与电源电压Vcc无关。

在下一篇关于时序逻辑电路的教程中,我们将看另一种称为数据锁存器的时钟控制触发器。数据锁存器是非常有用的时序电路,可以由任何标准门控SR触发器制成,并用于分频,以产生各种纹波计数器,分频器和锁存器。

-

电路

+关注

关注

172文章

5905浏览量

172155 -

逆变器

+关注

关注

283文章

4715浏览量

206715 -

多谐振荡器

+关注

关注

14文章

207浏览量

37749

发布评论请先 登录

相关推荐

多谐振荡器的基本特性和主要参数

无稳态多谐振荡器电路工作原理是什么

多谐振荡器的工作原理、分类、设计方法和应用

多谐振荡器的特点和应用

单稳态多谐振荡器电路图分享

不同多谐振荡器电路及信号波形

不同多谐振荡器电路及信号波形

评论