本课程前期是基础理论的讲解,后期是结合经验和项目实践提炼的主要内容,围绕抗干扰和工程实现进行原理阐述,省去了复杂的公式推导过程,和大家分享硬件学习经验。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1629文章

21754浏览量

604231 -

程序

+关注

关注

117文章

3791浏览量

81156 -

时序

+关注

关注

5文章

389浏览量

37356

发布评论请先 登录

相关推荐

编制PLC程序的逻辑错误

在编制PLC程序时,不管是新手还是老手,都会犯下面的这种低级错误。因为这种错误是非语法上的,所以用编程软件也不能检查出错误之处。此错误一旦发

发表于 09-19 11:28

•625次阅读

使用SDK5生成工程模板程序时老是出现错误是为啥?

使用st SDK5生成工程模板程序时老是出现这样的错误是为啥?我的SDK:5.0.1STM32CubeMX:4.26.0Keil5:5.25

求助万能的网友。

发表于 04-28 08:36

FPGA重要设计思想及工程应用之时序及同

FPGA重要设计思想及工程应用之时序及同

在FPGA设计中最好的时钟方案 是: 由专用的全局时钟输入引脚 动单个 主时钟去控制设计项目中的每一个触发 器

发表于 02-09 10:29

•51次下载

FPGA设计:时序是关键

当你的FPGA设计不能满足时序要求时,原因也许并不明显。解决方案不仅仅依赖于使用FPGA的实现工具来优化设计从而满足时序要求,也需要设计者具有明确目标和诊断/隔离

发表于 08-15 14:22

•1279次阅读

FPGA中的时序约束设计

一个好的FPGA设计一定是包含两个层面:良好的代码风格和合理的约束。时序约束作为FPGA设计中不可或缺的一部分,已发挥着越来越重要的作用。毋庸置疑,时序约束的最终目的是实现

发表于 11-17 07:54

•2575次阅读

FPGA程序时序错误对雷达抗干扰的影响

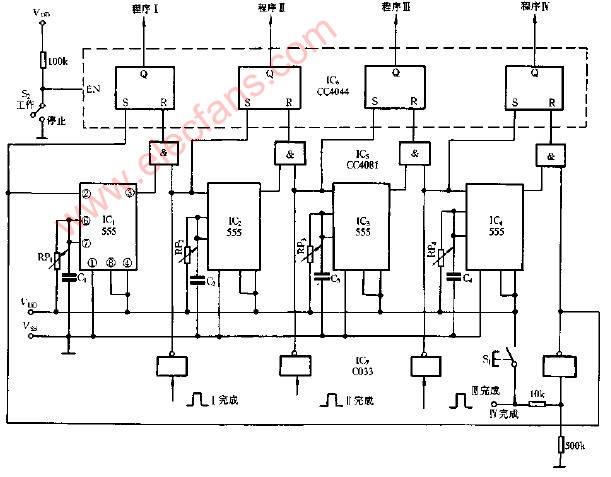

时序约束主要包括周期约束(FFS到FFS,即触发器到触发器)和偏移约束(IPAD到FFS、FFS到OPAD)以及静态路径约束(IPAD到OPAD)等3种。通过附加约束条件可以使综合布线工具调整映射和布局布线过程,使设计达到时序要求。

发表于 12-05 09:39

•1773次阅读

FPGA时序约束:如何查看具体错误的时序路径

1、时序错误的影响 一个设计的时序报告中,design run 时序有红色,裕量(slack)为负数时,表示时序约束出现

编制PLC程序时容易犯错的低级错误

继电器电气控制的固有思维,在编制程序时,某个或几个输入点采用物理常闭触点(如停止开关、行程限位开关),在程序中,仍延续继电器电气控制方式编制,即仍采用常闭接点作为导通条件使用。

发表于 06-26 11:42

•474次阅读

应用程序中的服务器错误怎么解决?

在使用应用程序时,可能会遇到服务器错误的问题。这种错误通常会导致应用程序无法正常运行 ,给用户带来不便。下面将介绍应用程序中的服务器

FPGA程序时序错误对工程的影响

FPGA程序时序错误对工程的影响

评论