顾名思义,EMC就是关于如何解决电子设备如何对其他设备产生干扰、或防止外部设备对自身电子设备产生电磁场干扰的问题。在PCB布线设计中,特别是高速电路设计,您必须得考虑电路的电磁兼容,不然的话,您的产品很可能通不过3C标准。

今天我们就来讲讲电磁兼容(EMC)在PCB布线设计中,需要注意哪些具体设计细节,注意哪些问题。从大体上来讲 ,PCB电磁兼容的设计,要对以下这几类电路布线重点关注。

1.强辐射信号线(高频、高速、时钟走线为代表)2.敏感信号(如复位信号)3.功率电源信号4.接口信号(interwetten与威廉的赔率体系 接口或数字通信接口)

下面,我们针对普遍的PCB电路和高速电路PCB电磁兼容设计,详细列举一二。

一、电磁兼容在低速信号的PCB设计问题

低速电路PCB设计中,我们需要考虑如下几点要素:

1、电源走线策略

对于电源来说,任何板都要遵循此规则。每个芯片电源管脚必须放置0.1uF的电容。这样能滤除芯片电源高速干扰。对于不铺铜,而是直接走粗线的,每隔3000mil必须加电容(10uF+0.1uF)。这样高频噪声会滤除。

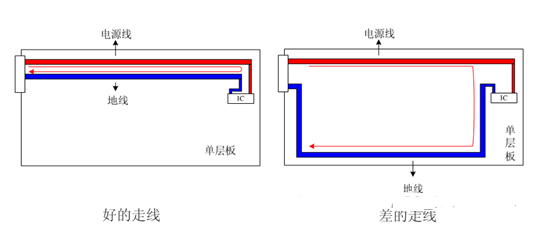

单层板的话,电源与地必须紧挨着走线,以减少回流环路面积。如下图

2、敏感信号的走线策略

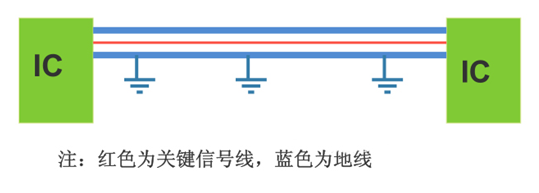

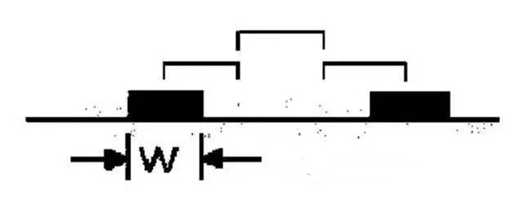

对于敏感信号最好是要用地包住。这样包地即提供了信吃最短回流路径,也能消除与其它相邻信号的干扰。如下图

如果是多层板,对于特别敏感的信号线除了同层用包地处理,还可以上,下两层也是大面积的铺地。这样,使信号的上,下,左,右都有地包着。保证信号的干净。

3、信号的回流面积最小定律

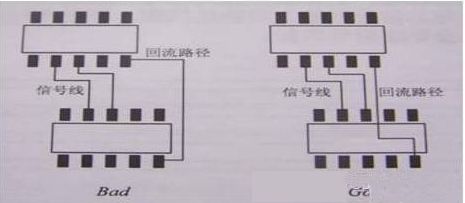

在PCB设计中,每根信号最好能做到与地的回流路径最短,如下图所示

回路面积最小,信号的抗干扰能力加强,对外的EMI也达到最小。单双面的话,只能使地回路尽可能的短。本文微信公众号: PCB_technique。对于多层板,就要在相邻层铺上大面积的铜作为地。这个铺大面积的铜的相邻层,也叫信号的参考层。做阻抗设计时,就是以这个参考层来计算阻抗大小的。

4、PCB的走线方式

PCB走线不能走直角,一般走45度角。高速信号最好走圆弧。超高速信号10度走线。走线宽度要一致,不然会产生阻抗不连续。对于高速信号就会产生不必要的反射,振铃。

5、相邻层的布线策略

相邻层走线时,最好是形成垂直。一层是平行走线,那相邻层就要垂直走线。这样相邻层的信号不会形成干扰。实在无法避免,就适当减小平行走线线段的长度。最好小于1000mil

6、在电源线中过孔的个数

在布电源线时,在不同层连接用到过孔时,必须考虑良好连接性。如果电流大,由于过孔的电阻性,放一个过孔可能会降低到终端的电压。导致到芯片电源脚的电压低于实际设计的电压,而使芯片不能工作。这时我们在换层连接处多加几个过孔。

7、电容的放置及布线

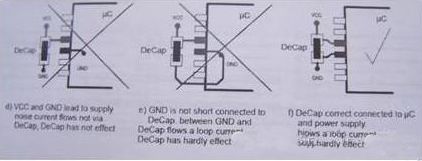

滤波电容在放置时,如第1条所说,要靠近芯片管脚放置,布线要尽可能的粗,短。保证滤高频效果。电容接地脚要就近打孔到地层。不能连一根很长的线再跟地相连。如下图所示

二、电磁兼容在高速信号的PCB设计问题

1、3W与20H法则

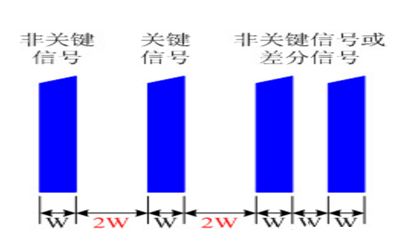

3W就是信号线之间的布线间距是线宽的两倍,中心距是3倍。如图所示:

3W的线间距,可以保证不受其它干扰信号的电场达到70%以上,如要达到98%的电场不互相干扰,就要使用10W的间距。

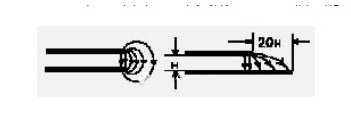

20H是指多层板电源平面要比地平面边缘缩进两个平面之间间距的20倍以上。这样,电源被地包围在地平面之内,大减小了向外辐射的机率。如下图所示:

2、高速信号的走线层次选择

高速信号线最好是走在里层,这样介质层起到屏蔽作用,能有效抑制EMI信号的向外辐射。

3、高带关键信号包地处理

高速信号线中如时钟钱,最好采用包地处理,而且包地每隔3000mil打一个过孔连接到地层。关键信号与其它线之间要满足3W规则。如下图所示:

-

pcb

+关注

关注

4319文章

23099浏览量

397923 -

电磁

+关注

关注

15文章

1133浏览量

51819

原文标题:高速PCB设计中考虑EMC,您不得不知道的布线技巧(附完整EMC学习大礼包)

文章出处:【微信号:elecfans,微信公众号:电子发烧友网】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

高速PCB设计中考虑EMC的布线技巧

高速PCB设计中考虑EMC的布线技巧

评论