声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

芯片

+关注

关注

455文章

50812浏览量

423574 -

ADI

+关注

关注

146文章

45821浏览量

249953 -

安全

+关注

关注

1文章

340浏览量

35703

发布评论请先 登录

相关推荐

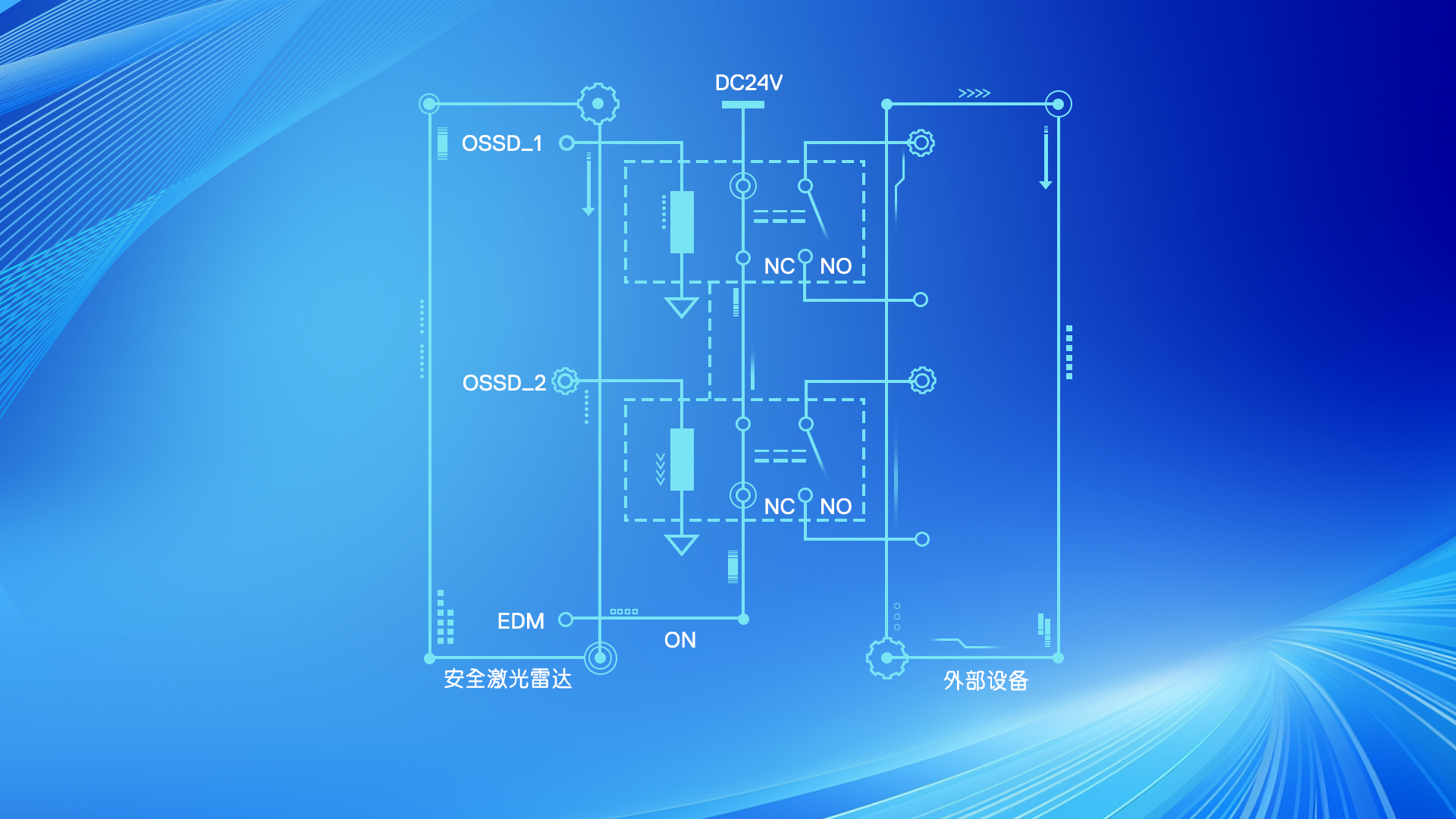

产品介绍 满足功能安全认证要求:SIL 2安全防护型激光雷达GS1-5

的SIL 2、PL d、Type 3 权威认证, 表明产品符合 IEC 61508、IEC 62061、ISO13849 和 IEC 61496 标准的要求。 2D 270° 功能安

两片AD7124的spi可以并在一起吗,分别片选。

两片AD7124-8 芯片的spi接口能够并联在一起吗?使用两个GPIO引脚做片选信号,目前这样设计的,一片芯片的CS引脚已经强制拉高了,另外一篇读回来全部是0。不知道是电路本身有问题,还是不能这样设计

发表于 09-21 18:03

应用案例分享 | 智驾路试数据分析及 SiL/HiL 回灌案例介绍

本文将通过实际应用案例进行讲解,通过软件在环(SiL)和硬件在环(HiL)回灌验证,该系统能够充分评估和优化算法性能,发挥数据价值。

具有集成电源的低辐射信号隔离器可满足CISPR 32要求

电子发烧友网站提供《具有集成电源的低辐射信号隔离器可满足CISPR 32要求.pdf》资料免费下载

发表于 09-07 11:28

•0次下载

南京恒立获TÜV南德SIL 2/PL d功能安全认证

南京恒立智能威廉希尔官方网站

有限公司近日迎来重大喜讯,其主体采用Cat.3架构的安全控制器HLEC-C3-7053成功获得TÜV南德意志集团颁发的功能安全证书。该证书基于国际权威标准IEC 61508(SIL

AD7124-8按照19200输出速率设置,实际五千不到怎么解决?

AD7124-8 直接说设置,

{0x01, 0x04C0, 2, 1}, 全功率,状态和数据一起传输

{0x09, AD7124_CH_EN |AD7124

发表于 08-01 07:12

AD7124的程序如何将它导出成hex格式呢?

/platforms/SDP_K1/这个等。它的程序我也在网上下载下来了。参见附件。

EVAL-AD7124-3e1005bd4d41.zip

打开后是这样的,

我的问题是,如果这个文件确实是用于AD7124的程序

发表于 07-23 08:13

AD7124-8手册里没提到上电时序,评估板原理图是有上电时序的,那电路设计时是否需要上电时序?

AD7124评估板中的AVDD先上电,而后IOVDD才上电。但数据手册中没有体现,实际设计电路时候是否需要这样设计呢?

还有一个问题,这里为啥中等功率模式的均方根值噪声明明小于全功率模式,为啥它

发表于 07-04 08:31

AD7124-8内部温度传感器如何读取,通道配置如何设置呢?

] - 0x800000) * 10 / 13584 - 2725; //读AD7124内部温度,精度0.5°C

发现温度比芯片表面温度总是低了1.5°C左右,我哪里做错了,请告诉我正常的设置,多谢!

发表于 07-04 06:52

该如何提高代码容错率、降低代码耦合度?

提高RT-Thread代码的容错率和降低耦合度是确保代码质量和可维护性的关键,下面列举了几种在编写代码时,提高代码容错率和降低耦合度的思路。让我们一起来看看吧~一、提高代码容错率输入验证与数据校验

TIDA-010049-适用于 IEC 61508 (SIL-2) 且经TUV评估的数字输入PCB layout 设计

电子发烧友网站提供《TIDA-010049-适用于 IEC 61508 (SIL-2) 且经TUV评估的数字输入PCB layout 设计.pdf》资料免费下载

发表于 05-13 14:19

•1次下载

容错can和高速can的区别

容错CAN(Controller Area Network)和高速CAN是两种常见的汽车通信协议,它们在速度和可靠性方面有所不同。以下是关于容错CAN和高速CAN的详尽、详实和细致的1500字

可满足SIL2对硬件容错要求的AD7124芯片

可满足SIL2对硬件容错要求的AD7124芯片

评论