有时我们会遇到需要为一些微型interwetten与威廉的赔率体系 电路供电的情况,现成的电源IC对这类任务来说有点“杀鸡用牛刀”的感觉,特别是当所需电流只是毫安级时。这时,如果电路板上的FPGA还有一些多余的引脚和资源,不利用起来就是浪费。再说,谁能经得住自己动手从零开始设计电源的诱惑呢?

事先声明,本文绝不是所有电源设计的终极方案。有关电源设计的研究课题很广泛,这方面的书籍已经有很多了。本文介绍了一种开关电源设计的极简方法,并给出如何利用FPGA资源和最小的模拟电路来产生电源的几种方法。

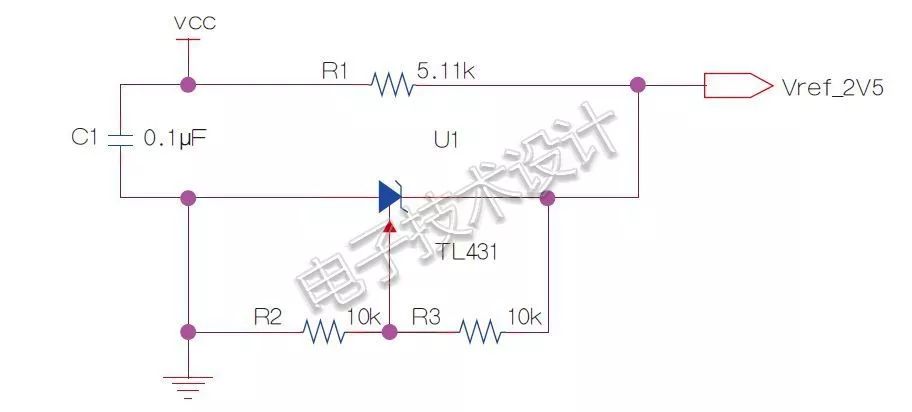

图1:电压参考图

使用FPGA来设计电源是大材小用了,除非将其用于教学目的。但是如果FPGA还剩下一部分没用着,可以执行一些有用的功能,而且它几乎是免费的,那么你就尽管使用最昂贵的FPGA来完成这项任务而不会有任何负罪感。首先,我们将介绍一种使用开关电源供电的简单方法。

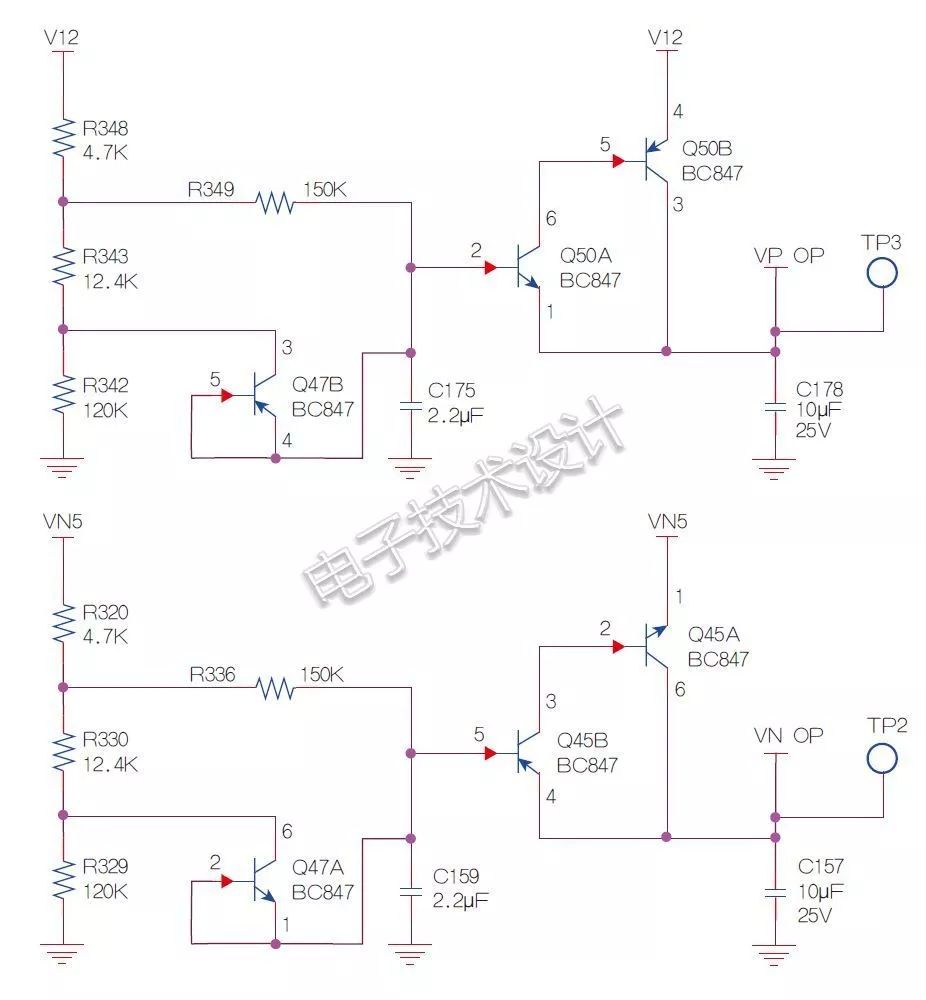

图2:有源滤波

开关电源有不同的拓扑结构,但它们都有一个共同的元件,就是一个用作临时储能的功率电感,它在负载和电源之间开关,因此而得名。将能量存储在电感器中并传递到输出的过程是很复杂的,甚至有点神秘,但这一过程已经有明确定义。神秘之处在于能量通过充电电流存储在电感的磁场中,当该电流中断时,磁场在试图保持充电电流方向和流动时会崩溃。虽然无法看到神秘的磁场充电/放电周期,但我们知道电感电流会随着时间而线性增加,这由其锯齿波形可以看出。

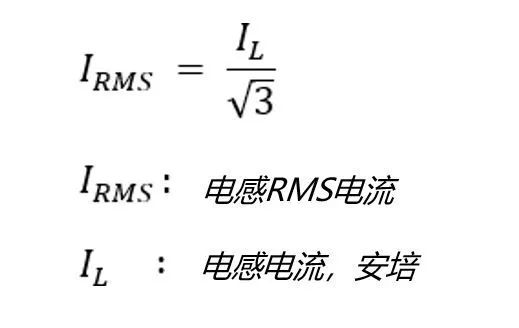

该波形的RMS电流可以用以下公式计算:

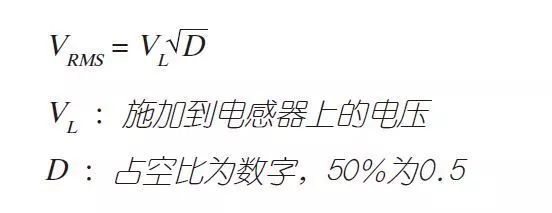

电压用以下公式计算:

对于电感电流,参见上面公式中的RMS电流:

这三个公式是我们的开关电源设计的基础。为了提高开关电源设计技巧,我们将设计三个电源:一个产生+5V(如图3),一个产生+35V(如图4),第三个产生-15V(如图5),它们都来自+15V输入电压。

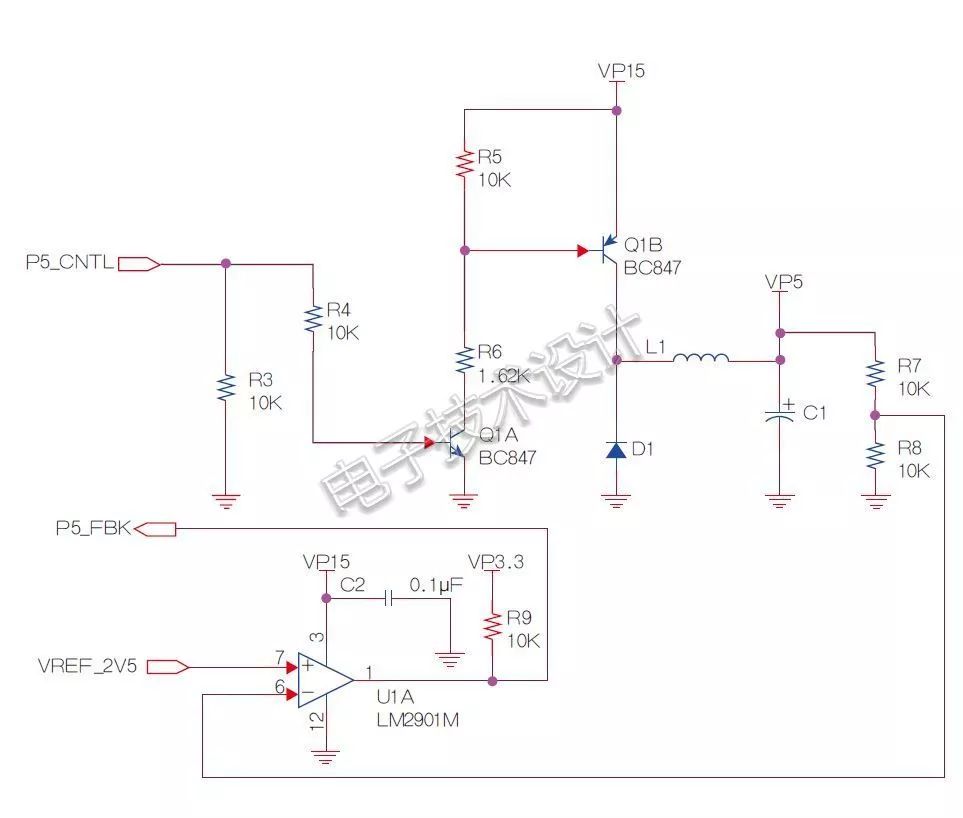

请注意,对于所有这三个电源,我们使用相同的FPGA模块(pcontrol),它带有一个由比较器驱动的反馈输入,以及用来驱动开关晶体管的输出。该模块还具有将其打开/关闭的使能输入。让我们分析一下图3所示的电路,这通常称为降压转换器开关电源拓扑。

图3:降压转换器开关电源拓扑结构

开始时Q1A和Q1B闭合,C1上的电压为零,由于施加到VREF_2V5输入的2.5V电压,U1A输出(P5_FBK)逻辑被强制为高电平,这表明VP5电源输出低于5V。输出电压通过R7和R8分压器设置为5V,但可以是2.5V以上的任何值。

作为响应,FPGA电源控制模块(PCM)将通过脉冲驱动P5_CNTL引脚,在TON持续时间为高电平。该电压将首先打开Q1A,然后是Q1B,利用VP15(15V)输入电压对L1电感器充电。在T(on)持续时间之后Q1A和Q1B关闭,切断L1的充电电流。此时,L1已将先前的电流存储在磁场中,并试图通过提供电流来保持电流流动方向和幅度。该电流流过D1并开始对C1充电,也为负载供电(图中未显示)。L1完全放电后,D1关闭,电路准备好进入下一个周期。经过多次循环后,VP5电压上升至5V,触发U1A引脚1至低电平,从而有效禁止P5_CNTL脉冲序列。一旦VP5电压降至5V以下,P5_CNTL脉冲序列将再次启动,使其成为闭环系统,以主动监控输出电压。请注意,以上的描述很基础,以清楚传达该电路的工作原理。

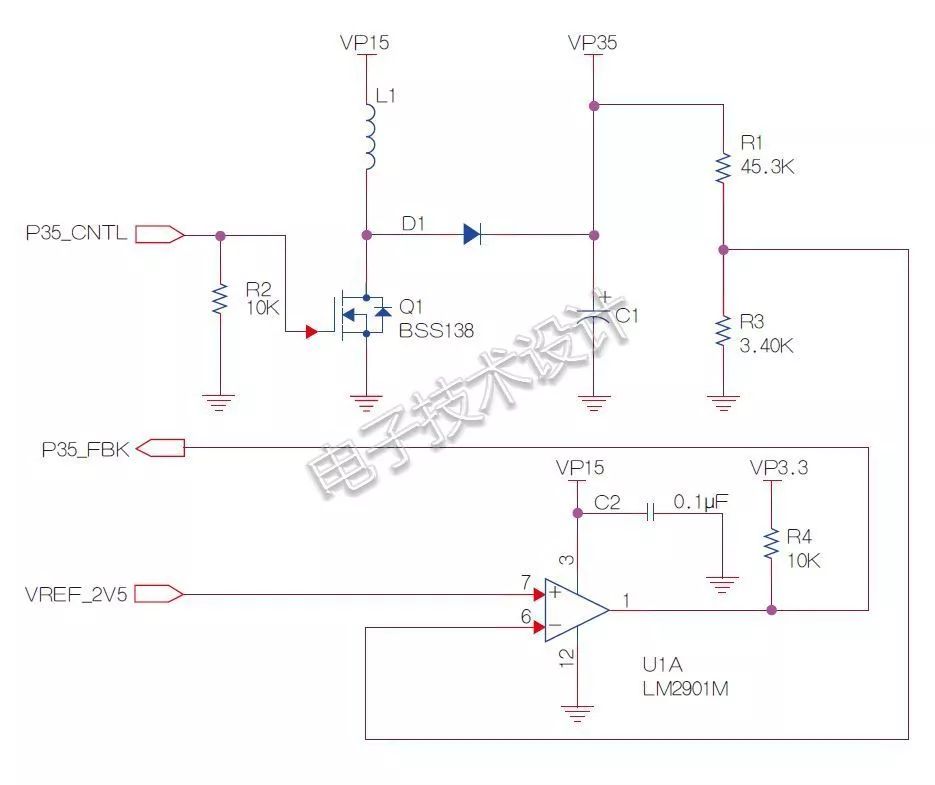

这种开关电源设计方法有一个优点:通过指定TON的方式让Q1B工作在安全区域,即使输出短路接地,也能够设置最大输出电流并实现数字输出限流。这是使用上面列出的第三个公式并选择晶体管的最大电流(IpK)作为计算基础来完成的。请参见表2了解计算方法,图4电路是一种反向降压开关电源拓扑。

图4:反向降压开关电源拓扑结构

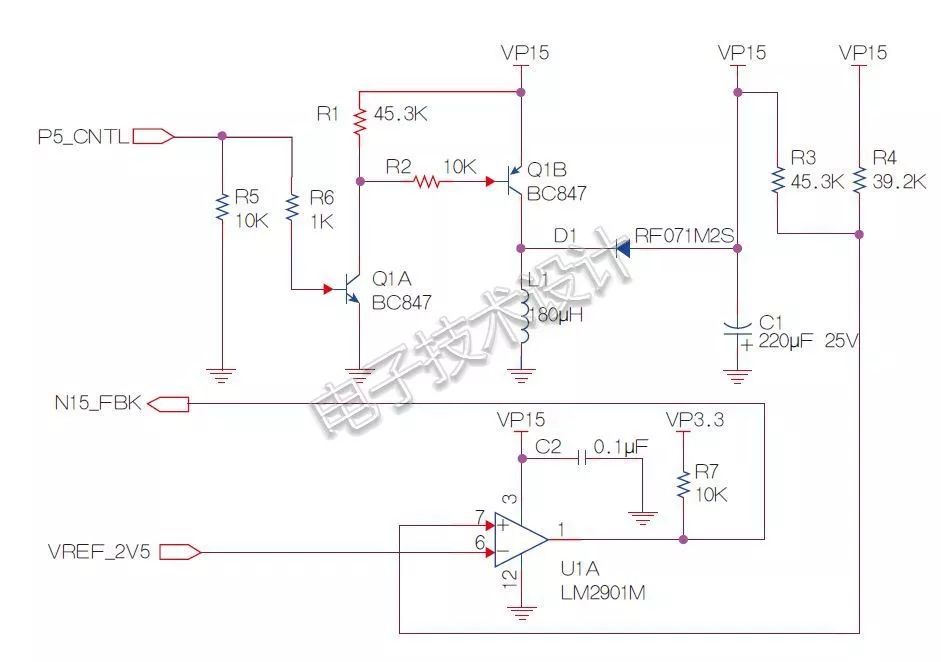

然而,在升压转换器(图5)中,我们无法控制最大输出电流,因为它受到通过L1和D1的正向电流的限制。

图5:升压转换器拓扑

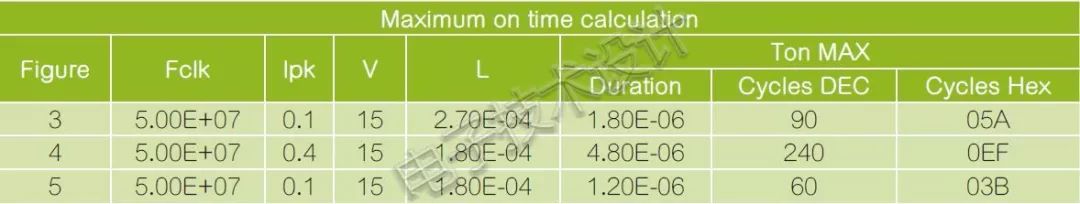

十六进制周期列中显示的计算值将由PCM用作最大TON设置。

表1:最大时间计算值

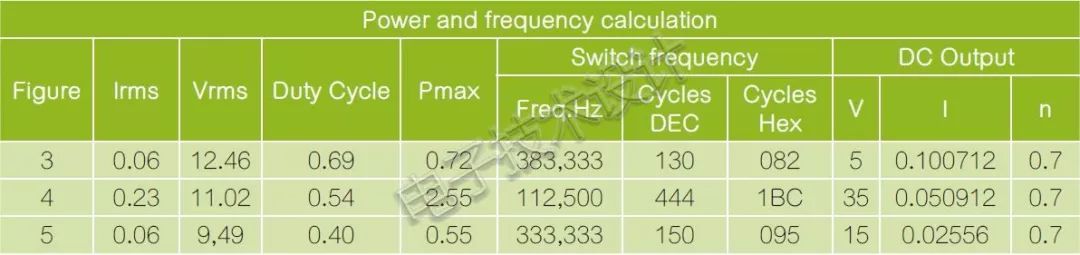

输出可用功率通过P=VrmcxIrmc公式计算,该公式描述输出的可用直流功率,通过估计效率70%进行调整。计算如表2所示。

表2:功率与频率计算

在调整表2中的值时,尽量将开关频率保持在500kHz以下,并将占空比保持在80%(0.8)以下,以使损耗保持在低水平。

下面是有关图3~5电路中元件选择的一些注意事项。首先,所选电感L1的饱和电流至少是所选IpK的两倍,这很重要。二极管D1建议用肖特基二极管,以最大限度地减小正向压降引起的效率损失。在大电流开关电源中用次级MOSFET来代替,可在二极管导通后立即打开,并与其并联连接。为这个电路选择的晶体管并不是最佳的,但还OK,因为占用空间小。在大电流开关电源设计中,通常在输出级使用MOSFET。

C1值不如L1重要,但会决定输出纹波电压。请注意,应选择低ESR(低于200mΩ)的电容。另外,要尽量保持较大的容量,要知道开关电源在输出端会有50~100mV的纹波。单独增加C1值不能减少这种纹波。

很多时候,我们需要产生“干净”的电压,以便为敏感的模拟电路供电,比如仪表放大器、ADC和其它精密模拟电路等。为此,我们需要添加有源滤波以使用图2~4中所述的开关电源(图2)。该电路从+12V电源提供VP_OP电压,从-12V提供VN_OP电压。它们是低于电源的两个基极/发射极电压。

这一电路看似简单,乍一看它的优点也不是很明显。请注意,组合的hfe Q1 (Q2)高于3000,具有C1电容值倍增的效果。简单的说,VP_OP就像连接到0.6F电容一样,它就像电池供电一样干净。该电路的缺点在于,由于Vbe的变化,VP_OP可能随温度在小范围内变化。这对于精密电子/运算放大器的供电不是大问题,但我们应该知道这一点。其另一个“特性”是上电时启动缓慢,这是由RC常数决定的。

-

模拟电路

+关注

关注

125文章

1557浏览量

102741 -

开关电源

+关注

关注

6463文章

8337浏览量

482054 -

电感器

+关注

关注

20文章

2330浏览量

70536

原文标题:如何利用多余的FPGA资源和最少的模拟电路设计电源?

文章出处:【微信号:WW_CGQJS,微信公众号:传感器威廉希尔官方网站 】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

一种可靠的开关电源保护电路

一种高压开关电源的设计

一种AC-DC开关电源的研制

一种AC/DC开关电源的研制

一种用于高频UPS的新型开关电源设计

一种简洁的高效率开关电源的设计

一种新颖的开关电源设计方法

一种新型开关电源的PWM控制

一种基于TOP260EN的开关电源设计

一种开关电源设计的极简方法

一种开关电源设计的极简方法

评论