可编程逻辑器件基础

1、数字逻辑设计历史-------了解历史进展

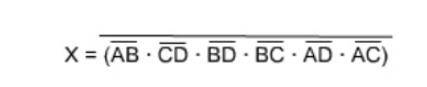

开始时:有复杂的逻辑关系,是我们初学者刚刚接触的数电方面的基础应用,设计一个基础的TTL逻辑,根据真值表-----卡诺图-----简历函数式逻辑表达式,举个例子:X=AB+CD+BD+BC+AD+AC,需要很多的基础逻辑单元,但是如果利用异或关系,可转换成:

利用这样的组合逻辑,这样可以将数量众多的基本逻辑单元简化,硬件相对变简单了。

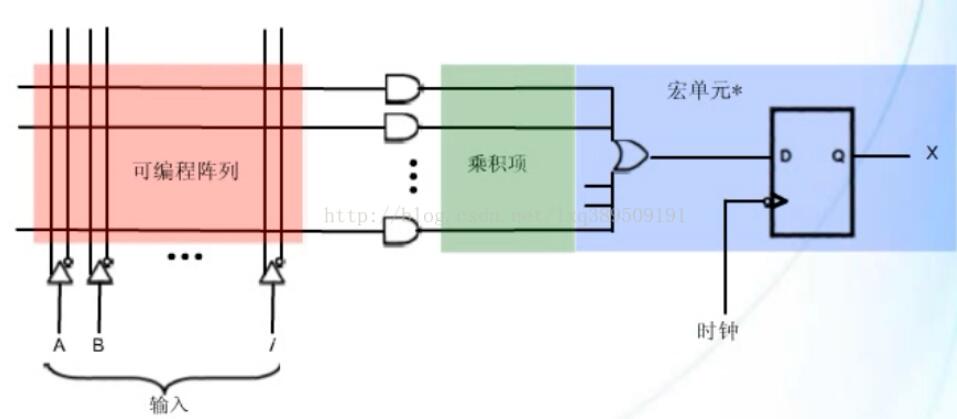

如果逻辑功能和寄存器组合到一个部件,通过布线(布线相当于一种控制)就可以得到一个简单的PAL---可编程阵列逻辑,一种简单的可编程控制单元,器件中的数量变少,占用更少的电路板,设计灵活,可防止逆向剖析,容易更新设计。

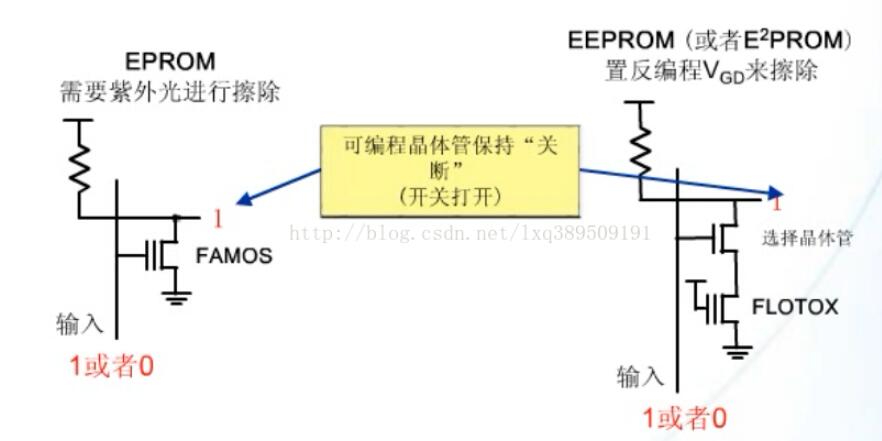

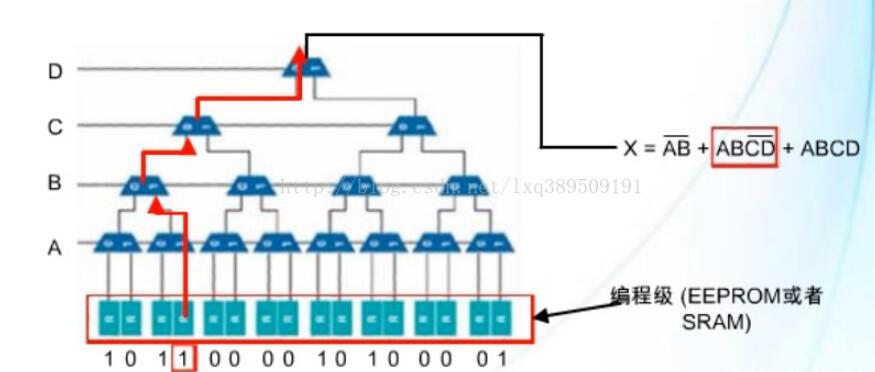

针对PAL的编程威廉希尔官方网站 实质(当前闪存威廉希尔官方网站 的关键):阵列交叉(跨线)上的浮栅型晶体管(含有第二个栅极,浮动栅极)在加上编程电压后,不会导通。以下两种晶体管不做任何设置,都可用作N型晶体管,栅极接地时,源级和漏极导通。当栅极设置电压后,电子被限制在浮动栅极,纵使浮动栅极设置电压值,晶体管依旧不导通,这样总是关断,相当于一个开关。

2、可编程逻辑基本威廉希尔官方网站

了解器件本身:

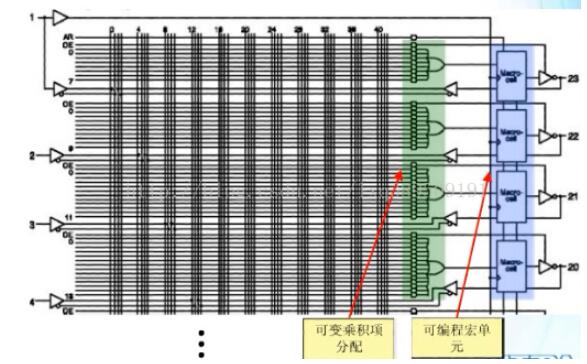

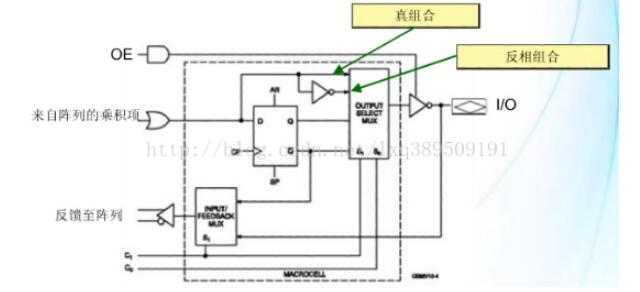

从PAL到可编程逻辑器件PLD,在单个器件中排列多个PAL阵列,存在可变的可乘积项分配和全面可编程宏单元。

可变的可乘积项分配:简单的想法,改变或门、与门的数量,不会浪费逻辑门,不需要复杂的延时网络。

灵活的可编程宏单元(主要进步):提供多种可编程选择,实现乘积和输出。

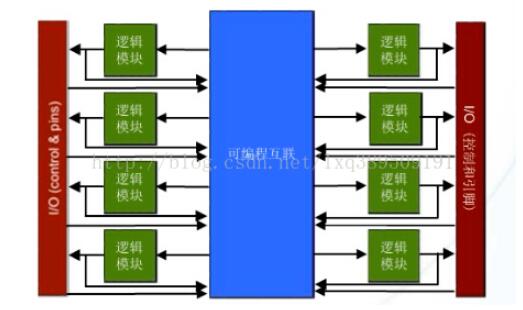

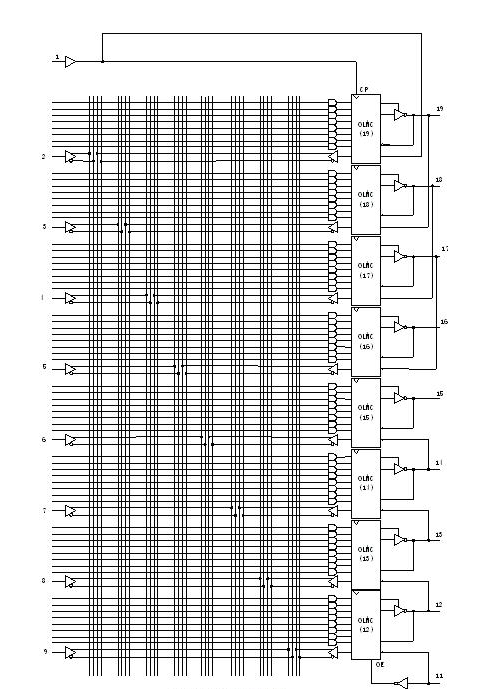

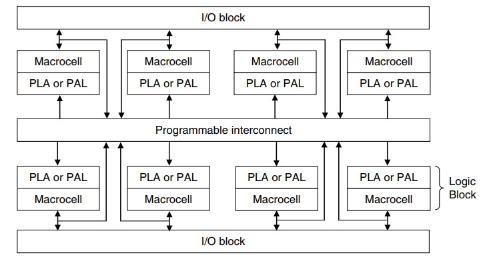

PLD进一步发展形成复杂的PLD(CPLD)-----在一个器件中,采用可编程互联和I/O,连接多个PLD:

CPLD的特性:

CPLD逻辑模块通常被称为逻辑阵列模块(LAB),每个LAB相当于一个PLD,含有4-20个宏单元,该宏单元还存在扩展项,提供可操控的乘积项分配和扩展,代价是额外的延时。即,建立一次乘积项就可以使用,大大减少了逻辑浪费。

LAB之间的互联称为可编程互联阵列(PI或PIA),和PAL可编程阵列相同的编程威廉希尔官方网站 (两种晶体管,EPROM、EEPROM或者闪存威廉希尔官方网站 编程),配置更高级,实现灵活的可编程关键,全局布线连接器件中的任何信号和任何目的位置。

单独的I/O控制模块,由PI将I/O引脚与LAB分开,I/O都有专用逻辑提供控制以及更多的功能,三态缓冲控制实现任意引脚的输入、输出和双向功能。

采用JTAG进行在系统编程(ISP)

由于可编程逻辑越来越大、越来越复杂,必须放在特定的条件下编译,器件放在特殊的单元,或者器件上加一些特殊装置,不能在线编译,故设计了一种和I/O分开的编程接口,几乎所有的FPGA都使用JTAG接口,简单的4、5线串行接口,构成单个器件长1位寄存器或者多个器件的JTAG链,可用于器件自检测或者系统编程(ISP),当PLD硬件生成EPROM编程电压,由JTAG接口进行控制,简化了实验室自编程。

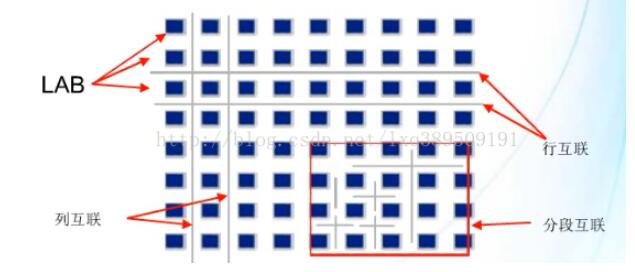

从CPLD到FPGA:理论上我们可以一直增加LAB,但是这样大大增加了额外的全局布线,但是如果LAB本身重新排列一个阵列中呢?这就是FPGA的由来。

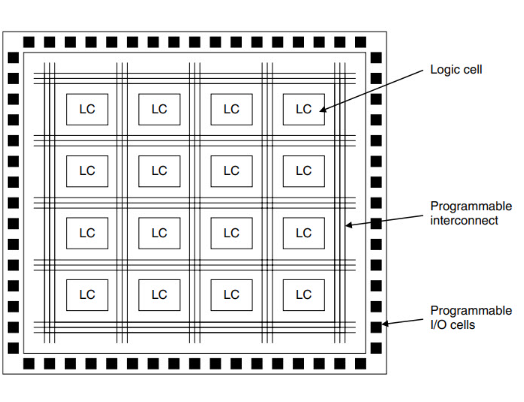

现场可编程门阵列(FPGA):LAB排列在大型阵列中,器件可以现场编程或重新编程,行列可编程互联,通过这中互联方式(在行列之间设置互联布线)可以跨越所有或者部分的阵列。

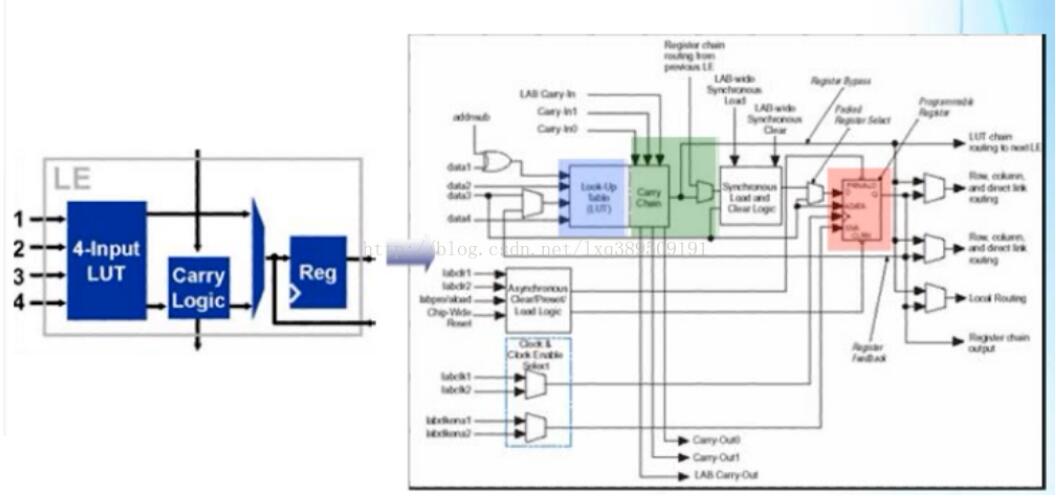

FPGA的LAB设计和CPLD不同,没有乘积项和宏单元,FPGA-LAB由逻辑单元(LE)构成,LE级联更容易建立复杂的功能,LE实质是一个4位查找表(LUT)、进位逻辑、输出寄存器逻辑构成。

4位查找表 LUT替代了CPLD中的乘积项阵列,LUT是由一系列级联复用的器件构成,LUT输入作为选择线,复用输入作为高或者低逻辑电平,之所以逻辑被称作查找表,通过差找正确的编程级,来选择输出,根据输入的值通过复用输入,将输出送到正确的位置,编程级的选择基于函数真值表,故可以灵活的建立一个组合函数(级联复用器),减少逻辑资源浪费。

LE同步部分来自可编程寄存器,该寄存器和CPLD宏单元相似,但配置灵活,配置为D\T\JK或者SR触发器工作,一般由全局的时钟来驱动时钟,任何时钟可驱动任何LE,可通过其他逻辑或者IO进行寄存器的异步控制,器件还可以反馈回LUT,产生严格的组合逻辑功能,这种寄存器只使用存贮、同步功能,这种灵活的LE输出级适合所有类型的逻辑操作。

LE和宏单元不同之处在于进位逻辑和LAB寄存器链逻辑,LE之间存在进位bit链,这种进位可以输出到别的LE,也可以输出到互联中,寄存器输出可以链接至LAB中的其他LE寄存器,形成和LUT无关的移位寄存器(适合DSP峰作),增强资源管理。

更高级的FPGA使用自适应逻辑模块(ALM)代替LE,提高性能和资源利用率,使用自适应的LUT(ALUT)可以任意划分,智能资源管理。

FPGA布线

所有器件资源都可以和器件中的任何布线连接,分为本地互联(LE之间互联、相邻LAB直接连接)、行列互联(固定长度布线、跨过多个LAB)。

FPGA IO单元

高级可编程模块可直接连接至行或者列互联,具有多种优良特性,同时存在特殊的逻辑。

其他典型FPGA特性

采用专用功能硬件模块代替某些LAB,存储器模块、嵌入式乘法器、高速收发器。(多查一下手册,看是否满足要求)

FPGA编程

大部分FPGA使用SRAM单元威廉希尔官方网站 (基本是个锁存器)对互联和LUT功能进行编程,必须在上电时进行编程,数据易丢失。FPGA编程信息必须存储在某一位置,以便在上电时对器件进行编程。主动编程方式:上电时FPGA自动控制编程顺序;被动编程:智能主机(CPU)控制编程;JTAG编程:实验室PC端编程。

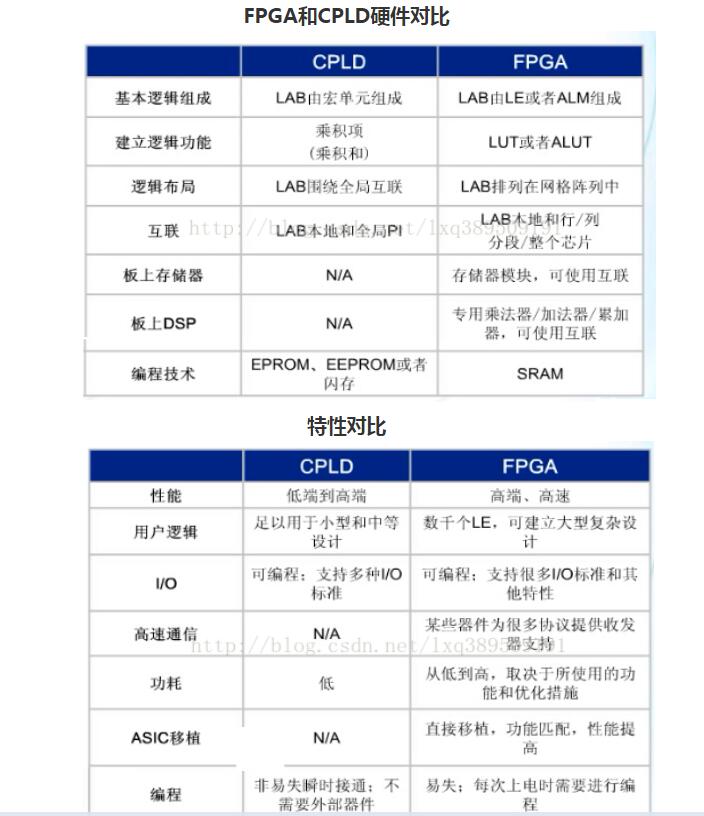

3、对比CPLD和FPGA

-

可编程逻辑

+关注

关注

7文章

515浏览量

44080 -

可编程逻辑器件

+关注

关注

5文章

139浏览量

30306

发布评论请先 登录

相关推荐

德州仪器可编程逻辑器件解决方案

德州仪器推出全新可编程逻辑产品系列

FPGA零基础学习系列精选:半导体存储器和可编程逻辑器件简介

fpga是什么意思?它有什么特点?

fpga是什么芯片

FPGA的内部结构工作过程

通用阵列逻辑(GAL)电路结构设计分析

可编程逻辑器件的优化过程主要是对什么进行

近日AMD宣布将停产多种可编程逻辑器件

可编程逻辑器件基础

可编程逻辑器件基础

评论