一、原理图网络命名

原理图网络命名时,字母必须为大写字母,不可以使用字母“O”;可以使用下划线和左斜线“/”;禁止使用小写字母、短横线、*等;

电源网络命名建议:10V以上命名举例,12V、36V等,数字在字母V前;10V以下电源命名举例,V33或者3V3、V18或者1V8、V09或者0V9;interwetten与威廉的赔率体系 电源命名举例,V33_AVDD_FPGA或者3V3_AVDD_FPGA ;可以增加后缀说明电源使用对象;

时钟网络命名规则:时钟网络命名以CLK开头,后接频率,可以增加使用对象说明,举例 CLK_50M_CPU;

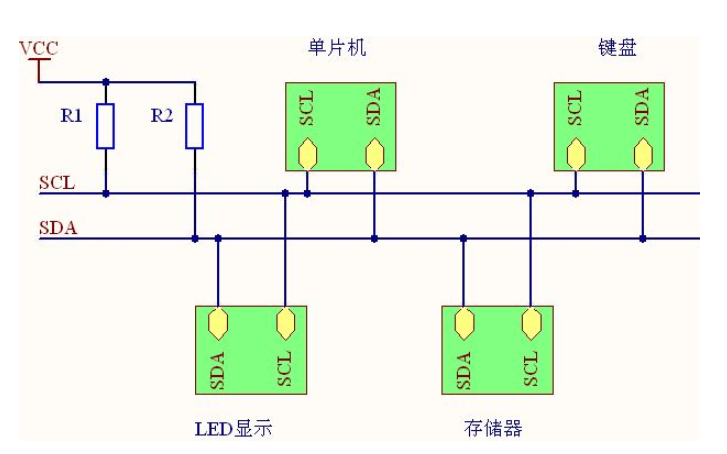

总线网络命名规则:总线类型开头,后接使用对象或者总线方向,举例 SGMII_CPU_PHY、JTAG_TDI_CPU、PCIE_CPU_FPGA、IIC_SCL_EEPROM等;

使能网络命名中包含EN,中断网络命名包含INT;

低有效信号命名规则,以“/”开头,例如 /RST_CPU、/INT_PHY、/SPI_CS 等;

指示灯信号命名规则,以LED开头,增加功能说明,举例 LED_CPU_RUN、LED_CPU_ALARM、LED_FPGA_DEBUG、LED_V33 等;

差分信号命名规则,以P N表示差分信号的+ -信号,举例 PCIE_CPU_FPGA_0_P、PCIE_CPU_FPGA_0_N,经过电阻、电容前或者后的信号,建议增加R C说明,举例 PCIE_CPU_FPGA_0_C_P、PCIE_CPU_FPGA_0_C_N。禁止使用+ -符号表示差分信号;差分信号网络必须全部标识,禁止使用自动生成网络名称;

二、原理图图表文字说明

对复杂器件的配置、上电启动等要进行图表说明。例如CPU的上电配置、PHY的地址配置等;

对开关或者有功能选择通道的器件,需要增加图表说明;

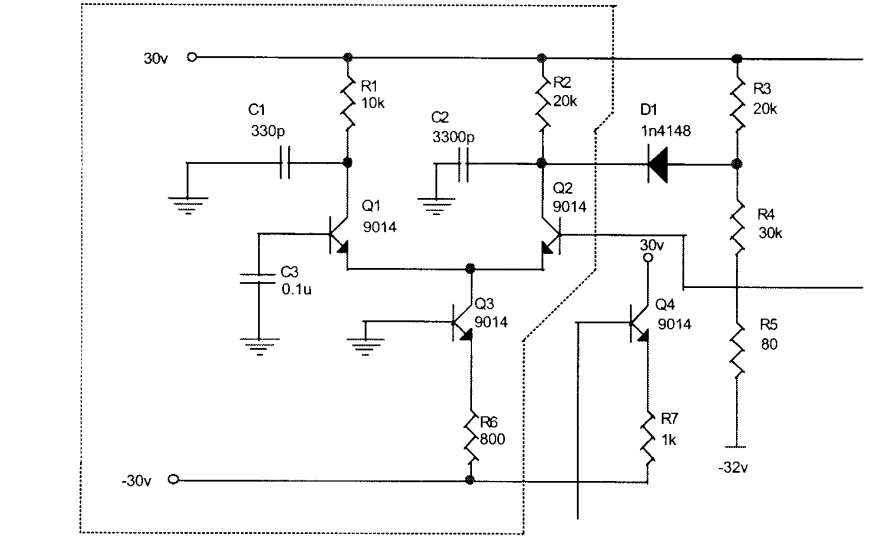

电源设计时,需要增加文字说明,例如输出电压公式、最大电流值,需求电流值;

电源限流设计时,需要增加文字说明,限流公式、限流大小、实际需要电流大小;

三、原理图CBB化设计

原理图设计时,对常用的功能模块,建议进行CBB化,例如电源、CPU、PHY等器件;

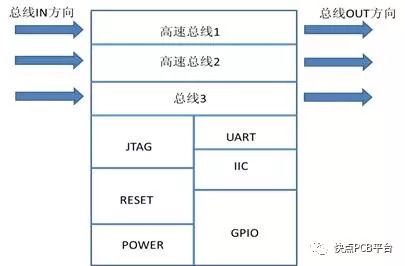

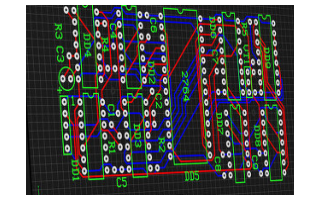

原理图功能模块CBB化时,总线IN的方向在左侧,OUT的方向在右侧,其他功能按区块进行放置,举例如下:

-

原理图

+关注

关注

1298文章

6340浏览量

233909 -

硬件

+关注

关注

11文章

3322浏览量

66208 -

PHY

+关注

关注

2文章

301浏览量

51734

原文标题:盘他|硬件开发中原理图设计规范

文章出处:【微信号:cn_maxwell,微信公众号:快点PCB平台】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

硬件原理图设计规范

【设计规范】orcad原理图

如何设计电路原理图详细设计规范说明

硬件开发的原理图设计规范详细说明

硬件开发的原理图设计规范详细说明

评论