SPI 协议简介

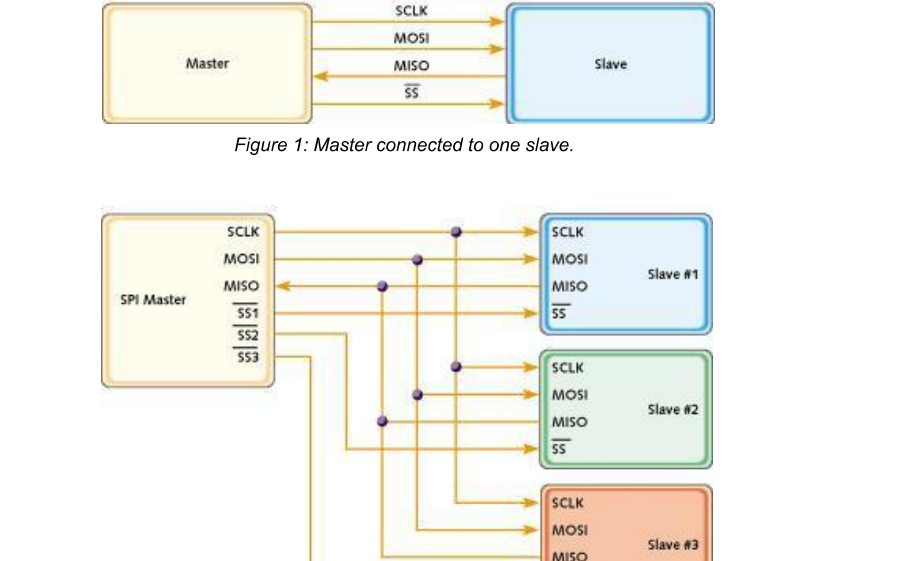

SPI是单master多slave的总线协议,全双工通信。如下图所示,一个master可以控制多个slave,通过ss信号选择需要控制的slave,ss低电平有效。

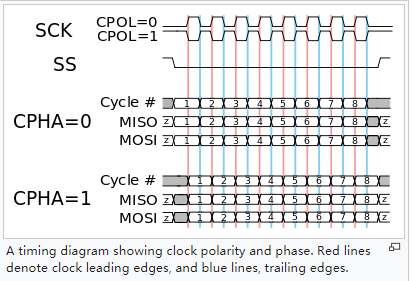

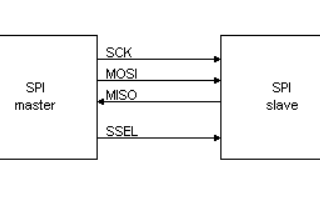

数据传输要遵循如下时序要求(下图是以收发数据位数为8作为示例)。其中SCK为SCLK,由master发出,SS为Slave片选信号。其中CPOL,CPHA为模式选择。master与slave的模式需要一致。MISO(单bit)为slave的输出数据线,master的输入数据线(未选中的slave的MISO为高阻态);MOSI(单bit)为master的输出数据线,slave的输入数据线。数据都是先发低位。

当CPOL=0,CPHA=0时:空闲时,SCLK为低电平;master和slave,在SCLK上升沿采集数据,下降沿发出数据。并在第一个SCLK上升沿之前,数据的第一bit必须送上数据线。

当CPOL=0,CPHA=1时:空闲时,SCLK为低电平;master和slave,在SCLK上升沿发出数据,下降沿采集数据。

当CPOL=1,CPHA=0时:空闲时,SCLK为高电平;master和slave,在SCLK上升沿发出数据,下降沿采集数据。并在第一个SCLK下降沿之前,数据的第一bit必须送上数据线。

当CPOL=1,CPHA=1时:空闲时,SCLK为高电平;master和slave,在SCLK上升沿采集数据,下降沿发出数据。

设计概述

本次提供了一个master接口与slave接口的参考设计。并且要求clk的时钟频率最好为SCLK时钟频率的三倍以上。当SCLK为clk的奇数倍分频时需要考虑误差积累问题。

SPI_master_if(SPI master接口驱动)的信号端口说明如下表:

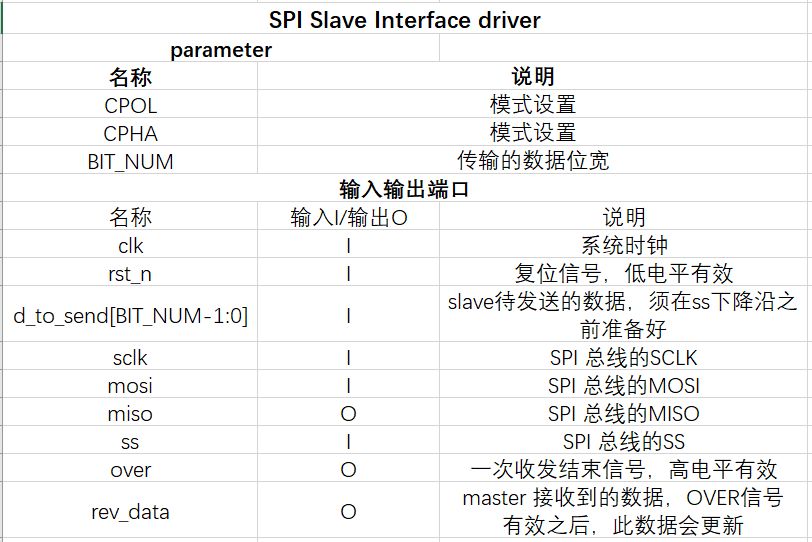

SPI_slave_if(SPI slave接口驱动)的信号端口说明如下表:

并且还提供了一个简单的TB(SPI_tb.sv)。大家可以跑跑仿真。

目前此设计只是做了功能仿真,并未上板与其他SPI设备进行实测,如有问题,希望大家给予反馈。

-

仿真

+关注

关注

50文章

4076浏览量

133560 -

SPI

+关注

关注

17文章

1706浏览量

91530 -

驱动电路

+关注

关注

153文章

1529浏览量

108499

原文标题:SPI 接口驱动电路设计

文章出处:【微信号:LF-FPGA,微信公众号:小鱼FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

求助。SPI接口主模式电路设计。

SPI接口主模式电路设计

无线传感器节点SPI接口电路设计

基于CP2120的SPI与I2C总线接口转换电路设计

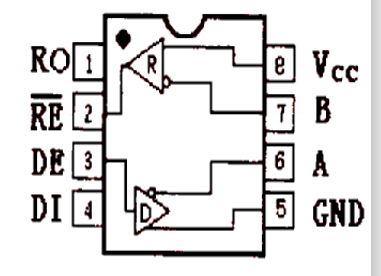

基于SPI总线的RS-422接口电路设计

基于SPI接口的凌阳单片机键盘设计

LED驱动电路设计中文资料概述

串行接口威廉希尔官方网站 的详细资料概述

带有N的SPI总线详细资料概述

SPI接口驱动电路设计的资料概述

SPI接口驱动电路设计的资料概述

评论