微控制器的封装在系统的小型化中起着关键作用。芯片上外设选择,焊盘数量和芯片尺寸的权衡都限制了缩小微控制器尺寸的能力,但仍然有助于减小终端设备的整体尺寸。

散热问题也很重要考虑微控制器的尺寸变小。随着小型芯片上的晶体管越来越多,以更高的频率运行,功耗是一个关键考虑因素。在降低电压和选通不同外围设备以使未使用的元件不消耗功率的同时可以降低总热负荷,然后必须有效地去除产生的多余热量或者微控制器将降级并最终失效。这是微控制器系统小型化时必须考虑的一个关键可靠性问题。

这是引脚与尺寸之间的折衷所在。封装上的附加引脚可用于连接散热通孔,以消除多余的热量来自微控制器和其他可能对高温敏感的设备,如无线接口。

虽然最新的芯片级封装可以减少具有特定功能的设备的总体占用空间,但占用的面积减少了四分之一,将更多外设集成到器件中并拥有更多引脚进行散热的机会可能更为重要。

设计人员还必须意识到小型化的目标。 ARM 32位内核,例如Cortex-M0 +甚至M4,小于1平方毫米的硅片 - 芯片尺寸更多地取决于芯片上的内存量,对于封装考虑至关重要,需要连接外部世界的外围设备。最小的M0器件,例如飞思卡尔的Kinetis KL02,在芯片级封装中可以小到1.9 x 2.0 mm,几乎不比芯片本身大。在不到4平方毫米的情况下,与球栅阵列或LGA封装相比,PCB面积减少了25%,但GPIO的数量增加了60%,最多可达28行。这一举措几乎是“硅尘”,使设计人员能够大幅减小电路板尺寸,同时不会影响最终产品的性能,功能集成和功耗。

图1:Kinetis KL02采用芯片级封装的系列产品可提供几平方毫米的完整微控制器。

在这种尺寸下,功耗和散热考虑是关键,芯片上可以做很多事情来降低整体功耗并允许一个较小的包裹。该内核以48 MHz的频率运行,有助于在整个-40°C至+ 105°C的温度范围内保持功率下降,并允许器件在尽可能多的不同环境中使用。还有多种低功耗模式,例如新的计算模式,通过将外设置于异步停止模式来降低动态功耗。低功耗UART(LPUART),SPI,I²C,数据转换器,低功耗定时器和DMA引擎均支持低功耗模式操作,无需唤醒内核即可运行。

但是,这并不一定反映硅的实际用途。如果需要单独的掩模,制造具有各种外围设备和存储器选项的微控制器的许多不同版本实际上是昂贵的。相反,实现和制造具有超集功能的单一设计,并且仅连接一组特定功能。这使得硅供应商能够提供广泛的产品,同时最大限度地降低制造成本并从规模经济中获益。

下一个发展阶段是创建更灵活的I/O配置。正如内部总线矩阵连接外设一样(如Atmel 4S系列),供应商也在推出带有连接I/O引脚的矩阵的设计。这允许任何外设连接到任何I/O引脚,为供应商提供更大的灵活性,以提供一系列引脚兼容的器件,其中相同的I/O始终位于同一位置。由于存在备用硅,这有助于系统设计人员在不影响整体尺寸的情况下实现可扩展性能的设计。

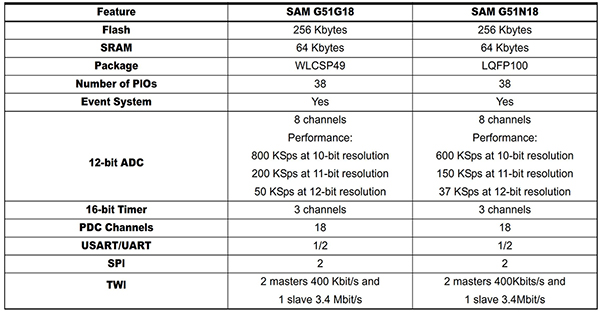

这一切都意味着封装威廉希尔官方网站 是微控制器小型化的关键。 Atmel开发了SAM G51系列闪存微控制器,它也基于具有浮点支持的M4内核。它还可以以48 MHz的最高速度运行,具有高达256 KB的闪存和高达64 KB的SRAM。外设集包括一个USART,两个UART,两个TWI,一个高速TWI,最多两个SPI,一个三通道通用16位定时器,一个RTT和一个8通道,12位ADC,提高引脚数要求。

图2:Atmel SAM G51系列微控制器显示了封装选项范围。

该外设集允许SAM G51系列针对a广泛的应用包括消费者,工业控制和PC外围设备,只有两种封装类型 - 49球WLCSP芯片级封装或100引脚LQFP封装。

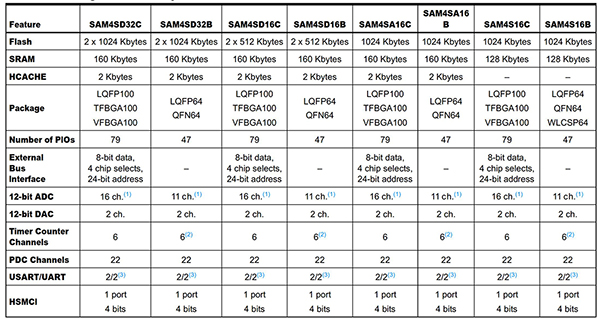

与此同时,Atmel的SAM4S系列也基于ARM Cortex-M4处理器内核。它的最高运行速度为120 MHz,具有高达2048 KB的闪存,可选的双存储区实现和高速缓存,以及高达160 KB的SRAM。外设包括带嵌入式收发器的全速USB设备端口,用于SDIO/SD/MMC的高速MCI,带存储器控制器的外部总线接口,两个USART,两个UART,两个TWI,三个SPI,一个I²S,以及一个PWM定时器,两个三通道通用16位定时器(具有步进电机和正交解码器逻辑支持),一个RTC,一个12位ADC,一个12位DAC和一个interwetten与威廉的赔率体系 比较器。 》所有这些都对包装和引脚数量提出了更高的要求。该系列具有多达79个I/O线,具有外部中断功能(边沿或电平灵敏度),去抖,毛刺滤波和片上串联电阻终端,以及3个32位并行输入/输出控制器。 》这导致了一系列封装,从100引脚到48引脚,但使用更传统的威廉希尔官方网站 :

100引脚封装

LQFP,14 x 14 mm,间距0.5 mm

TFBGA,9 x 9 mm,间距0.8 mm

VFBGA,7 x 7 mm ,间距0.65 mm

64引脚封装

LQFP,10 x 10 mm,间距0.5 mm

QFN,9 x 9 mm,间距0.5 mm

WLCSP,4.42 x 3.42 mm,间距0.4 mm(SAM4S16/S8)

WLCSP,3.32 x 3.32 mm,间距0.4 mm(SAM4S4/S2)

48引脚封装

LQFP,7 x 7 mm,间距0.5 mm

QFN,7 x 7 mm,间距0.5 mm

图3:Atmel SAM4S系列具有更广泛的外设选项,可实现更大的封装。

未来趋势

在同一封装中叠加芯片的新封装威廉希尔官方网站 也有助于减少整体足迹。微控制器芯片不是在微控制器旁边有一个单独的存储芯片,而是安装在一个封装中的存储器芯片或大型FPGA的顶部。这种方法通常称为2.5D,需要硅中介层和硅通孔(TSV),这是一种相对较新的威廉希尔官方网站 ,现在正在逐渐成熟并变得越来越普遍。这用于需要大量存储器的高端设备,这些设备无法经济高效地集成在单个芯片上。

全3D封装可将多个芯片直接堆叠在一起;也许边缘上有I/O焊盘,以允许不同器件之间的互连。虽然这是小型化的长期目标,将印刷电路板上的所有元件从微控制器到存储器和无线接口整合到一个封装器件中,但它仍然需要克服许多成本,可靠性和散热问题。 br》结论

来自多个供应商的各种微控制器隐藏了这种设备小型化的策略。来自一个供应商的不同系列的封装范围,都在同一个核心,展示了封装,外设组合,功耗和系统尺寸之间的复杂权衡。在性能曲线的下游,具有复杂外设的32位控制器现在只有几平方毫米,成为渗透到物联网中的“硅尘”。

-

微控制器

+关注

关注

48文章

7552浏览量

151418 -

芯片

+关注

关注

455文章

50812浏览量

423590 -

封装

+关注

关注

126文章

7901浏览量

142954

发布评论请先 登录

相关推荐

微控制器小型化给系统设计带来的挑战

电源的小型化轻量化设计方案

小型化医疗电子设备

微电子威廉希尔官方网站 有什么重要性?

电源对电子设备的重要性

基于CPLD的机载小型化控制与保护

封装威廉希尔官方网站

对于微控制器小型化的重要性

封装威廉希尔官方网站

对于微控制器小型化的重要性

评论