1.什么是JESD204B

该标准描述的是转换器与其所连接的器件(一般为FPGA和ASIC)之间的数GB级串行数据链路,实质上,具有高速并串转换的作用 。

2.使用JESD204B接口的原因

1. 不用再使用数据接口时钟(时钟嵌入在比特流中,利用恢复时钟威廉希尔官方网站 CDR)

2. 不用担心信道偏移(信道对齐可修复此问题,RX端FIFO缓冲器)

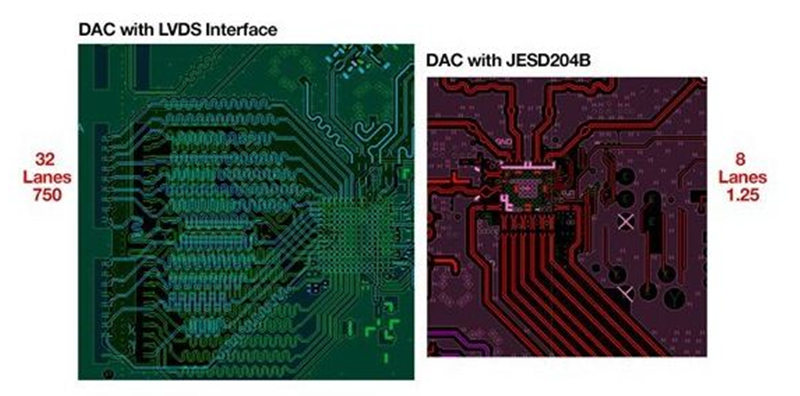

3. 不用再使用大量IO口,布线方便(高速串行解串器实现高吞吐量)

4. 多片IC同步方便

4 。关键变量

M:converters/device,转换器(AD/DA)数量

L:lanes/ device(link),通道数量

F:octets/frame(per lane),每帧的8位字节数

K:frames/multiframe,每个多帧的帧数

N:converter resolution,转换器分辨率

N’:total bits/sample,4的倍数,N’=N+控制和伪数据位。

S:samples/converter/frame cycle,每个转换器每帧发送的样本数。当S=1时,帧时钟=采样时钟

CS:control bits/sample

CF:control words/frame cycle/device(link),通常只在HD=1时使用。

5. subclass0~2确定延迟

subclass0:不支持确定延迟;

subclass1:SYSREF,(AD9370支持的是子类1,IP核默认也是子类1 ),利用确定延迟来对齐多片IC。

subclass2:SYNC~。

6 。 subclass1的三个阶段

1) 代码组同步(CGS):

1. RX将SYNC~引脚拉低,发出一个同步请求。

2. TX从下一个符号开始,发送未加扰的/K28.5/符号(每个符号10位)。

3. 当R X接收到至少4个无错误的连续/K28.5/符号时,R X同步,然后将SYNC~引脚拉高。

4. R X必须接收到至少4个无错误8B/10B字符,否则同步将失败,链路留在CGS阶段。

5. C G S阶段结束,I L A S阶段开始。

注意:

1. 串行数据传输没有接口时钟,因此RX必须将其数位及字边界与 TX 串行输出对齐。RX 向 TX 发送 ~SYNC 请求信号,让其通过所有信道发送一个已知的重复比特序列K28.5。RX 将移动每个信道上的比特数据,直到找到 4 个连续的 K28.5 字符为止。此时,它不仅将知道比特及字边界,而且已经实现了 CGS。

2. RX~SYNC的输出必须与RX的帧时钟同步,同时要求TX的帧时钟与~SYNC同步(可通过~SYNC复位TX的帧时钟计数器来实现)。

3. 不能使用交流耦合。(with the exception that SYNC~ should never be ACcoupled)。

2) 初始通道同步(ILAS):

1.在JESD204B中,发送模块捕捉到SYNC~信号的变换,在下一个本地多帧(LMFC)边界上启动ILAS。

2.ILAS主要对齐链路的所有通道,验证链路参数,以及确定帧和多帧边界在接收器的输入数据流中的位置。

3.ILAS由4个多帧组成。每个多帧最后一个字符是多帧对齐字符/A,第一,三,四个多帧以/R字符开始,以/A字符结束。接收器以各通道的最后一个字符/A对齐接收器内各通道内各多帧的末尾。

4.这些特定的控制字符只用于初始通路对齐序列中,而不用在数据传输的任何其他阶段。CGS和ILAS阶段不加扰。

5.RX模块中的FIFO吸收信道偏移。

3) 数据传输阶段:没有控制字符,获取链路全带宽。利用字符替换来监视数据同步,多帧计数器LMFC。

7.Device clk

系统基准时钟,提供采样时钟,JESD204B时钟,帧串行器时钟。产生帧时钟和多帧时钟。器件时钟用来捕捉SYSREF,并完成帧和多帧时钟的前沿相位对齐。子类1中,多帧时钟周期必须是器件时钟的整数倍。ADC/DAC/FPGA可运行于不同速率,但必须同源且频率相关。

8.同步对齐过程

发送器和接收器各维护一个多帧计数器(L M F C),所有发送器和接收器连接到一个公共(源)SYSREF,这些器件利用SYSREF复位其LMFC,这样所有LMFC应互相同步(在一个时钟周期内)。In the TX, the detected phase of the LMFC determines the momentswhen alignment characters can be sent. In the RX, the detected phase of theLMFC determines the moments that the alignment characters are read out from theFIFO.

SYSREF signal (DeviceSubclass 1):1.确定时延(小于1个多帧时钟周期)。2.对齐和器件时钟同源,LMFC周期的整数倍,在Device Clk沿变化时采样SYSREF信号,确定时延,对齐多帧和帧时钟。SYSREF用于对齐所有收发器件LMFC相位。

SYNC~ signal:同步请求信号。接收端:与接收器帧时钟同步。CGS后在接收端LMFC边沿拉高。释放SYNC(所有器件都会看到)后,发送器在下一次(TX) LMFC绕回0时开始I L A S。如果F*K设置适当,大于(发送器编码时间)+(线路传播时间)+(接收器解码时间),则接收数据将在下一个LMFC之前从接收器的S E R D E S传播出去。接收器将把数据送入F I F O,然后在下一个(R X)L M F C边界开始输出数据。发送器SERDES输入与接收器FIFO输出之间的已知关系称为“确定性延迟。

-

接口

+关注

关注

33文章

8598浏览量

151153 -

JESD204B

+关注

关注

5文章

76浏览量

19138

发布评论请先 登录

相关推荐

jesd204b

JESD204B串行接口时钟的优势

JESD204B协议有什么特点?

JESD204B协议介绍

JESD204B协议概述

JESD204B SystemC module 设计简介(一)

JESD204B标准及演进历程

JESD204B协议相关介绍与具体应用实例

JED204B是什么?JESD204B的分类及优缺点介绍

JESD204B使用说明

jesd204b协议相关知识介绍

jesd204b协议相关知识介绍

评论