物理优化是Vivado实现流程中更快时序收敛的重要组成部分。 了解如何在Vivado中应用此功能以交换运行时以获得更好的设计性能。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

赛灵思

+关注

关注

32文章

1794浏览量

131322 -

交换

+关注

关注

0文章

32浏览量

16679 -

Vivado

+关注

关注

19文章

812浏览量

66637

发布评论请先 登录

相关推荐

光波导系统中光栅几何结构的优化

| | 次我们强调了快速物理光学软件VirtualLab Fusion分析光波导系统性能。这次我们在设计工作流程中处理一个密切相关的步骤: 在系统的耦合和扩展区域中使用的光栅几何结构的优化

发表于 12-20 10:27

仿真系统的性能优化技巧

在现代工业和科学研究中,仿真系统扮演着越来越重要的角色。它们不仅能够帮助我们预测复杂系统的行为,还能在没有实际物理原型的情况下进行实验和测试。然而,随着仿真模型的复杂度增加,性能优化成

SSM框架的性能优化技巧 SSM框架中RESTful API的实现

SSM框架的性能优化技巧 SSM(Spring + Spring MVC + MyBatis)框架的性能优化是提升Java Web应用性能的

光波导系统中光栅几何结构的优化

快速物理光学软件VirtualLab Fusion拥有分析光波导系统性能。这次我们在设计工作流程中处理一个密切相关的步骤: 在系统的耦合和扩展区域中使用的光栅几何结构的优化。

Virt

发表于 12-16 10:39

Vivado之实现布局布线流程介绍

一、前言 本文将介绍Vivado进行综合,以及布局布线的内部流程,熟悉该流程后结合Settings中对应的配置选项,对于时序收敛调试将更具有针对性。 二、Implementation(实现) 实现

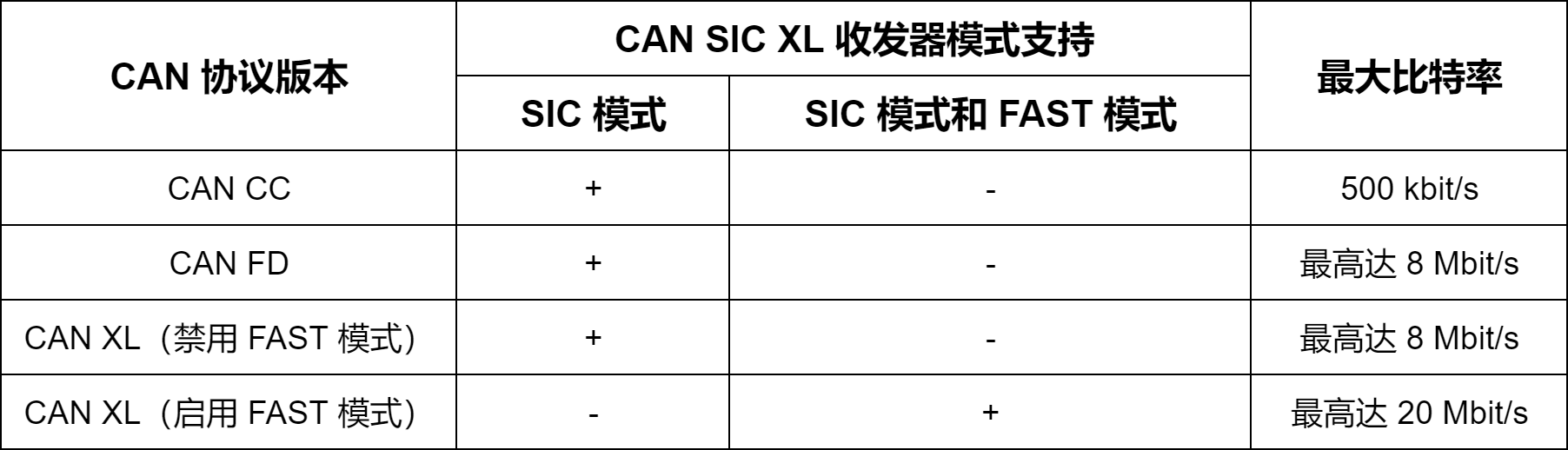

CAN XL物理层揭秘(下):物理层组合与兼容性

CAN XL网络凭借物理层革新,在汽车电子和工业通信中占据重要地位。在上篇中,我们深入探讨了CAN XL网络中的物理层革新与优势(点击回顾)。本文将继续这一话题,重点介绍CAN XL网

如何在电路中优化GND连接 GND在高频应用中的挑战

在电路中优化GND连接以及应对GND在高频应用中的挑战,是确保电路性能稳定、减少干扰和噪声的关键环节。以下是对这两个方面的介绍: 一、优化G

AI大模型的性能优化方法

AI大模型的性能优化是一个复杂而关键的任务,涉及多个方面和策略。以下是一些主要的性能优化方法: 一、模型压缩与优化 模型蒸馏(Model D

优化 FPGA HLS 设计

优化 FPGA HLS 设计

用工具用 C 生成 RTL 的代码基本不可读。以下是如何在不更改任何 RTL 的情况下提高设计性能。

介绍

高级设计能够以简洁的方式捕获设计,从而

发表于 08-16 19:56

如何在AMD Vivado™ Design Tool中用工程模式使用DFX流程?

本文介绍了在 AMD Vivado™ Design Tool 中用工程模式使用 DFX 流程以及需要注意的地方。在使用 DFX 工程模式的过程中要把具体步骤映射到相应的 DFX 非工程模式的步骤,这样才能更好地理解整个流程的运行

鸿蒙语言ArkTS(更好的生产力与性能)

可以传递类型D的变量,这种灵活性可能不符合开发者的意图,容易带来程序行为的正确性问题。另外,由于类型D和类型C布局不同,那么foo中对c.s这个属性访问就不能被优化成根据固定偏移量访问的方式,从而给运行时性能造成瓶颈。

发表于 02-17 15:56

TC332如何获得变体中物理上独立的ADC通道的数量?

根据 TC33X 的附录,TC332 变体的模拟输入总数应为 9+8 通道。 但是在引脚配置工具中,输入较少。 我还检查了其他变体;工具和 ds 总是不同的。 如何获得变体中物理上独立

发表于 01-25 06:53

如何在Vivado中应用物理优化获得更好的设计性能

如何在Vivado中应用物理优化获得更好的设计性能

评论