SDRAM:Synchronous Dynamic Random Access Memory,同步动态随机存储器,同步是指Memory工作需要同步时钟,内部的命令的发送与数据的传输都以它为基准;动态是指存储阵列需要不断的刷新来保证数据不丢失;随机是指数据不是线性依次存储,而是自由指定地址进行数据读写。

SDRAM在读写数据时重点注意以下信号:

(1)CLK:时钟信号,为输入信号。SDRAM所有输入信号的逻辑状态都需要通过CLK的上升沿采样确定。

(2)CKE:时钟使能信号,为输入信号,高电平有效。CKE信号的用途有两个:一、关闭时钟以进入省电模式;二、进入自刷新状态。CKE无效时,SDRAM内部所有与输入相关的功能模块停止工作

(3)CS#:片选信号,为输入信号,低电平有效。只有当片选信号有效后,SDRAM才能识别控制器发送来的命令。设计时注意上拉

(4)RAS#:行地址选通信号,为输入信号,低电平有效

(5)CAS#:列地址选通信号,为输入信号,低电平有效。

(6)WE#:写使能信号,为输入信号,低电平有效。

当然还包括bank[…]地址信号,这个需要根据不同的型号来确定,同样为输入信号;地址信号A[…],为输入信号;数据信号DQ[…],为输入/输出双向信号;数据掩码信号DQM,为输入输出双向信号,方向与数据流方向一致,高电平有效。当其有效时,数据总线上出现的对应数据字节被接收端屏蔽。SDRAM之所以成为DRARM就是因为它要不断进行刷新(Refresh)才能保留住数据,因此它是DRAM最重要的操作。那么要隔多长时间重复一次刷新,目前公认的标准是,存储体中电容的数据有效保存期上限是64ms(毫秒,1/1000秒),也就是说每一行刷新的循环周期是64ms。这样刷新速度就是:行数量/64ms。我们在看内存规格时,经常会看到4096 Refresh Cycles/64ms或8192 Refresh Cycles/64ms的标识,这里的4096与8192就代表这个芯片中每个Bank的行数。刷新命令一次对一行有效,发送间隔也是随总行数而变化,4096行时为15.625μs(微秒,1/1000毫秒),8192行时就为7.8125μs。HY57V561620为8192 refresh cycles / 64ms。

SDRAM是多Bank结构,例如在一个具有两个Bank的SDRAM的模组中,其中一个Bank在进行预充电期间,另一个Bank却马上可以被读取,这样当进行一次读取后,又马上去读取已经预充电Bank的数据时,就无需等待而是可以直接读取了,这也就大大提高了存储器的访问速度。

为了实现这个功能,SDRAM需要增加对多个Bank的管理,实现控制其中的Bank进行预充电。在一个具有2个以上Bank的SDRAM中,一般会多一根叫做BAn的引脚,用来实现在多个Bank之间的选择。

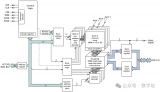

SDRAM具有多种工作模式,内部操作是一个复杂的状态机。SDRAM器件的引脚分为以下几类。

(1)控制信号:包括片选、时钟、时钟使能、行列地址选择、读写有效及数据有效。

(2)地址信号:时分复用引脚,根据行列地址选择引脚,控制输入的地址为行地址或列地址。

(3)数据信号:双向引脚,受数据有效控制。

SDRAM的所有操作都同步于时钟。根据时钟上升沿控制管脚和地址输入的状态,可以产生多种输入命令。

模式寄存器设置命令。

激活命令。

预充命令。

读命令。

写命令。

带预充的读命令。

带预充的写命令。

自动刷新命令。

自我刷新命令。

突发停命令。

空操作命令。

根据输入命令,SDRAM状态在内部状态间转移。内部状态包括模式寄存器设置状态、激活状态、预充状态、写状态、读状态、预充读状态、预充写状态、自动刷新状态及自我刷新状态。

SDRAM支持的操作命令有初始化配置、预充电、行激活、读操作、写操作、自动刷新、自刷新等。所有的操作命令通过控制线CS#、RAS#、CAS#、WE#和地址线、体选地址BA输入。

1、行激活

行激活命令选择处于空闲状态存储体的任意一个行,使之进入准备读/写状态。从体激活到允许输入读/写命令的间隔时钟节拍数取决于内部特征延时和时钟频率。HY57V561620内部有4个体,为了减少器件门数,4个体之间的部分电路是公用的,因此它们不能同时被激活,而且从一个体的激活过渡到另一个体的激活也必须保证有一定的时间间隔。

2、预充电

预充电命令用于对已激活的行进行预充电即结束活动状态。预充电命令可以作用于单个体,也可以同时作用于所有体(通过所有体预充电命令)。对于触发写操作必须保证在写入预充电命令前写操作已经完成,并使用DQM禁止继续写入数据。预充电结束后回到空闲状态,也可以再次被激活,此时也可以输入进入低功耗、自动刷新、自刷新和模式设置等操作命令。

预充电中重写的操作与刷新操作一样,只不过预充电不是定期的,而只是在读操作以后执行的。因为读取操作会破坏内存中的电荷。因此,内存不但要每64ms刷新一次,而且每次读操作之后还要刷新一次。

3、自动预充电

如果在触发读或触发写命令中,A10/AP位置为“1”,在读写操作完成后自动附加一个预充电动作。操作行结束活动状态,但在内部状态机回到空闲态之前不能给器件发送新的操作命令。

4、触发读

触发读命令允许某个体中的一行被激活后,连续读出若干个数据。第一个数据在经过指定的CAS延时节拍后呈现在数据线上,以后每个时钟节拍都会读出一个新的数据。触发读操作可以被同体或不同体的新的触发读/写命令或同一体的预充电命令及触发停止命令中止。

5、触发写

触发写命令与猝发读命令类似,允许某个体中的一行被激活后,连续写入若干个数据。第一个写数据与触发写命令同时在数据线上给出,以后每个时钟节拍给出一个新的数据,输入缓冲在触发数据量满足要求后停止接受数据。触发写操作可以被触发读/写命令或DQM数据输入屏蔽命令和预充电命令或触发停止命令中止。

6、自动刷新

由于动态存储器存储单元存在漏电现象,为了保持每个存储单元数据的正确性,HY57V561620必须保证在64ms内对所有的存储单元刷新一遍。一个自动刷新周期只能刷新存储单元的一个行,每次刷新操作后内部刷新地址计数器自动加“1”。只有在所有体都空闲(因为4个体的对应行同时刷新)并且未处于低功耗模式时才能启动自动刷新操作,刷新操作执行期间只能输入空操作,刷新操作执行完毕后所有体都进入空闲状态。该器件可以每间隔7.8μs执行一次自动刷新命令,也可以在64ms内的某个时间段对所有单元集中刷新一遍。

7、自刷新

自刷新是动态存储器的另一种刷新方式,通常用于在低功耗模式下保持SDRAM的数据。在自刷新方式下,SDRAM禁止所有的内部时钟和输入缓冲(CKE除外)。为了降低功耗,刷新地址和刷新时间全部由器件内部产生。一旦进入自刷新方式只有通过CKE变低才能激活,其他的任何输入都将不起作用。给出退出自刷新方式命令后必须保持一定节拍的空操作输入,以保证器件完成从自刷新方式的退出。如果在正常工作期间采用集中式自动刷新方式,则在退出自刷新模式后必须进行一遍(对于HY57V561620来说,8192个)集中的自动刷新操作。

8、时钟和时钟屏蔽

时钟信号是所有操作的同步信号,上升沿有效。时钟屏蔽信号CKE决定是否把时钟输入施加到内部电路。在读写操作期间,CKE变低后的下一个节拍冻结输出状态和猝发地址,直到CKE变高为止。在所有的体都处于空闲状态时,CKE变低后的下一个节拍SDRAM进入低功耗模式并一直保持到CKE变高为止。

9、DQM操作

DQM用于屏蔽输入输出操作,对于输出相当于开门信号,对于输入禁止把总线上的数据写入存储单元。对读操作DQM延迟2个时钟周期开始起作用,对写操作则是当拍有效。

-

FPGA

+关注

关注

1629文章

21729浏览量

603048

发布评论请先 登录

相关推荐

辅助电源的工作原理

串行接口的工作原理和结构

VCO的工作原理是什么

DDR SDRAM的工作模式和特点

SDRAM的特点与应用

SDRAM的发展经历和工作原理

DDR SDRAM和SDRAM功能及结构差异

简谈 SDRAM的工作原理

简谈 SDRAM的工作原理

评论