为了实现异步电路在实际应用中的低功耗、高性能特性,提出了一种基于单通道通讯协议的高速异步流水线控制单元和一种使用Muller C单元的高鲁棒性的QDI(quasidelay insensitive)异步流水线控制单元。第1种异步流水线控制单元采用独立的正反向响应电路,使得比近期提出的超高速异步流水线控制单元GasP电路的正向响应减小了50%的信号翻转。该电路使用TSMC 0.25μmCMOS工艺实现,HSPICEinterwetten与威廉的赔率体系 结果表明与GasP电路相比正向响应时间减少38.1%.可以工作在2.2GHz;第2种控制器与流行的QDI异步控制器STFB(single-track full-buffer)电路相比.以较少的面积代价,实现了时序验证上的极大简化。

异步电路因其具有低功耗、高性能和低电磁干扰的特性,正受到越来越多的关注。异步流水线是异步电路实现的主要形式,从而得到广泛研究,实用的异步流水线结构也被不断提出,例如在文中提出的超高速异步流水线控制单元GasP电路,在文中提出的准延时无关QDI异步流水线控制单元WCHB(weak condition half buffer)、PCHB(precharged fullbuffer),以及在文中提出的基于单通道通讯协议的QDI异步流水线控制单元STFB。

提出一种基于单通道通讯协议的高速异步流水线控制单元,与文中GasP电路的正向响应需要4次信号转换相比,该控制单元的正向响应只需要2次信号转换,从而大大减小了流水线的正向响应时间。同时,为了简化时序验证,另一种具有更强鲁棒性的QDI异步流水线控制单元被提出,该控制单元很好地解决了STFB控制单元高的功耗和面积消耗问题。

1 GasP电路与STFB电路

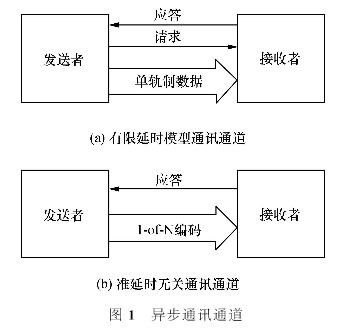

典型异步电路系统由一系列相互通讯的模块组成,在这些模块之间需要基于异步握手协议的通讯通道来完成数据交换,本文根据通讯通道的延时模型将其分为有限延时通讯通道和准延时无关通讯通道,图1给出了这两种类型的通讯通道。

其中图la中给出的有限延时的通讯通道,由于采用单轨制编码方式,可以有效的复用现有同步电路单元,并且在很大程度上节约了面积。但是有限延时模型决定了请求信号与数据有效之间存在复杂时序关系,在物理设计时,时序验证是一项复杂的工作。准延时无关通讯通道如图lb所示,该通道采用1-of-N的编码方式,此种编码使用冗余码,数据本身包含数据有效信息,不需要请求信号指示数据有效,这样也就有效避免了请求信号与数据有效信号之间复杂的时序关系。准延时无关通讯通道有效地简化了时序约束并易于实现异步电路的平均延时,但是,由于其需要检测数据有效,势必会引入额外的延时。

与同步电路相比,异步电路需要实现发送者和接收者之间的握手协议,因而会引入额外的延时、功耗以及面积的代价,如何设计有竞争力的控制器实现握手协议是异步电路设计的关键。

1.1 GasP电路

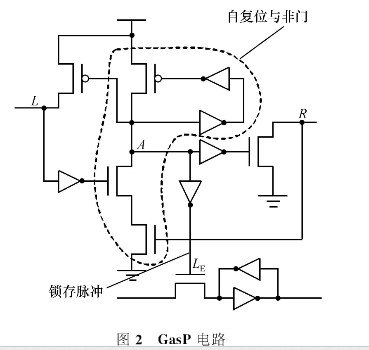

GasP电路作为高速异步流水线控制器被提出,图2给出了GasP电路的基本结构,通过逻辑努力电路优化之后,图中每一次信号翻转的延时相等。

初始化之后,节点L、 R和A均为高电平,当前一级电路准备好数据时,节点L将被设成低电平,此时自复位与非门的输出发生翻转,节点A被驱动到低电平,经过一级反相器,节点LE变为高电平,此时数据通过锁存器传输到下一流水级。当节点A电平为高后,节点L通过上拉的PMOS恢复到高电平,经过两级延时,节点R被驱动成低电平。在A为低电平后两个门延时,自复位与非门的两个输入为低电平,因此,自复位与非门的输出将自行恢复到高电平。在这一状态下,如果前一级电路再次将L驱动成低电平,自复位与非门的输出不会再次发生翻转,直到后一级电路完成对当前锁存数据的处理,将R重新设置成高电平。

正向响应时间定义为节点L变低到节点R变低过程中的信号转换次数。反向响应时间定义为节点R变高到节点L变高过程的信号转换次数。根据以上定义,GasP电路的正向响应时间为4次信号转换,而反向响应时间为2次信号转换。异步流水线的输入到输出的响应时间由流水级的正向响应时间决定,因此,Gasp电路获得高的吞吐率的同时,是以大的响应时间为代价的。当Gasp电路各级门的延时失配时,存在直流电流,从而引入了额外的功耗,并减慢了节点A由低向高的翻转速度。同时,GasP电路不利于实现准延时无关电路,在电路物理设计时,复杂的时序验证是不可避免的。

1.2 STFB电路

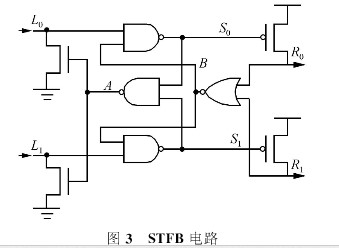

异步流水线控制器STFB电路由Ferretti M和Beerel P A提出,其电路结构如图3所示,其采用双轨制编码实现准延时无关异步通讯。

工作过程如下:初始化以后,节点L0、L1、R0、R1以及A均为低电平,节点B为高电平;一旦前一级电路准备好数据,L0和L1其中一个设置成高电平,这里假设L0被前一级电路设置成高电平,这时通过与非门S0节点设置成低电平。当S0为低时,节点A和节点R0被驱动成高。节点A变高以后,L0和L1被重新拉回到低电平,这标志着前一级电路可以发送新的数据。当R0变高以后,B节点由高电平变成低电平,防止S0、S1节点被再次拉高,直到后一级电路处理完Ro、R1上的数据,将R0设置成高电平之后,B节点重新回到高电平,新的数据才允许被再次传送到下一级。

从图3不难得出,STFB控制器的正向响应需要2次信号翻转,而反向响应需要4次信号翻转,一个周期的信号翻转次数与GasP电路一样,都是6次。当一个流水线的输出受限时,流水级的反向响应将影响其性能,同时在实现宽数据通路的流水线时,STFB电路需要与数据宽度一致的控制器个数,因此在STFB实现时,需要较大的功耗和面积代价。

2 低响应时间特性的异步流水线控制器

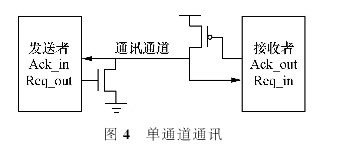

图4给出了基于单通道异步握手协议通讯通道结构,

从图中可以看出,信号Ack_in和Ack_out总是反相的,因此在同一控制器中,从Ack_in到Ack_out需要奇数次反相,从Req_in到Req_out也需要奇数次反相。此外Req_out和Ack_out有效的条件是Req_in为低电平并且Ack_in为高电平,因此Req_in和Ack_in两个信号在进行与非操作或者或非操作前必须有一个信号需要先做一次反相。在设计控制器时,若由同一电路产生Req_out和Ack_out时,则从Req_in到Req_out或者从Ack_in到Ack_out路径中必有一条路径存在3级反相门,也就是说,正向响应或者反向响应需要4次信号转换(Req_out和Ack_0ut到通讯通道还有一次信号反相)。

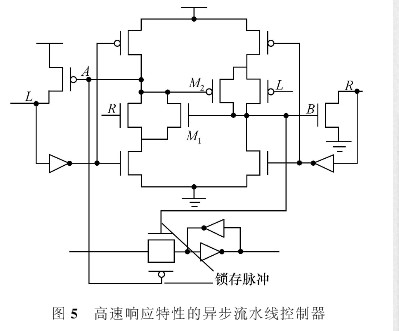

为了减小正反向响应信号翻转的次数,将信号Req_out和Ack_out信号的产生电路分开,图5就是基于这一思想提出的一种新的具有低响应时间特性的异步流水线控制器。

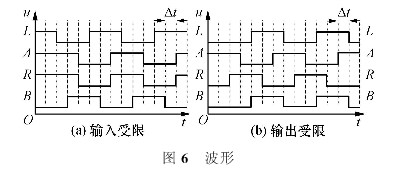

下面具体介绍该控制器的工作过程:在初始状态时,节点L、R和A均为高电平,节点B为低电平,此时晶体管M1、M2截止。当前一级电路将L节点驱动为低电平时,经过一级门延时,节点B被驱动成高电平,经过两级门延时节点A被驱动成低电平,节点R被驱动成低电平。在节点A为低以后,L节点通过PMOS管重新被拉成高电平,表示前一级电路可以发送新的数据。当R为低电平后两个门延时,B节点被重新驱动成低电平,同样在L为高电平后两个门延时,A节点重新回到高电平;当A是高电平,B是低电平时,L和R节点浮空,该流水级处于等待前一级的请求信号和后一级的应答信号状态。图6a给出了以上描

的输入受限(即请求信号晚于应答信号)的信号转换情况,而图6b是输出受限(即应答信号晚于请求信号)的信号转换情况。为了使在输入受限和输出受限两种不同情况下,节点A和节点B充放电时间都为3个门延时,如图5所示,加入了M1和M2管,以确保A、B信号在这两种情况下具有相同的脉宽。

上述异步流水线控制器的正反向响应都只需要2次信号翻转,与GasP电路相比,减小了50%的正向响应信号翻转次数。同时在设计GasP电路中,必须小心选择晶体管的尺寸,以保证每一级门的延时完全一致。如果各门延时出现失配,GasP将不能正常工作。而本文提出的控制器由于产生信号Req_out和Ack_out不再共享同一电路,使得在节点L被拉高之前节点A不会被拉高,同样,在节点R被拉低之前节点B不会被拉低,这样就消除了门延时失配导致电路失效的情况。

3 准延时无关异步电路控制

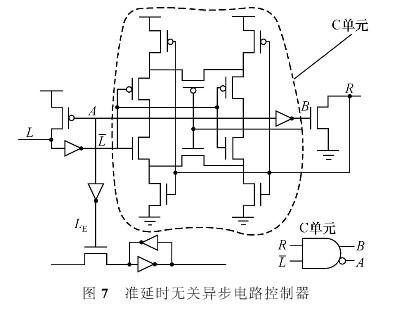

为了实现准延时无关异步流水线,提出第2种控制器。图7给出高鲁棒性的单通道异步控制器,该控制器使用Muller C单元代替第1种控制器中的与非门。对于一个基本的2输入Muller C单元,当其输入都为高时输出为高,其输入都为低时输出为低,其他情况,输出保持不变,图7中所示的MullerC单元是带有互补输出的。

与第2节描述的第一个控制器类似,初始化以后,L、R和A为高电平,B为低电平,Muller C单元输出保持不变;一旦L节点被前一级电路设置成低电平,Muller C单元的输出将发生翻转,A节点变成低电平,B节点变成高电平;随后,L翻转成高电平,R变成低电平;当L为高,R为低以后,Muller C单元的两个输入都为低,Muller C单元将再次发生翻转,A节点为高,B节点为低,此时L和R节点浮空,该流水级处于等待前一级的请求信号和后一级的应答信号状态。

当L变低以后,该控制器需要经过3次信号转变才能将L恢复到高电平,同时,其前一级电路在检测到R为高后,同样需要3次信号转换才能将R节点变低。该控制器与GasP电路一样需要6次信号翻转来完成一个周期的操作,同样该控制器的正、反向响应时间也与GasP电路一致,分别为4次和2次信号转换。但是由于Muller C单元的逻辑努力要大于自复位与非门,因此该控制器在获得高鲁棒性的同时牺牲了一定的性能。

4 模拟结果

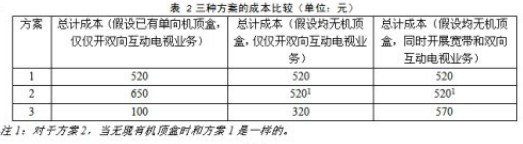

使用TSMC O.25 μm逻辑工艺库对文中的4个电路进行如下Hspice模拟:反相器的尺寸分别为Wp=1.4 μm,Wn=0.6μm,其他逻辑门的尺寸选择以与反相器具有相同驱动能力为原则,输出级MOS的尺寸为反相器管子尺寸的两倍。在GasP电路中,自复位与非门中PMOS管尺寸为Wp=2.8μm,STFB电路或非门中NMOS管的尺寸为Wn=0.9μm。表l给出了4个控制器的模拟结果,

可以看出,与GasP电路相比,第1种控制器的正向响应时间减小了38.1%,而相对于STFB电路,第2种准延时无关控制器的吞吐率增加了15.3%。如果使用脉冲逻辑代替图5中的复杂逻辑门,第1种控制器将在具有和GasP电路几乎相同吞吐率的情况下,正向响应时间却仅为GasP电路的79.1%。

5 结 论

本文提出了两种新型的基于单通道通讯协议的高速异步流水线控制器。第1种控制器正向只需要两次信号翻转,模拟结果显示其正向响应时间与最具有竞争性的GasP电路相比减少了38.1%,使用TSMCo.25μm的工艺库模拟,该电路可以工作在2.2GHz。同时,为进一步简化时序验证而提出的第2种使用Muller C门的QDI单通道异步流水线控制器,与流行的准延时无关电路STFB相比其面积代价大为减少,并且吞吐率提高了15.3%。

-

控制器

+关注

关注

112文章

16356浏览量

177991 -

驱动

+关注

关注

12文章

1840浏览量

85287 -

协议

+关注

关注

2文章

602浏览量

39221

发布评论请先 登录

相关推荐

FPGA中的流水线设计

现代RISC中的流水线威廉希尔官方网站

周期精确的流水线仿真模型

FPGA重要设计思想及工程应用之流水线设

流水线ADC

如何选择合适的LED生产流水线输送方式

嵌入式_流水线

CPU流水线的问题

了解流水线型ADC

采用单通道通讯协议设计高速异步流水线控制器STFB电路的设计

采用单通道通讯协议设计高速异步流水线控制器STFB电路的设计

评论