前几天搞数学建模好几天没更新文章了,大家没忘了我吧,赶紧发一篇。

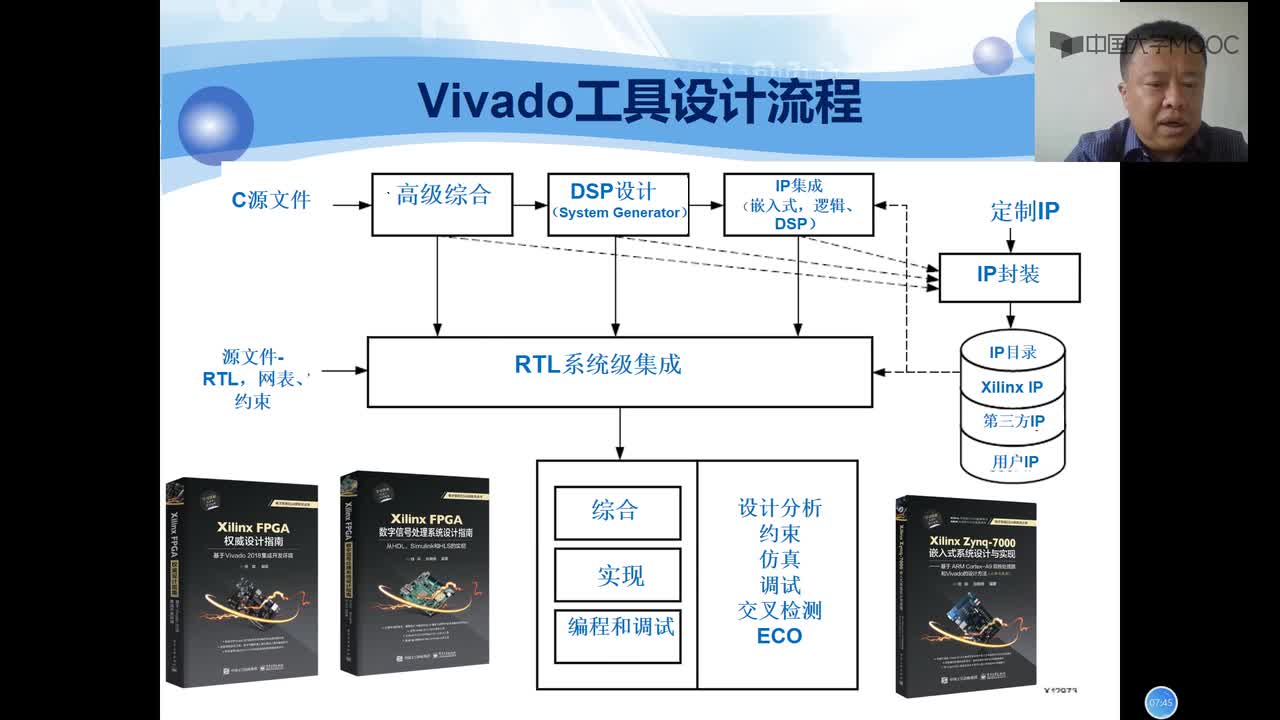

在有了电路设计的概念的之后我们可能苦于不能灵活运用Verilog去对电路进行描述。然后苦于到处找资料,这里我们告诉你们一个非常好的Verilog实例描述学习工具,Vivado。

不知情者:呀,Vivado不是FPGA的设计EDA工具嘛?用它还能来来学习Verilog描述,你确定?

答:是的,你没听错,可以的。这个Vivado工具就是这么体贴。

1. 打开Vivado工具,随便先新建一个工程。然后进入下页面。

2. 在界面最上面一行菜单栏找到 “Tools”,点击 Tools-> Language Templates

3. 点击 Tools-> Language Templates后,出现如下界面。可以看到,这里有Verilog,VHDL, systemVerilog, XDC,Debug的语言模板。这里我们先只看Verilog。

4. 将上图中的Verilog栏展开,在Synthesis Constructs栏就是我们可综合的常见Verilog描述。可以看到 Always ,Conditional里的case,条件选择赋值语句,if-else等常见的语法模型他都列出来了。在Coding Example里面有一些基础的电路模块的Verilog描述示例。

5. 展开Coding Example,可看到基础的电路,如累加器,基础算术电路,逻辑门,输入输出端口,比较器,计数器,解码器,常见的数字信号处理电路,译码器,寄存器(flip flops),逻辑移位器,Misc(有七段式数码管驱动,同步电路,防抖电路, 开漏输出端口,脉冲调制电路),多路选择器,RAM,ROM,移位寄存器,状态机,三态缓冲器等等的Verilog描述示例。

6. 在Example Module里面有更多的设计示例,如一些算法电路的设计。有了一些基础之后,就可以把这里的设计示例都看看。

对于初学者可以好好利用这个。把上面这些示例模板和示例设计学习仿真一遍。主要是将Verilog描述与电路对应起来,在Vivado里面可以使用Schematic,把Verilog描述的电路原理图显示出来。后面我们也会以这个为资料发一些文章。

原文标题:使用vivado也能学习Verilog设计,你造吗

文章出处:【微信号:LF-FPGA,微信公众号:小鱼FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

EDA工具

EDA Tools in FPGA

基于多种EDA工具的FPGA设计

使用VIVADO对7系列FPGA的高效设计心得

赛灵思推出首个基于机器学习优化算法 FPGA EDA 工具套件

赛灵思Vivado ML版优化应用设计

【FPGA Vivado】基于 FPGA Vivado 的流水灯样例设计

智多晶EDA工具HqFpga软件实用小功能

Vivado不是FPGA的设计EDA工具嘛?

Vivado不是FPGA的设计EDA工具嘛?

评论