1.引言

在现代雷达系统中,含DSP电路板应用很广,含DSP电路板通常是以某种DSP芯片为核心,外围配以双口RAM(DRAM)和闪存(Flash)等器件。DSP芯片大多支持IEEE1149.1标准,并且在电路板中形成了边界扫描链,支持边界扫描。本文采用边界扫描威廉希尔官方网站 与传统的外部输入矢量测试方法相结合,为含DSP电路板的测试与诊断提供了可以借鉴的方法。

2.电路原理简介及总体测试思想

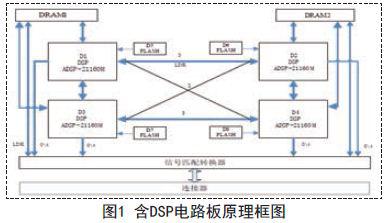

2.1 电路原理介绍

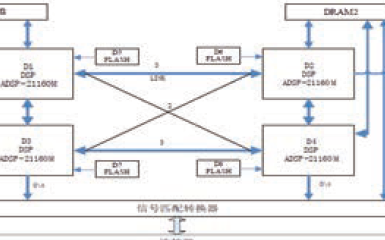

本文以雷达系统中某含DSP电路板为例对测试方法进行介绍,该电路以AD公司的ADSP-21160M为核心,外加DRAM、Flash、信号匹配转换器组成,Flash为DSP工作提供配置程序,4个DSP之间通过Link口进行数据交换,同时DSP的部分数据线和地址线与DRAM的数据线和地址线相连,DSP的Link口通过信号匹配转换器与外部连接器进行数据交换。该电路板在电路器件构成上使用了集成度较高的器件,芯片封装采用了PQFP132、PLCC100等多种表贴器件,器件引脚间距极小,采用探笔测试可能破坏电路工艺;并且电路上的DSP芯片不能从电路板上取下,所以采用边界扫描威廉希尔官方网站 较为合理。如图1所示。

2.2 测试与诊断分析

对电路中核心器件DSP的资料分析,芯片具有JTAG测试接口,具备边界扫描测试的条件。但边界扫描测试不是基于IP内核的测试,使用边界扫描威廉希尔官方网站 可以对电路测试但无法达到全面的测试与诊断,所以可以利用与传统的外部输入矢量测试方法相结合的方式实现电路的互连以及器件功能的测试,达到故障定位的目的。

2.3 测试系统组成

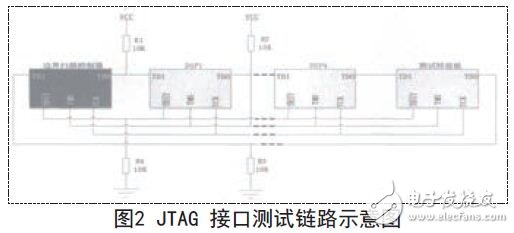

根据测试与诊断需求、测试工具以及电路本身的特点,设计稳压电路、JTAG测试接口转换电路以及加入一片具有边界扫描功能的芯片(FPGA)构成的电路实现了对电路测试所需的资源。

*稳压电路。稳压电路对测试系统程控电源发送过来的电压进行滤波、稳压后提供被测板的工作电压,保证被测板电源不会因为意外的原因产生突变。

*FPGA电路。该部分电路为被测板提供测试的地址和数据信号,测试时使用系统平台上的边扫控制器将被测电路板上DSP的测试链路的JTAG口与适配板上的FPGA的JTAG口构成一个测试链路,实现4个DSP之间互连测试、DSP与连接器连线测试、通过对FPGA配置程序实现FPGA与DSP间互连线测试。

*JTAG测试接口转接电路。将被测板上的DSP与测试转接板上的FPGA的JTAG接口构成一个测试通道,形成一个边界扫描测试链路。如图2所示。

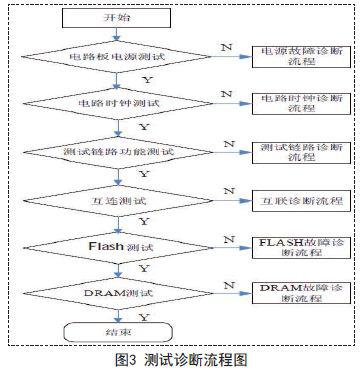

3.测试与诊断流程开发

基于边界扫描威廉希尔官方网站 的测试诊断流程开发主要内容包括对边扫器件链路设计、引脚映射关系设置、边界扫描控制器相关文档设置,以及测试脚本语言的开发。图3是该电路板的测试诊断流程图。

*测试链路功能测试。实现对边扫器件构成的测试链路的连接情况进行测试,以及完成边扫器件引脚输入输出功能是否正常测试,只有在测试链路测试通过后才能使用边界扫描控制器进行后续测试。

*互连测试。依据被测板电路原理图和测试转接板原理图的网表文件,通过边界扫描测试软件实现对被测电路板上的边扫器件(DSP)、测试转接板上FPGA共五个器件间两两互连线的是否出现开路、短路、虚焊等问题的测试。

*Flash测试。被测电路板上的每个Flash的控制使能信号由不同的器件进行控制,在对Flash的测试过程中需要开发针对各Flash测试与诊断的测试脚本,在测试的过程中完成对故障的分析和定位,开发的测试脚本能够定位到器件的具体引脚故障。

*DRAM测试。通过连接器发送DRAM配置程序的触发信号,FPGA产生DRAM的读写时序,对DRAM的读写功能进行测试,FPGA读写的测试结果进行判读并生成一定的测试结果数据由连接器采集至测试系统,判断该部分电路功能是否正常。

按照上述开发过程实现的测试诊断流程的故障覆盖率≥83%,故障检测率约为92%,隔离到3个器件以内的故障隔离率≥95%.

4.总结

通过在测试转接板上放置具有边界扫描功能的芯片将该芯片与被测板上的边扫芯片构成测试簇,传统的外部输入矢量测试弥补了边扫测试的不足,进而实现了较高的电路测试覆盖率。

-

dsp

+关注

关注

553文章

7987浏览量

348790 -

DRAM

+关注

关注

40文章

2311浏览量

183451 -

连接器

+关注

关注

98文章

14488浏览量

136451 -

雷达

+关注

关注

50文章

2930浏览量

117473

发布评论请先 登录

相关推荐

数字电路板自动测试与故障诊断威廉希尔官方网站 的研究

基于边界扫描的电路板测试系统

边界扫描测试威廉希尔官方网站 在带DSP芯片数字电路板测试中的应用解析

柔性电路板的主要测试方法

针对含DSP电路板的测试方法与诊断分析

针对含DSP电路板的测试方法与诊断分析

评论