引 言

目前国内急需一种能够对电火工品的发火过程进行实时无损耗监测的方法和手段,并根据监测结果对火工品的可靠性进行准确的判决和认证,解决科研和生产过程中的具体问题。本系统采用感应式线圈作为非接触式启爆电流的启爆装置,并采用高速A/D、FPGA、DSP等先进的集成电路实现了电火工品的无损耗检测。其主要目的是:第一,解决电火工品可靠性试验中微秒级瞬态信号的检测、处理和存储威廉希尔官方网站 ;第二,为可靠性试验提供一种在线的无损耗实时检测系统,以便对电火工品的发火全过程进行监测;第三,为电火工品的发火可靠性认证和*估提供真实的*价依据,减少或杜绝因拒收产品而出现经济方面的风险,同时也可减少或杜绝因错误地接收产品而出现武器装备质量方面的隐患。

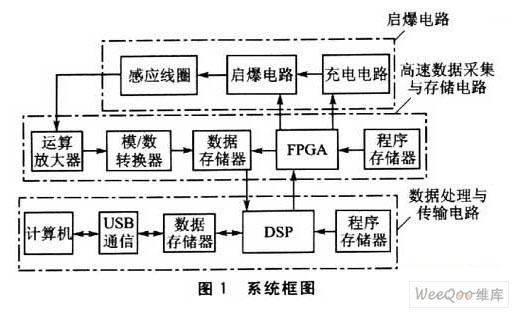

1 系统组成

整个系统的组成如图1所示。当启爆电路在DSP和FPGA的控制下启爆时,感应线圈取出启爆电流,首先是高速数据采集与存储电路,以FPGA为核心,对数据进行高速采集与存储。数据存储完毕,FPGA发信号告知DSP采集完毕,开始对采集的数据进行相关的处理。DSP对信号处理的内容:首先对信号滤波,然后进行必要的时域和频域分析,提取相关的信号特征,包括持续时间、信号带宽、峰值、功率、能量等。处理完的数据通过USB口传送到计算机,继而进行专业的相关分析。这里如果采用高速DSP进行数据采集,对于DSP的运算能力是一种浪费。而在高速数据采集方面,FPGA有单片机和DSP无法比拟的优势。FPGA时钟频率高,内部时延小;全部控制逻辑由硬件完成,速度快,效率高.因此有图1所示的系统组成。

2 硬件电路

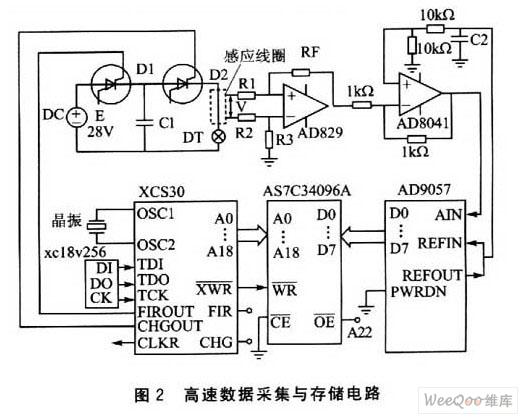

2.1 高速数据采集与存储电路

为了能够对作用时间为μs级的电火工品的启爆电流进行实时监测,采用了由一些大规模集成电路芯片构成的高速数据采集与存储电路,如图2所示。

电火工品无损耗检测的主要内容是对启爆电流的测量。

电火工品的启爆电流作用时间为μs级。XCS30是Xilinx公司基于SRAM威廉希尔官方网站 的FPGA芯片,由它发出指令对电容Cl充电并启爆电火工品DT。非接触式感应线圈作为启爆电流的探测装置,取出电压。前端调理电路一是扩大可测信号的幅度范围,设置放大器,对小信号进行放大,以保证足够的动态范围;二是为了不给被测信号带来影响,输入端应有较高的输入阻抗。在实验中测到的电压带有噪声,于是通过滤波器将噪声滤掉。但这样处理以后,信号的驱动能力下降,以至于A/D不能正确地采样,于是加了一级跟随器,增强驱动能力,这样A/D就可以正确地采样了。

XCS30的主要任务是:④控制可控硅D1的导通,使电容器C1充电;②控制可控硅D2的导通,使电火工品启爆;③在D2导通的同时,启动A/D转换,以实现A/D采样与启爆信号的同步;④产生地址信号,将A/D输出的数据存储到SRAM中;⑤判断SRAM的存储空间是否已满,以便结束A/D采样,并输出CLKR信号,通知图3所示的数据处理与传输电路,读取SRAM中的数据。其中①与②两项任务是在DSP的控制下进行的,如同3所示,即XCS30接收到DSP的指令后才能完成上述两项任务。DSP经过XCS30而控制Dl和D2导通的原因,是为了提高负载的驱动能力。也就是说,XCS30的驱动能力比DSP强,可以可靠地使可控硅Dl和D2导通。

实际使用时,数据采集与存储电路所达到的主要性能是:①采样速率达到40 Msps,即采样间隔25 ns;②存储器容量为512KB;③被采样信号的最大持续时间为12.8 ms。

被采样信号因为检测对象的不同而持续时间有μs级的也有ms级的,因此采样频率不能一成不变。经过分析,最小采样频率为5 MHz,最大采样频率为40 MHz。而FPGA外接晶振的频率为40 MHz,应该对它进行8分频。外接一个两位拨动开关,“00”时对应采样频率为40 MHz,“11”时对应的采样频率为5 MHz。

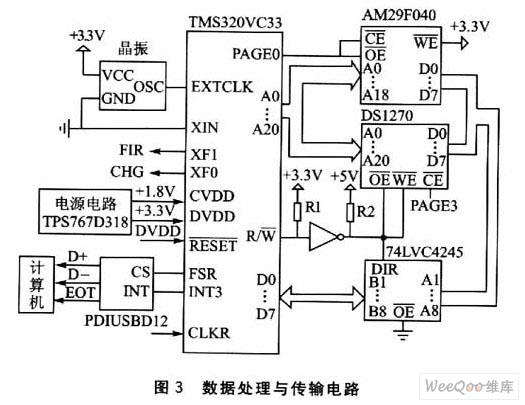

2.2 数据处理与传输电路

TMS320VC33是图3所示电路的核心器件,其主要功能是:①读取图2所示SRAM的数据。电路上的连接关系是,TMS320VC33的A19选通AS7C34096A的输出使能信号OE,DSP的地址线A0~A18及数据线DO~D7分别与SRAM的Ao~A18及数据线D0~D7相接。②对读取的数据进行处理,包括必要的时域和频域分析,主要是大数据量的FFT。③通过串行接口芯片将采集和处理后的数据传输到计算机。

DSl270是一种非易失性的存储器。其输出电压高电平为5 V,但TMS320VC33的I/O口电平为3.3 V,不能承受高电平为5 V的TTL信号。为了使TMS320VC33与DSl270能交换数据,采用74LVC4245实现3.3V和5V的电平转换。74LVC4245同时具有3.3 V和5 V两种供电电源,与DSP相连的I/O脚电平为3.3V,与DS1270相连的I/O脚电平为5 V。

由于TMS320VC33片内设有ROM,掉电后程序和数据信息都将遗失,因此需要外接存储器。这里选用Flash芯片AM29F040存储程序,用DS1270存储数据处理过程中及过程后的数据。电源芯片TPS767D318产生3.3V和1.8 V的电压给DSP供电;上电后,TPS767D318的复位脚将产生一个低电平,此信号同时将DSP复位,DSP将程序从程序存储器引导到高速RAM区后开始全速执行。数据进入DSP,DSP对数据进行处理,即进行必要的时域和频域分析,提取相关信号特征,将处理后的结果再放回DSl270。

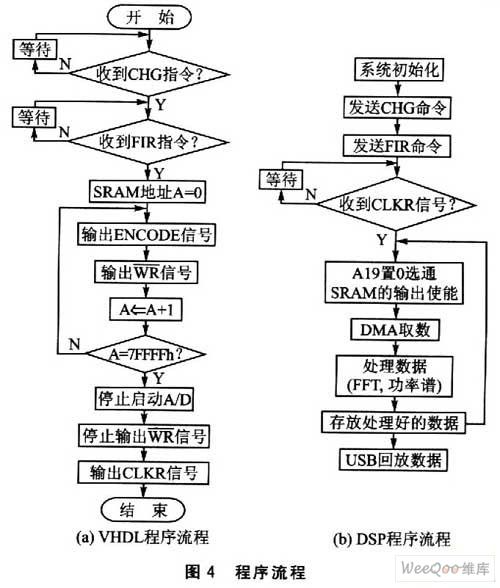

3 软件设计

图2所示电路的核心器件是XCS30,前述5项功能是通过VHDL实现的,其流程如图4(a)所示。图中CHG和FIR分别是发给XCS30,并使其发送对电容Cl充电和启爆电火工品DT的指令;ENCODE是启动A/D转换的信号;WR是写SRAM的信号,地址值A=7FFFFh表示SRAM已满。这时XCS30输出CLKR信号,表明采样和存储过程已经结束。

图4(a)分为4个功能模块:产生发火信号、分频器、频率选择器、地址分配器。图4(b)为DSP程序流程。

编写VHDL程序并在ISE7.1中的仿真波形如图5所示。

4 小 结

DSP的优势有:数据处理能力强,高速度运算,能实时完成复杂计算,单周期多功能指令,丰富的串口资源。利用DSP强大的数据处理能力和高运行速度的优势,可以提高分析系统的精度和实时性,满足监测系统的更高的性能要求。由于将DSP与FPGA等高新的芯片运用到该系统中,一片可以实现许多功能,蹦此减少了使用的其他器件,精简了主板系统;特别是增加功能比较方便,只需修改软件。这样,相对降低了整个系统的成本,而且增强了整个系统的性能。

-

dsp

+关注

关注

553文章

7966浏览量

348531 -

FPGA

+关注

关注

1628文章

21696浏览量

602504 -

芯片

+关注

关注

454文章

50548浏览量

422590

发布评论请先 登录

相关推荐

利用FPGA和DSP实现信号检测系统设计

利用FPGA和DSP实现信号检测系统设计

评论