1 引言

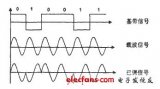

交错正交相移键控(OQPSK)是继QPSK之后发展起来的一种恒包络数字调制威廉希尔官方网站 ,是QPSK的一种改进形式,也称为偏移四相相移键控(offset-QPSK),有时又称为参差四相相移键控(SQPSK)或者双二相相移键控(Double-QPSK)等。它和QPSK有同样的相位关系,也是把输入码流分成两路,然后进行正交调制。与普通的QPSK比较,交错正交相移键控的同相与正交两支路的数据流在时间上相互错开了半个码元周期,而不像QPSK那样I、Q两个数据流在时间上是一致的(即码元的沿是对齐的)。OQPSK信号中,I(同相)、Q(正交)两个数据流,每次只有其中一个可能发生极性转换。所以每当一个新的输入比特进入调制器的I或Q信道时,输出的OQPSK信号中只有0°、±90°三个相位跳变值,而根本不可能出现180°相位跳变。所以频带受限OQPSK的信号包络起伏比频带受限QPSK的信号小,经限幅放大后频带展宽得少,故OQPSK性能优于QPSK。

本设计中OQPSK解调器接收端接收的信号是10.7MHz已调信号,按照软件无线电的设计思想,先进行计算机的interwetten与威廉的赔率体系 仿真,充分利用FPGA的特点,成功实现了对的10.7MHz的OQPSK信号差分解调。解调器的威廉希尔官方网站 指标为:解调器输出码:256 kb/s 、TTL电平;解调器输出时钟:256 KHz 、占空比50%。

2解调器的设计与FPGA实现

2.1总体方案设计

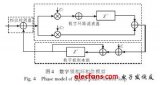

解调器前端的载波恢复部分采用分离元件实现,这里不做详细介绍,大家可以参考经典锁相环电路进行设计。位时钟信号可以由I路信号提取也可以由Q路信号来提取,本设计中由I路信号来提取。并串变换之后就完成了信号的解调。后边的HDB3编码是为了便于传输和其他处理,比如解调后的信号送计算机处理等等。

2.2位时钟恢复电路的设计

位时钟恢复电路由高稳定度振荡器(晶振)、分频器、相位比较器和控制器所组成。其中,控制器包括扣除门、附加门和“或门”。高稳定度振荡器产生的信号经整形电路变成周期性脉冲,然后经控制器再送入分频器,输出位同步脉冲序列。若接收码元的速率为F(波特),则要求位同步脉冲的重复速率也为F(赫)。这里,晶体的振荡频率设计在nF(赫),由晶振输出经整形得到重复频率为nF(赫)的窄脉冲,经扣除门、或门并n次分频后,就可得重复频率为F(赫)的位同步信号。如果接收端晶振输出经n次分频后,不能准确地和收到的码元同频同相,这时就要根据相位比较器输出的误差信号,通过控制器对分频器进行调整。调整的原理是当分频器输出的位同步脉冲超前于接收码元的相位时,相位比较器送出一超前脉冲,加到扣除门(常开)的禁止端,扣除一个a路脉冲,这样,分频器输出脉冲的相位就推后1/n周期(3600/n);若分频器输出的位同步脉冲相位滞后于接收码元的相位,晶振的输出整形后除a路脉冲加于扣除门外,同时还有与a路相位相差1800的b路脉冲序列加于附加门。附加门在不调整时是封闭的,对分频器的工作不起作用。当位同步脉冲相位滞后时,相位比较器送出一滞后脉冲,加于附加门,使b路输出的一个脉冲通过“或门”,插入在原a路脉冲之间,使分频器的输入端添加了一个脉冲。于是,分频器的输出相位就提前1/n周期。经这样的反复调整相位,即实现了位同步。

接收码元的相位可以从基带信号的过零点提取(它代表码元的起始相位),而对数字信号进行微分就可获得过零点的信息。其中codein输入端输入的是I路信号,clkin输入的是32.0867M的时钟信号,Clkout输出同步信号。FredivN分频器的分频倍数为64倍。

其中codein输入端输入的是I路信号,clkin输入的是32.0867M的时钟信号,Clkout输出同步信号。FredivN分频器的分频倍数为64倍。

2.3 差分译码电路的设计

差分译码完成的功能就是把相对码变为绝对码。绝对码是以基带信号码元的电平直接表示数字信息。如高电平表示“1”,低电平表示“0”;相对码(差分码)是用基带信号码元的电平相对前一码元的电平有无变化来表示数字信息的,假若相对电平有跳变表示“1”,无跳变表示“0”,由于初始参考电平有两种可能,因此相对码也有两种波形,但是不论是那种形式解码方式都是一样的。现假设{an}和{bn}分别表示绝对码和相对码序列,则差分译码器的功能可表示为:an =bn bn-1,其中 表示模二加。

其中b为相对码,a为绝对码,clkin为为同步信号时钟。

2.4 并串变换电路的设计

A、B两路128kb/s的并行输入信号分别接到数据选择器74153的两个数据输入端,其中B路信号落后A路信号半个码元周期。256KHz的位同步信号经分频为128KHz作为数据选择器的一路地址选择信号,另一路地址选择信号接地。这样数据选择器输出为A、B两路信号的并路信号,即A1、B1、A2、B2、A3、B3……,速率为256kb/s。

2.5 HDB3编码器的设计

2.5.1编码规则

HDB3码是AMI码的改进型,称为三阶高密度双极性码.他克服了AMI码的长连0串现象.

HDB3码的编码规则:

① 将消息代码变换成AMI码;

② 检查AMI码中的连0情况,当无4个或4个以上连0串时,则保持AMI码的形式不变;

若出现4个或4个以上连0串时,则将1后的第四个0变为与前一非0符号(+1或-1)同极性的符号,用V表示(+1记为+V,-1记为-V).

③ 检查相邻V符号间的非0符号的个数是否为偶数,若为偶数,则再当前的V符号的前

一非0符号后的第一个0变为+B或-b符号,且b的极性与前一非0符号的极性相反,并使后面的非0符号从V符号开始再交替变化.

2.5.2建模思想

本设计没有象其他设计那样将插V补B分开实现,而是通过变量的设置将两个功能一起实行。

首先判断前面已存在非0符号的极性,用以判断后面非0符号的极性。同时通过变量flag的状态判断前面是否已经插V,若已经插V则再通过变量H的状态判断两个V之间的非0符号的个数,为偶数且后面连续输入4个以上连0时则插B,为奇数时则不插B。若尚未插V则不补B。插V和插B的功能由两个3位移位寄存器的强制输出实现,当不需要插V和B的时候则移位寄存器顺序输出。

本设计在实现过程中将插入的V和B根据需要直接由+1和-1表示,省去了其他程序中先插入V和B然后再判断极性的过程。输出部分由两路表示,当aout和bout分别为0和1时表示输出-1,为1和0时表示输出+1,为0和0时表示输出0。限于篇幅这里就不给出程序清单。

3 部分试验结果

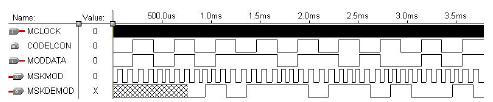

系统加入调制部分后的仿真结果如下图7所示。其中indata为调制器的输入信号,DATAOUT为解调输出,outa2和outb2为DATAOUT的HDB3编码结果。OUTCLK为最后的输出时钟。

4 结论

随着FPGA威廉希尔官方网站 的发展,大规模FPGA的容量在不断增大,价格不断下降,这使得集成复杂的算法成为可能。用它将实现连续相位OQPSK解调所需的大部分功能封装于其中,将有利于通信系统实现小型化和集成化,并可提高系统的稳定性。另外,由于FPGA器件具有可编程性,可以很方便地进行系统升级和修改,以满足不同应用场合的需要。忧无线SOC开发平台豪华的单片机开发系统S3C44B0 ARM7 开发板无忧S3C2410 ARM9开发板单片机以太网开发板Mini ARM Debugger无忧单片机实验开发板无忧单片机学习板 无忧无线nRF-9E5模块。

-

FPGA

+关注

关注

1629文章

21729浏览量

603059 -

解调器

+关注

关注

0文章

286浏览量

25812 -

计算机

+关注

关注

19文章

7490浏览量

87877

发布评论请先 登录

相关推荐

解调器

LoRa™调制解调器相关设计操作

一种基于FPGA的全数字短波解调器设计

全数字QAM解调器方案采用了载波相位和符号定时的联合估计环——基于FPGA的同步电路设计与实现研究 精选资料分享

基于FPGA的OQPSK解调器的设计与实现

一种全数字BPSK解调器的设计与FPGA实现

基于FPGA的MSK调制解调器设计与应用

一种全数字BPSK解调器的设计与FPGA实现

基于FPGA的MSK调制解调器设计与应用

采用TMS320F206控制的同步调制解调器

基于FPGA的全新数字化PCM中频解调器设计

基于FPGA的BPSK调制与解调器设计

采用FPGA威廉希尔官方网站

如何设计OQPSK解调器

采用FPGA威廉希尔官方网站

如何设计OQPSK解调器

评论