在过去几十年中,数字设计人员一直依赖逻辑分析仪,作为系统检验的主要工具。近年来,时钟速率的加快,已经迫使设计人员考虑系统所有部分的信号完整性,包括测试能力。逻辑分析仪探头不再能够任意连接到系统上,就能够保证成功,而是必须考察探头位置、负荷及与传输线的邻近程度等因素。本文考察了在探测高速数字系统时设计人员遇到的部分常见问题,另外本文还讨论了探头的负荷模型及探测位置的影响。最后,本文讨论了把探头连接到高速系统最常用的威廉希尔官方网站 :短线探测和阻尼电阻器探测。

逻辑分析仪探头的负荷模型

任何类型的探头的目标都是尽可能对系统提供最小的电负荷。如果探头对系统性能的变动太大,那么探头将不能帮助设计人员检验系统,因为故障原因可能完全是由探头引起的。隔离故障对有效检验故障非常重要。因此,设计人员必须能够预测探头对系统的影响,而不管其是可以忽略不计,还是占主导地位。

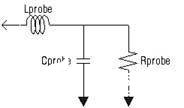

预测被探测的系统性能的最精确方式是在系统interwetten与威廉的赔率体系 中包括一个探头负荷模型。逻辑分析仪厂商提供RLC电路,直到预定的频率(通常是6 GHz)建立探头负荷模型。模拟不仅提供了最精确的探头影响模型,而且它们提供了一种方式,可以改变变量,监测每个变量的影响。这些变量包括探头在传输线上的位置和/或从传输线到探针的探头短线长度。一般来说,逻辑分析仪的探头负荷模型如下:

图 1. 简化的逻辑分析仪探头负荷模型

在较低频率上,电阻器会主导探头阻抗,对目标的影响最小。这是因为探头阻抗一般在20k ,而目标一般在50 - 75 。两个阻抗并联,会产生最接近的目标阻抗。在频率提高时,探头开始引入电容,其阻抗开始滚降。一旦阻抗达到目标阻抗的数量级上,来自探头的反射会成为重要问题。

在超高频率上,探头会引入电感,阻抗将提高。探头负荷的电容和电感特点会形成谐振。逻辑分析仪探头的目标是尽可能提高谐振的频率。此外,谐振的阻抗应尽可能高。如果探头阻抗下降到10-20 范围内,探头将分流出目标系统较高的频率成分。对每种探头形状,厂商将提供精确的负荷模型及阻抗与频率关系曲线。

为迅速估算探头的影响,可以使用集总电容探头模型。逻辑分析仪探头厂商对每种探头形状提供了估算的集总电容。在使用等效集总电容时,可以确定时间常数,支持端接电阻或传输线的阻抗。然后可以在系统时间常数的RMS之和中使用这种等效电容。一旦确定整体系统时间常数,可以把其转换成上升时间和带宽,预测探头对系统整体系统的影响。

探测位置的影响

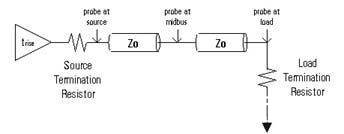

由于探头是电路的一部分,而电路又是探头的一部分,因此可以预测两个感兴趣的点上的影响 (即接收机和探针)。探头的影响中一个主要变量是其在目标传输线上的位置。通过其在传输线上的相对位置,可以确定探头导致的反射。反射影响的严重程度取决于目标系统(即轨迹长度、端接方案、电压余量等…)。图2是一个标准传输线系统,其中列明了连接逻辑分析仪探头的最常用位置。

图2. 标准传输线的电路拓扑结构

[图示内容:]

Probe at source: 在信号源上探测

Probe at midbus: 在中间总线上探测

Probe at load: 在负荷上探测

Source Termination Resistor: 源端接电阻器

Load Termination Resistor: 负荷端接电阻器

负荷端接系统

在负荷端接系统中,负荷端接电阻器仅用于传输线设计中。引入的反射被吸收到接收机上的端接电阻器中。如果这些反射和入射波或后续波同时到达,它们本身会表现为上升时间劣化或码间干扰(ISI)。在把逻辑分析仪探头连接到系统上时,探头将表现为电容不连续点。把探头插入这类系统中的最佳位置是信号源。首先,探头反射会即时发生在驱动装置上。然后这种反射会再次反射离开低阻抗驱动装置,并与入射波一起沿着传输线传送。收到的波形会经历上升时间劣化,但二次反射最小。其次,为降低电容负荷对系统的影响,探头形成的RC时间常数应尽可能低。不能改变探头的电容,但时间常数的电阻/阻抗取决于探头的位置。通过在信号源插入探头,时间常数的电阻/阻抗是低阻抗驱动装置与传输线阻抗的并联组合。这种组合在系统中产生了最低的电阻/阻抗,进而产生了最低的RC时间常数。

源端接系统

在源端接系统中,仅使用图2中的源端子。入射波在源端接电阻和传输线阻抗之间进行幅度划分。半幅度波传导到接收机上,在这里,其被100%正反射。这种反射本身会与入射波叠加在一起,产生驱动装置的原始幅度。反向传导反射会传回驱动装置,然后它被吸收到源端接电阻器中。源端子采用相应的结构,使得在除接收机之外的传输线任何位置上,观察到的波形都呈现出梯级形状。通过把其与用户定义的门限电压(通常以电压摆幅为中心)进行比较,逻辑分析仪确定被探测的信号是‘1’还是‘0’。这意味着如果逻辑分析仪探头位于直接接收机之外的任何地方,都将观察到这种梯级波形形状。在波形位于摆幅中间的时长内,逻辑分析仪将不能确定逻辑电平。这直接影响着分析仪的定时性能。对源端接系统,逻辑分析仪探头的位置应尽可能接近接收机。

双端接系统

在双端接系统中,传输线中同时使用源电阻器和端接电阻器。在这种系统中,由于源端接电阻器和负荷端接电阻器形成的电阻分路器,只有一半的原始信号会到达接收机。逻辑分析仪探头一般会放在这类系统上任何地方。主要考虑因素是探头的RC时间常数。但是,在系统的任何位置上,电阻/阻抗将是线路特性阻抗的? (即50?//50?)。由于在探针上只能观察到一半的原始电压电平,设计人员必须保证满足逻辑分析仪的最小电压摆幅规范。

短线探测

短线探测是指探针不能直接放在目标的传输线上。探针和目标信号之间敷设的轨迹长度称为短线。短线可以由PCB轨迹、导线或连接器引线组成。由于PCB上的布局限制,很难避免短线探测。问题是探针离传输线的距离必须有多近、同时仍能在系统和逻辑分析仪中实现可以接受的性能?

在谈论传输线时,使用的经验法则也适用于逻辑分析仪短线。经验法则取决于系统上升时间。对逻辑分析仪,建议短线的电长度不超过系统上升时间的20%。对小于系统上升时间20%的电长度,可以把短线视作阻尼电阻,而不是分布式传输线。但是,在短线长度提高时,电容会大幅度提高。在某一点上,电容会超过探头的总电容。 下面的实例说明了特定上升时间可以接受的最大短线长度。这一实例使用150ps/英寸的传播速度,这在FR4介电PCB中非常典型。对标准50 , FR4微带传输线,单位电容一般是每英寸3pF。

实例

Trise= 150ps, Tstub=(150)*(0.2)= 30ps Length=(30)/(150)=0.20“ Cstub=(0.2)*(3p)=0.6pF

Trise= 250ps, Tstub=(250)*(0.2)= 50ps Length=(50)/(150)=0.33” Cstub=(0.33)*(3p)=1.0pF

Trise= 500ps, Tstub=(500)*(0.2)= 100ps Length=(100)/(1500)=0.67“ Cstub=(0.67)*(3p)=2.0 pF

Trise= 1000ps, Tstub=(1000)*(0.2)= 200ps Length=(200)/(150)=1.33” Cstub=(1.33)*(3p)=4.0pF

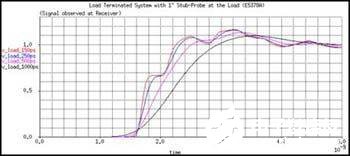

如果我们看一下通过1“短线连接到传输线负荷上的逻辑分析仪探头,我们可以说明上面的实例。下图说明了在探测负荷时1”短线探头对负荷端接传输线的影响,其中显示了四个上升时间。150ps、250ps和500ps上升时间把1“短线视为不可接受,而1000ps上升时间则能够正常运行。从这一图中可以明显看出,1000ps上升时间的特点要明显好于150ps上升时间。

图3. 在负荷上使用1”短线探头时,负荷端接系统接收机上的信号

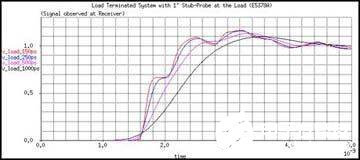

下图说明了1“短线探头探针上的信号。再次可以明显看出,1000ps上升时间的特点要好于150ps上升时间。

图4. 负荷端接系统探针上的信号,在负荷上使用1”短线探头

这些图说明了在高速信号中,成功的逻辑分析必须考虑接收机和探针上的信号质量。

阻尼电阻器探测

很明显,在探针和被探测的系统之间增加一条短传输线会严重影响目标接收机和逻辑分析仪探针上的信号质量。在探针不能直接放在目标系统上时,改善探头和系统性能的方式之一是采用“阻尼电阻器探测”方法。通过直接在目标上插入一个阻尼电阻器,可以在探针上容忍更长的一段短线。阻尼电阻器有两种用途。首先,它把目标系统与短线探头的电容负荷隔开。此外,它消耗短线上的反射能量,从而使得逻辑分析仪能够观察到更清楚的信号。

为说明使短线长度达到最小的重要意义及阻尼电阻器的作用,看一下下面的实例。安捷伦科技的E5387A软接触逻辑分析仪探头通过长0.5“的短线连接到负荷端接系统上。通过使用信号完整性工具”Eye Scan“,可以绘制被探测信号的眼图,并在探针上直接查看眼图。被探测的波形是一个500Mb/s, 400mVpp 信号。左图说明了使用逻辑分析仪通过0.5”短线观察到的信号完整性。右图说明了在触点上插入一个125Ω阻尼电阻器时,逻辑分析仪观察到的信号完整性。

(通过0.5“短线观察到的眼图) (在短线前面使用125Ω阻尼电阻器)

图5. 在带和不带125Ω阻尼电阻器时,通过0.5”短线探测的信号Eye Scan图

这些眼图明确说明了阻尼电阻器对逻辑分析仪查看的信号的影响。在某个时点上,逻辑分析仪几乎不能使用信号。通过简单插入一个阻尼电阻器,信号质量得到改进,使得短线可以忽略不计。

在包含信号完整性工具(如安捷伦科技的“Eye Scan”)的现代逻辑分析仪中,探测威廉希尔官方网站 要更加重要。逻辑分析仪可以从模拟角度查看被探测的信号特点。为利用这种模拟信息,探头本身不得使显示的波形失真。如果可以使探头负荷达到最小,那么可以把产生的眼图视作系统中发生的情况的真实模拟表示。这为调试信号完整性问题提供了一个非常强大的工具。逻辑分析仪信号完整性工具的主要优点是,它能够在许多信道中同时进行模拟测量。通过使用Eye Scan及安捷伦科技最新的一套逻辑分析仪模块(16753A, 54A, 55A和56A),可以观察最多340个信号。这些新工具可以从全新的角度查看信号完整性及进行系统调试。但是,如上图所示,探测对成功的测量至关重要。

结论

本文说明了使用逻辑分析仪成功地探测高速数字系统的考虑因素。从本文中可以看出,探头在目标上产生了负荷,具体取决于探头固有的负荷及探头在传输线上的位置。我还说明了目标的拓扑结构和寄生信号会使探针上观察的信号完整性劣化。在使用逻辑分析时,这两个因素都应该考虑在内。

责任编辑:gt

-

电阻器

+关注

关注

21文章

3782浏览量

62134 -

隔离

+关注

关注

4文章

1295浏览量

32503 -

逻辑分析仪

+关注

关注

3文章

214浏览量

23172

发布评论请先 登录

相关推荐

逻辑分析仪的原理和应用

如何使用和选择近场探头?

逻辑分析仪的性能指标

逻辑分析仪工作原理

浅析逻辑分析仪的原理

探针没有可访问的探测位置

容易被忽略的逻辑分析仪探头

逻辑分析仪探头如何实现正确连接,需注意哪些问题

逻辑探头的使用注意事项

告诉逻辑分析仪探头的负荷模型及探头探测位置的影响

告诉逻辑分析仪探头的负荷模型及探头探测位置的影响

评论