引言

interwetten与威廉的赔率体系 电路中广泛地包含电压基准(reference voltage)和电流基准(current reference)。在数/模转换器、模/数转换器等电路中,基准电压的精度直接决定着这些电路的性能。这种基准应该与电源和工艺参数的关系很小,但是与温度的关系是确定的。在大多数应用中,所要求的温度关系通常分为与绝对温度成正比(PTAT)和与温度无关2种。

近年来有研究指出,当漏电流保持不变时,工作在弱反型区晶体管的栅源电压随着温度升高而在一定范围内近似线性降低。基于该特性,带隙基准源所采用的基极-发射极结可以被工作在弱反型区的晶体管代替产生低温度系数的基准源。文献中提到采用该设计原理的基准源,利用0.13μm工艺的低阈值电压NMOS管和衬底调整的PMOS管实现其中的放大器。本文所采用的基准源电路利用传统带隙基准源的核心电路原理,通过饱和状态MOS等效电阻对PTAT电流动态反馈补偿,基本实现了基准源的稳定要求。

1 带隙基准源的基本原理

带隙基准源可以在0~70℃的温度范围内有lO ppm/℃的温度系数。由室温下温度系数为-2.2 mV/℃的PN结二极管产生电压为VBE。同时也产生一个热电压VT(VT=kT/q),其与绝对温度(PTAT)成正比,室温下的温度系数为0.085 mV/℃,则输出电压为:

将式(1)对温度求导,用VBE和VT的温度系数求出理论上不依赖于温度的K值。为了达到所希望的性能,更详细地分析VBE与温度的关系是必须的。带隙基准就是将负温度系数的电压与正温度系数的电压加权相加来抵消温度对输出电压的影响。

1.1 负温度系数电压的产生

双极晶体管的基极-发射极电压具有负温度系数,或者说PN结二极管的正向电压具有负温度系数。从文献可得到与温度的关系式:

式中:η为与三极管结构有关的量,其值大约为4;α为与流过三极管的电流有关的一个量,当PTAT电流流过三极管时α为1,当与温度不相关的电流流过三极管时为0;T0为参考温度;VBG为硅的带隙电压。由式(1)可以看出VBE是一个具有负温度系数的电压。

1.2 正温度系数电压的产生

两个三极管工作在不同的电流密度下,它们的基极-发射极电压的差值与绝对温度成正比。如果两个同样的三极管(IS1=IS2),偏置的集电极电流分别为nI0和I0,并忽略他们的基极电流,那么:

式中:△VBE表现出正温度系数,而且此温度系数是与温度无关的常量。

1.3 一阶温度补偿带隙基准源

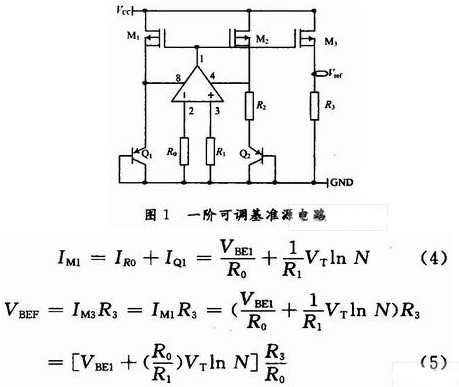

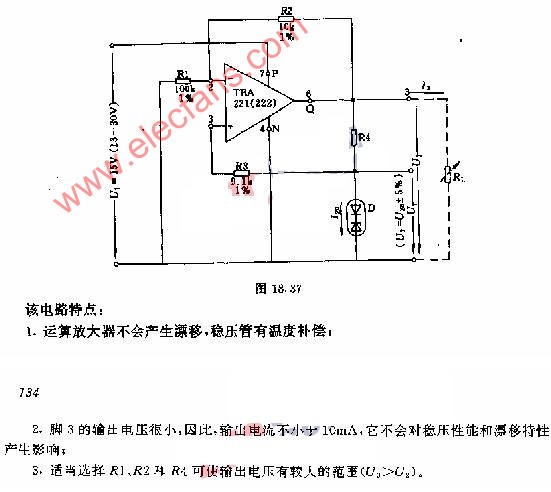

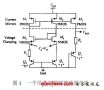

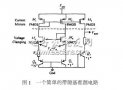

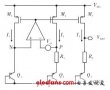

将正、负温度系数的电压加权相加,就可以得到一个近似与温度无关的基准电压。常见的一阶可调基准源电路如图1所示。

式中:N为Q2与Q1的发射结面积之比,式(4)中第一项具有负的温度系数,第二项具有正、负温度系数,合理设计R0与R1的比值和N的值,就可以得到在某一温度下的零温度系数的一阶基准电压。式(5)中方括号内是约为1.25 V的一阶温度无关基准电压,通过调节R2/R0的比值,可以得到不同大小的基准电压。

2 电路结构及原理分析

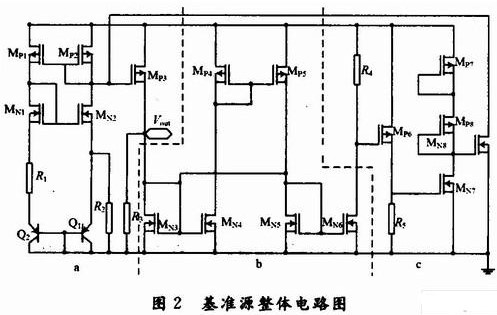

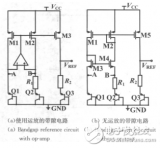

图2为本文设计的基准源整体电路图,包含带隙核心电路、反馈补偿电路和启动电路。其中虚框a为带隙核心电路,虚框b为偏置及反馈补偿电路,虚框c为基准源启动电路。

2.1 带隙核心电路

图2中,由Mp1~Mp3,MN1,MN2,R1,R2和Q1,Q2组成的电路构成带隙核心电路。输入晶体管的偏置电流由PMOS电流源提供,可通过减小其电流,而不是减小其宽长比来降低负载器件的gm,从而增加其差动放大增益。

其中Mp1,Mp2,MN1,MN2均工作在饱和状态,Mp1,Mp2复制了Iout,从而确定了IREF。从本质上讲,IREF被“自举”到Iout。选择一定的MOS管尺寸,如果忽略衬底沟长长度调制效应,则有Iout=KIREF,因为每个二极管连接的器件都是由一个电流源驱动的,故IREF和Iout与VDD无关,左右两支路永远维持这两个电流值。双极晶体管Q1和Q2工作在不同的电流密度下,它们的基极与发射极间的电压差与绝对温度成正比。将与电源无关的偏置电路与双极晶体管结合,得到带隙核心电路。

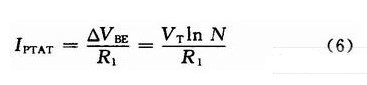

假设Mp1,Mp2和MN1,MN2均为相同的对管,将PTAT电流Ip3加到基极-发射极电压上,因此输出电流为:

PTAT基准电流IMp3PTAT(与绝对温度成正比)通过R3产生输出基准电压。

2.2 自偏置电路及反馈补偿电路

为了提高电源电压抑制,该设计对核心电路和运放的电源电压进行了调节,由MOS管的电流电压特性可知,当VDS≥VG-VTH时器件工作在饱和区,有:

因为栅漏短接,故MN3,MN5一定处于饱和状态,它们均可作为一个阻值由过驱动电压控制的等效电阻,定义MN3和MN5的等效电阻分别为RN3和RN5,则可将MN3与R3视为并联电阻Rx,如果Vout增大,则RN3减小,并联电阻Rx减小,从而使PTAT基准电流通过MN3分流一部分;同样原理适用于MN5和MN6,达到抑制补偿输出电压,使基准源输出电压稳定。其中Mp4和Mp5为MN3提供偏置电流,但使用这种“自偏置电路”会带来电路的启动问题。

2.3 启动电路

在基准源电路中需要启动电路使得系统上电时电路能够进入正常的工作状态,而自偏置放大器电路往往也存在启动问题。当电路处于非工作状况时,放大器的输入端电压初始值为零,而输出电压由于寄生电容的存在可能位于一个比较高的电势,当电源接通后不但放大器的偏置电路为截止状态,而且基准源的核心电路也无法正常启动。本文设计的启动电路则可以同时满足放大器和核心电路的启动要求,它由Mp6~Mp8,MN7,MN8,R4,R5构成。

当电源接通后,启动电路提供了放大器输出端到地的通路,从而拉低了核心电路中Mp1~Mp3的栅极电势,放大器的偏置电路开始工作,同时基准源的Mp1和Mp2支路中流过的电流也随之增大,使得放大器的输入端电势上升,这样放大器进入高增益工作区,带动基准源电路开始正常工作。

电路刚启动时,使Mp7和Mp8饱和,保证MN8栅极有足够高的开启电压,当MN8导通时,一个小的导通电流流过运放,启动带隙电路。电路开启后,虚框b部分电流镜像电路将输出电流进行镜像,给启动电路提供偏置,偏置电流使Mp6导通,从而MN7的栅极电压升高,MN7导通,由于MN8的电阻很大,导致MN7漏极电压很低,从而关断MN8,使启动电路(虚框c)两端电压降低而停止工作。

3 仿真结果与分析

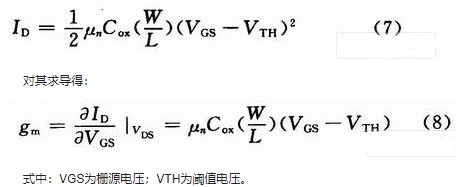

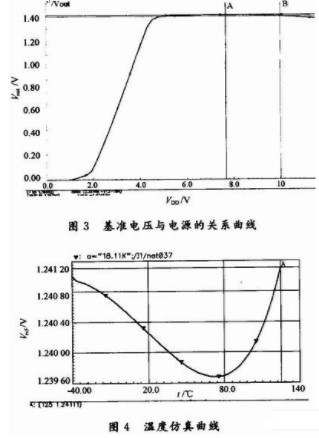

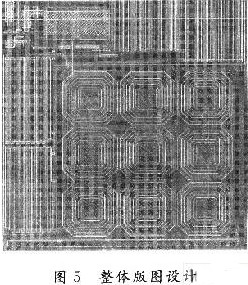

图3说明了该基准源对电压的抑制效果。根据仿真数据,在所取5~10 V的输出电压范围经计算基准电压电源抑制比为82 dB。图4为Cade-nce下的温度仿真曲线,根据所要求取的温度范围在-25~+120℃,计算得温度系数为:TCF=7.427 ppm/℃。图5为整体电路的版图设计,面积近似为0.022 mm2。

4 结语

本文通过对传统带隙基准源的基本原理分析,设计的基准电路工作电压为5~10 V,通过饱和状态MOS等效电阻对PTAT电流反馈补偿,得到了82 dB的电源电压抑制比和低于7.427 ppm/℃的温度系数,版图面积0.022 mm2。该电路产生的基准源电压基本满足普通应用要求。

-

CMOS

+关注

关注

58文章

5714浏览量

235468 -

放大器

+关注

关注

143文章

13589浏览量

213435 -

模拟电路

+关注

关注

125文章

1557浏览量

102732

发布评论请先 登录

相关推荐

基于CMOS工艺设计低温漂高PSRR带隙基准源

基于CMOS放大器实现带隙基准源电路的设计

基于CMOS放大器实现带隙基准源电路的设计

评论