1.引言

DDS频率合成器具有频率分辨率高,输出频点多,可达2N个频点(假设DDS相位累加器的字长是N);频率切换速度快,可达us量级;频率切换时相位连续的优点,可以输出宽带正交信号,其输出相位噪声低,对参考频率源的相位噪声有改善作用;可以产生任意波形;全数字化实现,便于集成,体积小,重量轻。

本文介绍了DDS的基本原理,同时针对DDS波形发生器的FPGA实现进行了简要介绍,利用SignalTapII嵌入式逻辑分析仪对正弦波、三角波、方波、锯齿波进行仿真验证。

2.DDS波形发生器的FPGA实现

FPGA的应用不仅使得数字电路系统的设计非常方便,而且它的时钟频率已可达到几百兆赫兹,加上它的灵活性和高可靠性,非常适合用于实现波形发生器的数字电路部分。使用FPGA设计DDS电路比采用专用DDS芯片更为灵活,只需改变FPGA中的ROM数据,DDS就可以产生任意波形,具有相当大的灵活性。

2.1 FPGA设计流程

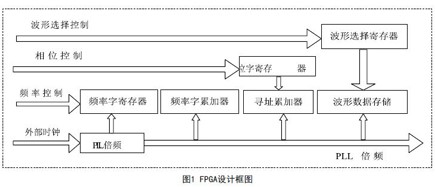

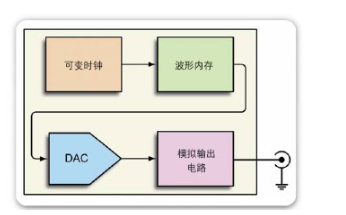

FPGA的设计框图如图1所示,FPGA的主要功能是:产生与外围电路的接口电路,使其能够接受外围逻辑控制信号;保存频率字,并构成相位累加器,产生与主时钟相同频率的RAM寻址字;用内部的存储块构成存放多种波形数据的ROM,并通过相应的控制线进行选择;构造出两个多波形选择输出的输出通道,其中的一路通道可具备移相功能;用内部的PLL倍频外部低频晶振,并输出与主时钟同频的时钟,驱动片外高速D/A.

2.2 时钟模块

根据耐奎斯特采样定理要得到输出频率为10MHz的信号,其所输入的信号时钟频率必须达20MHz以上。采样频率越高,输出波形的平坦度越好,同时波形的的采样点数也越多,那么获得的波形质量也就越好。本设计中的DDS模块是一高速模块,所以对系统时钟就有很高的要求,不仅需要有较高的频率,而且还要有非常高的稳定性,如果在FPGA的时钟端直接加一高频晶振,不仅时钟不稳定,而且功耗大,费用高,在本设计中,直接调用Altera公司的PLL核,在FPGA时钟端只需加一低频晶振,通过FPGA内部PLL倍频达到系统时钟要求,输出的时钟相位偏移在允许范围内。

2.3 DDS控制模块

(1)频率控制字输入模块

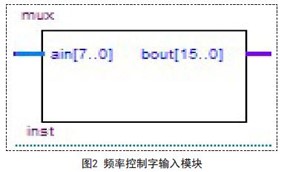

频率控制字输入模块如图2所示,数据选择器控制输入16位频率控制字。

(2)步进频率控制模块

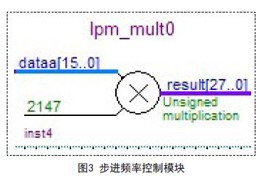

步进频率控制模块如图3所示,通过一个乘法器来控制步进频率,具体算法如下:f步进=fc*2147/232.

(4)相位寄存器

相位寄存器模块如图5所示,通过一个8位加法器跟8位寄存器构成相位寄存器并产生8位波形数据地址。

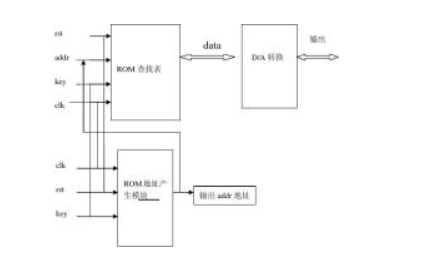

(5)波形存储器设计

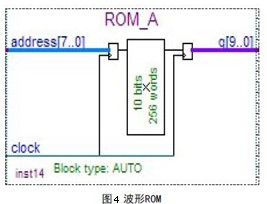

波形数据ROM就是存放波形数据的存储器,大多波形发生器产品都将波形数据存放在外部的ROM中,这样使得各部分结构清晰,测试、维护更加方便但由于ROM本身读取速度慢的缺点,使得整个系统性能下降,工作频率下降,为了解决以上问题,本设计使用的是用FPGA设计出ROM,在FPGA中存放波形数据,使用Quartus II9.0中的Mega Wizard Plug-In Manager来生成一个ROM,如图6所示。

Mega Wizard Plug-In Manager的设置,根据设计的要求,经过七步的设置,就可以生成一个ROM的IP核。当在波形ROM中固化所需波形的一个周期的幅度值后,由地址发生器产生的地址对波形ROM寻址,依次可取出送至D/A转换及滤波后即可得到所需的interwetten与威廉的赔率体系 波形输出。计算波形数据可以有两种方法:C语言与matlab计算。

3.仿真实验结果

按照第2节的系统设计,设计程序下载到FPGA芯片,使用QuartusII软件自带SignalTapII嵌入式逻辑分析进行仿真,观察信号波形图,正弦波如图7,三角波如图8。

4.总结

经实验结果表明,通过DDS威廉希尔官方网站 合成的波形具有良好的稳定性,易于控制和调节,利用FPGA能在很短时间内快速构建任意波形,提高了设计效率,具有实际应用价值。

-

FPGA

+关注

关注

1629文章

21735浏览量

603179 -

发生器

+关注

关注

4文章

1368浏览量

61691 -

DDS

+关注

关注

21文章

634浏览量

152649

发布评论请先 登录

相关推荐

基于DDS的任意波形/ 函数发生器之间的差别

基于DDS原理设计信号发生器的方案

基于DDS的波形发生器设计

基于FPGA的DDS波形信号发生器的设计

DDS多波信号发生器的实现

基于FPGA的DDS信号发生器设计方案解析

基于Verilog实现的DDS任意波形发生器

基于FPGA和DAC设计的dds发生器

采用FPGA器件实现DDS波形发生器的设计

采用FPGA器件实现DDS波形发生器的设计

评论