合成孔径雷达成像算法中较为成熟和应用广泛的算法主要有距离-多普勒(R-D)算法和线性调频变标(CS)算法。R-D算法复杂度相对较低,运算比较简单,虽然其成像质量并不高,但是相比对稳定性、存储空间、功耗与实时性要求都很高的实时SAR成像系统,其应用十分广泛。在整个有距离-多普勒(R-D)算法中方位脉冲压缩系统是设计的关键。随着FPGA芯片突飞猛进的发展,实时雷达成像方位脉冲压缩系统在FPGA上实现变成了可能。

1 脉冲压缩及方位脉冲压缩系统的结构

1.1 脉冲压缩的基本原理

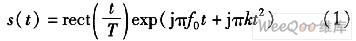

实现脉冲压缩必须满足两个条件:一是发射脉冲必须具有非线性的相位谱并且其脉冲宽度与有效频谱宽度的乘积》1;二是接收机中必须具有一个压缩网络,其相频特性应与发射信号实现“共轭匹配”。线性调频信号又称为Chirp信号,是广泛应用在信号处理领域的一种脉冲压缩信号。线性调频信号是具有矩形包络的宽脉冲信号,其特点是具有二次型的非线性相位谱和线性频率谱,即频率具有线性特性。一维线性调频信号的表达式为

其中,t为时间变量,T为线性调频脉冲宽度,f0为载频频率,k为调频斜率。信号的相位函数和频谱函数为

由式(2)可知,信号的调频斜率与时间成线性关系。

由于线性调频信号的以上特点,线性调频信号适合实现脉冲压缩,是一种典型的脉冲压缩方法:首先线性调频脉冲的相位谱是非线性的,具有较大的时间带宽积;其次匹配滤波器是在输入为确知信号加白噪声的情况下,得到最大输出信噪比的传递网络,满足压缩网络的条件。因此,采用匹配滤波器对信号进行滤波,得到输出信号最大的信噪比。

对线性调频信号进行脉冲压缩的基本原理可以总结为:对宽脉冲线性调频信号进行匹配滤波处理,使其能量集中,成为窄脉冲信号,从而获得线性调频信号大时间带宽积所对应的高分辨率。线形调频信号脉冲压缩具体实现是先把一维线性调频信号从时域转换到频域,再求其对应匹配滤波器的传递函数。匹配滤波器脉冲响应是信号的时间镜像复共轭,其时域表达式为

h(t)=C·s*(t-t0) (3)

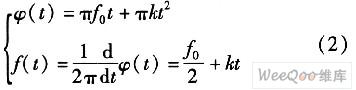

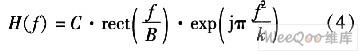

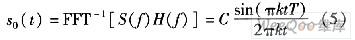

根据驻定相位原理,可以得到匹配滤波器的传递函数为

线性调频信号经过匹配滤波器完成脉冲压缩过程,输出表达式为

1.2 方位脉冲压缩系统的结构

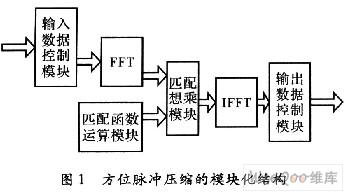

实现R-D算法中方位脉冲压缩的思路是先将信号经过FFT变换到频域,然后与匹配函数经过FFT后的结果进行匹配相乘,再经过IFFT得到压缩好的脉冲。在FPGA上实现时,应该包括输入\输出数据控制模块、FFT\IFFT模块、匹配函数运算模块、匹配相乘模块。数据流及各个模块的相互关系,如图1所示。

距离脉冲压缩的数据先进入输入数据控制模块,送入FFT运算模块,同时匹配函数运算模块进行工作,输出计算好的匹配函数,与FFT的输出结果同时送到匹配相乘模块中,相乘后的结果送入IFFT模块中,最后将IFFT的结果经输出数据控制模块进行输出。

2 方位脉冲压缩系统的FPGA设计

2.1 输入/输出控制模块

输入数据控制模块的主要作用是将数据送入FFT模块,同时给出FFT模块所需的控制信号,例如数据有效信号。数据流入数据控制模块时要做好缓存工作,保证其与FFT控制信号同步进入FFT模块。为了节省FPGA的资源,可以把相同功能的模块,如FFT/IFFT,进行复用。若FFT与IFFT模块复用,则应在输入模块中加入状态机来进行控制。状态1为无任何原始数据输入并且无IFFT运算的数据输入的状态;状态2为仅有原始数据输入而无IFFF运算的数据输入的状态;状态3为无原始数据输入但是有进行IFFT运算的数据输入的状态。状态机仅需要原始数据有效的使能信号与匹配相乘后数据有效的使能信号来进行控制即可。状态1代表了整个系统处于等待数据输入初始化的工作状态。状态2代表了原始数据进行FFT运算的工作状态。状态3代表了匹配相乘后数据进行IFFT的工作状态。

在FFT模块与IFFT模块复用的结构中,输出控制模块的作用是当匹配相乘的数据到来时,将其送入输入数据控制模块,再由输入数据控制模块送入FFT模块去完成IFFT运算;当计算出IFFT的结果时,输出数据控制模块直接将结果输出。实现上述功能,只需使用状态机即可,其工作原理与输入数据控制模块中的状态机类似

2.2 FFT/IFFT模块

在FFF/IFFT模块的设计上,为了提高设计的性能,增加设计的灵活性,采用Altera公司于2005年4月推出的版本号为2.1.3的FFT的IPcore进行FFT和IFFT运算。该IP core是一个高性能、高度参数化的,执行正向复数FFT与反向复数IFFT的FFT处理器。

2.3 匹配函数运算模块

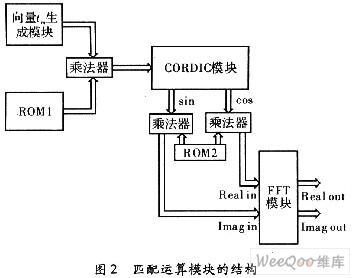

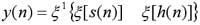

方位压缩的匹配函数为匹配函数再经过FFT变换到频域。在FPGA实现时要把interwetten与威廉的赔率体系 参量量化成离散的数字参量来进行处理。其中γm(RB),RB以雷达到场景中心线的距离Rs为参考进行数字量化,即每一个距离单元的RB=Rs+n deltaR,则RB相对每一个距离单元为常数。慢时间tm以脉冲重复时间1/PRF进行数字量化,相对于每一个方位单元为常数。在设计时,由于γm(RB)对于同一个距离单元来说为常数,所以可以把不同距离单元的γm(RB)按一定顺序存入一个ROM中,在处理不同的距离单元时读取相对应的γm(RB)。αr(tm)实现时用汉明窗。对于exp()采用CORDIC算法生成sin,cos来进行实现。若一个距离单元nan有个采样点,则向量由于PRF为常数,所以仅需设计一个产生向量[-nan/2:nan/2-1]2的模块,即每个时钟周期送出向量[-nan/2:nan/2-1]2中的一个数。匹配函数运算模块的框图,如图2所示。

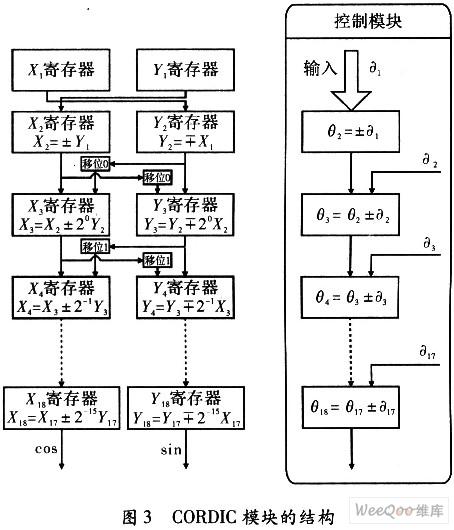

CORDIC模块的实现是匹配函数运算模块设计的重点。CORDIC(Coordinate Rotation Digital Com-puter算法即坐标旋转数字计算方法。主要用于三角函数、双曲线、指数、对数的计算。CORDIC模块采用18级流水线结构来实现,如图3所示。18级寄存器组中下一级寄存器中的输入数据是上一级寄存器的输出数据进行移位后相加或减组合得到的。进行加运算还是减运算完全由控制模块控制。控制模块的输入就是整个CORDIC模块的输入,即要进行sin,cos计算的角度э1。控制模块也采用流水线结构与18级寄存器组一一对应,达到对各级流水线的控制。18级流水线设计需要18个时钟周期来获取第一个计算结果,而只需要一个时钟周期来获取随后的计算结果。流水线结构的特点非常适合应用于方位脉冲压缩匹配函数运算的设计:首先,实时成像需要很高的数据吞吐量,这与流水线结构的优势相符合;其次距离单元的数据是随着时钟依次进入运算模块的,即一个时钟周期读人一个距离单元的数据,这与流水线结构的特点十分的吻合。采用流水线结构实现CORDIC算法,可以使匹配函数的数据在每个周期逐个输出,仅做好同步工作,使匹配函数的数据与距离脉冲压缩结果对应匹配相乘即可。

2.4 匹配相乘模块

匹配相乘模块主要完成的工作,是把距离脉冲压缩的数据经FFT后的结果与匹配函数对应相乘,再把相乘的结果送出。匹配相乘模块的核心是复数乘法器。复数乘法器是由4个普通乘法器和两个加法器组成。假设完成(a+bi)×(c+di)的操作,先分别计算a×c,a×d,b×c,b×d这4个实数与实数的乘法运算,再把减法运算a×c-b×d结果作为复数乘法器输出的实部,加法运算a×d+b×c的结果作为复数乘法器输出的虚部。

对数据的同步也是设计的重点。因为距离脉冲压缩经FFT后的数据与匹配函数的数据并不是同时进入匹配相乘模块。距离脉冲压缩经FFT后的数据较先进入,主要是因为匹配函数运算的CORDIC采用流水线结构,需要18个时钟周期来获取第一个计算结果而产生匹配函数数据的延迟。所以应该对匹配相乘模块对距离脉冲压缩经FFT后的数据进行缓冲。缓冲采用FIFO模块来实现。FIFO可以采用自带的IP core。

3 波形仿真与性能分析

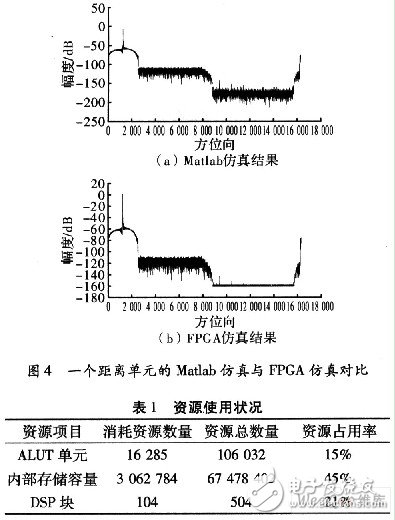

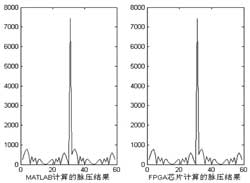

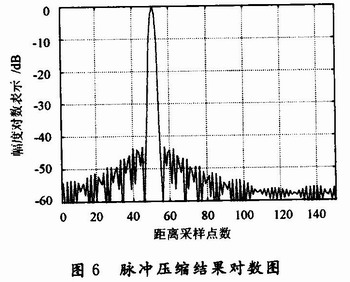

验证方法采用比对的方法,即单个目标点的仿真数据分别进行理论方位脉冲压缩仿真和基于FPGA的方位脉冲压缩仿真,并将得到的仿真结果进行比对。仿真数据中一个距离单元的点数为16 384点。验证过程是首先在。Matlab软件环境下对单个点目标的一个距离单元进行方位脉冲压缩的仿真,即理论仿真,然后再在Modelsim环境下对该距离单元进行方位脉冲压缩的FPGA仿真,并将得到的结果与Matlab下得到的理论结果进行比较。其比较的波形,如图4所示。

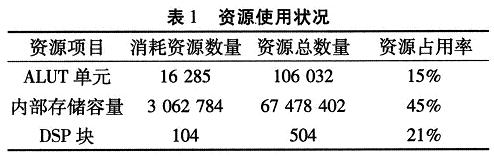

选用Ahera公司芯片EP2S130F780C5进行测试。稳定工作时时钟频率可以达到150 MHz。

4 结束语

方位脉冲压缩系统是这个R-D算法在FPGA实现的关键。文中给出的方案通过实验验证能够达到设计的要求。实验表明,随着可编程器件规模、速度的不断提高,采用FPGA实现高速数字信号处理的算法具有可行性和优越性。

-

FPGA

+关注

关注

1629文章

21729浏览量

603037 -

芯片

+关注

关注

455文章

50732浏览量

423247 -

雷达

+关注

关注

50文章

2930浏览量

117468 -

压缩系统

+关注

关注

0文章

9浏览量

7950

发布评论请先 登录

相关推荐

基于FPGA的雷达脉冲压缩系统设计

基于FPGA的数字脉冲压缩威廉希尔官方网站

基于FPGA的数字脉冲压缩系统实现

怎么设计基于XQ2V1000FPGA的数字脉冲压缩系统?

基于FPGA的雷达脉冲压缩系统该怎么设计?

基于FPGA的脉冲压缩仿真与实现

基于FPGA的雷达数字脉冲压缩威廉希尔官方网站

R-D算法与FPGA芯片实现雷达成像方位脉冲压缩系统的设计与仿真分析

R-D算法与FPGA芯片实现雷达成像方位脉冲压缩系统的设计与仿真分析

评论