脉冲压缩威廉希尔官方网站 是指对雷达发射的宽脉冲信号进行调制(如线性调频、非线性调频、相位编码),并在接收端对回波宽脉冲信号进行脉冲压缩处理后得到窄脉冲的实现过程。脉冲压缩有效地解决了雷达作用距离与距离分辨率之间的矛盾,可以在保证雷达在一定作用距离下提高距离分辨率。

线性调频信号的脉冲压缩

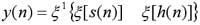

脉冲压缩的过程是通过对接收信号s(t)与匹配滤波器的脉冲响应h(t)求卷积的方法实现的。而处理数字信号时,脉压过程是通过对回波序列s(n)与匹配滤波器的脉冲响应序列h(n)求卷积来实现的。

依据式(1)的实现方法叫做时域相关法。根据傅里叶变换理论,时域卷积等效于频域相乘,因此,式(1)可以采用快速傅里叶变换(FFT)及反变换(IFFT)在频域内实现,称为频域快速卷积法。

用频域方法实现数字脉压,其基本原理是先对外部采样信号进行快速傅里叶变换(FFT)以求得回波信号频谱S(w),再将S(w)与匹配滤波器频谱H(w)进行乘积运算,最后对乘积结果进行快速傅里叶逆变换(IFFT)得到脉压结果Y(n),用公式表示为

(2)

(2)

频域快速卷积法的原理如图1所示,存储器中存储的是匹配滤波器传递函数H(k)。

图1 频域脉冲压缩原理框图

依据匹配滤波理论,数字匹配滤波器的脉冲响应h(n)及传递函数H(k)为

h(n)=s1(-n),H(k)=s1(k) (3)

其中, s(n)为雷达发射信号序列;S(k)为信号序列频谱。

数字脉冲压缩系统

1 系统构成和硬件设计

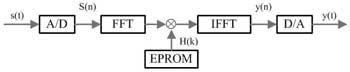

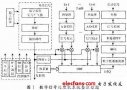

本系统是单脉冲雷达信号处理机的一部分,由于单脉冲雷达所需要处理的距离、方位/俯仰两路信号来自同一发射信号源的目标反射回波,要求对两路信号进行同时、同频ADC采样和完全相同算法的脉冲压缩处理。针对这一特点,雷达数字脉冲压缩系统将相同的脉冲压缩处理功能移至两片FPGA芯片内。由于对雷达体积、重量、功耗等指标有特殊要求,本系统采用二个通道的脉冲压缩处理硬件结构,即方位和俯仰两路信号分时共用一个脉冲压缩通道。雷达信号处理分系统硬件结构如图2所示。

图2 雷达信号处理分机硬件结构图

系统中,数据采样后分为和路和差路(包括航向差和俯仰差)两组数据,分别输入两片FPGA单独进行脉冲压缩计算,脉冲压缩后再送入后端的DSP做谱分析,以确定目标的距离、速度、方位等情况。由框图中我们看到,FPGA不仅要对数据做脉冲压缩计算,还承担了对输入数据处理和读写状态寄存器的任务。状态寄存器存储了脉冲压缩计算的控制参数,由后端的DSP根据分析的结果对其做相应的控制。

2 软件设计

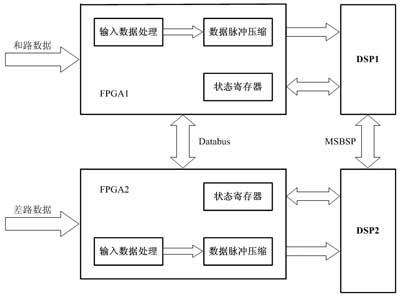

根据位内运算结构的特点,针对芯片内嵌的块RAM资源丰富的优势,脉冲压缩系统采用两片存储器的乒乓操作,在FFT的每一级运算中使一片双口RAM的两个端口同时处于读或写状态,达到每个时钟周期输出两个操作数的需要。而且,数据经蝶算单元运算结束后以相同的地址写入另一片双口RAM,节省了写地址生成的时间,为设计高速的FFT系统提供了可能。

如图3所示,采用两片中间级RAM:RAMA和RAMB,用它们来完成乒乓操作。地址产生模块生成的读地址同时与中间级的两片RAM相连,控制相应的RAM读取所需的操作数,操作数经蝶算模块运算后以同址方式写入到另一片RAM的两个端口。RAM的读写由地址产生模块生成的写使能信号控制,处于读状态的RAM写使能置零,而另一片的写使能端置高,处于写状态。而且,RAM被设置为写状态时输出端口不输出,以减少RAM的读取次数。这样,输入RAM变为输出RAM,输出RAM变为输入RAM,如此反复,直到FFT最后一级。

图3 脉冲压缩系统的结构框图

FFT的每一级运算结束后,两块RAM功能互换,写使能变反,运算结束。RAM的每次输出数据需经过数据选择模块(datamux),该模块由地址产生模块输出的当前级数信号Stage控制。本系统采用三种FFT模式:1024点、512点和256点,均采用同一旋转因子ROM。根据FFT点数的不同,ROM的读地址expaddr做相应的调整,这样的设计也在很大程度上节省了芯片内的块RAM资源。

3 系统性能

针对本雷达信号处理机对实时性和高精度的要求,我们设计研制出具有自主知识产权的高性能脉冲压缩处理系统,该处理系统具有以下特点:

A 处理系统内部采用24位自定制浮点数据格式,能够兼顾处理系统的资源占用和处理精度。数据输入为定点数据格式,输出为标准32位浮点数据格式。

B 处理系统工作时,需要依次完成FFT运算、复数乘法运算和IFFT运算。在进行FFT和IFFT运算时,蝶形运算/乘法运算单元完成蝶形运算操作;在进行复数乘法运算时,该单元完成乘法操作。这两种操作在实际工程中分时实现,并且共享浮点数规格化处理硬件电路。

C 处理系统中进行FFT/IFFT运算的长度N(N=2048、1024或512)由雷达信号处理机的控制信号决定。

D 内置三组数据存储器(输入数据RAM、同址运算RAM、输出数据RAM),保证处理系统能全速运行,提高该处理系统的处理能力。

E 旋转因子(N=1024时的FFT运算旋转因子)以上电初值的形式存储在FPGA片内存储器中。当N=512、256时,其旋转因子从N=1024的旋转因子中抽取得到。N点IFFT的旋转因子由N点FFT的旋转因子取共扼得到。实验结果

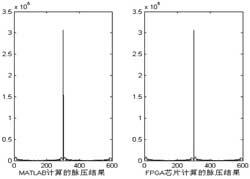

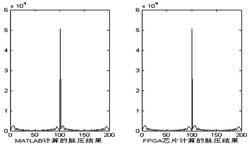

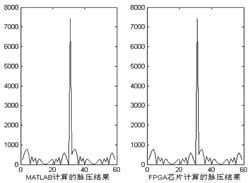

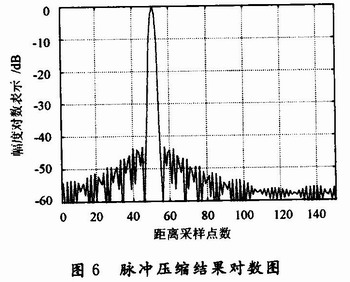

本雷达信号处理机存在三组时间—带宽指标,分别对其进行理论仿真和实际输出结果对照,其结果如图4、图5和图6所示。

图4 1024点脉冲压缩状态FPGA计算结果与MATLAB计算结果对比图

图5 512点脉冲压缩状态FPGA计算结果与MATLAB计算结果对比图

图6 256点脉冲压缩状态FPGA计算结果与MATLAB计算结果对比图

图4至图6分别对应时宽为60μs、20μs、6μs,带宽均为5M的线性调频信号。其中,左图对应MATLAB的计算结果,右图为FPGA芯片的输出结果。可以看到,FPGA芯片的输出结果和MATLAB仿真结果吻合。经测试验证结果良好,最大误差不超过-76db,在内部时钟频率80MHz条件下,完成1024点FFT 运行时间为146μs ,满足了雷达系统实时处理要求,达到了满意的效果。

-

滤波器

+关注

关注

161文章

7799浏览量

178010 -

存储器

+关注

关注

38文章

7484浏览量

163770 -

雷达

+关注

关注

50文章

2930浏览量

117468

发布评论请先 登录

相关推荐

基于FPGA的雷达脉冲压缩系统设计

基于FPGA的数字脉冲压缩系统实现

怎么设计基于XQ2V1000FPGA的数字脉冲压缩系统?

如何实现数字脉冲压缩系统?

基于FPGA的脉冲压缩仿真与实现

基于FPGA的雷达数字脉冲压缩威廉希尔官方网站

雷达信号处理机的脉冲压缩系统设计介绍

雷达信号处理机的脉冲压缩系统设计介绍

评论