1 引言

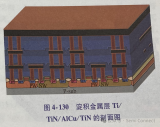

在 IC 工艺中,金属连线间的寄生电容除了取决于金属间距、金属厚度和连线宽度之外,还受金属连线间的介质的介电常数的影响。在金属刻蚀之后填充的介质材料(inter-metal dielectric)通常为二氧化硅,其介电常数介于 3.2~4.0 之间。随着工艺节点的进步,金属连线的线宽和间距越来越小,连线之间的寄生电容也越来越大,对电路性能的影响也随之增大。而金属线的厚度和连线之间的距离受工艺节点所限,一般不能够任意变动。所以要实现更小的寄生电容,需要改变填充介质材料,以便得到较低的介电常数。在已知的物质中,干燥空气的介电常数最低,可以借助在金属连线间形成空气隙的方式来降低金属间介质的整体介电系数[1]。由于金属连线间的寄生电容主要来自于在金属之间正对着的区域,边缘电容只占少比例。只需要在工艺制造过程中将空气隙形成于金属平板中间部分,其高度超过金属连线高度即可。

在已经量产的 0. 2μm RF-SOI 工艺中形成空气隙的方法是进行金属连线刻蚀,使金属之间形成相互间隔的沟槽。为了在金属连线之间形成尽可能大的空气隙,通常利用填充性能较差的 PEFSG 作为填充材料。为了阻挡 PEFSG 中 F 的穿透作用,还需要先填充一层富硅氧化层(SRO)作为阻挡层。SRO的填充性能和 PEFSG 基本相同。在 0.20 μm 的工艺中,可以满足要求。而在 0.13μm 工艺节点,当金属连线间距小于 0.18 μm以后,侧壁处的 SRO 阻挡层和 PEFSG 的厚度较薄,尤其在 Ti/TiN 台阶处对 Al的覆盖不够,并且还存在裂隙,会导致 PEFSG 中的 F 和金属 Al 接触反应,导致 Al 和 F 的生成物流动到空气隙中,引发金属连线短路(见图 1)。所以如何改善金属联线侧壁二氧化硅填充形貌是一个亟待解决的问题。

2 实验方案

在射频开管器件中,导通电阻和关断电容是衡量射频开管器件优良与否的关键参数。而后段金属连线之间的电容对整体的关断电容有直接影响[2,3]。

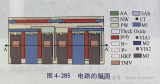

本文基于华虹宏力的 0.13μm RF-SOI 工艺平台,对射频开关器件中金属连线间的空气隙形成工艺进行了优化。射频开关器件为叉指结构设计,源区和漏区分别通过金属连线引出(见图 2)。开关器件源漏之间的总电容由两部分组成:分别是前段工艺中开关器件源漏电极与栅电极、源漏电极与衬底间的本征寄生电容,以及后段工艺中源漏金属连线之间的寄生电容。在前段工艺保持不变的情况下,改变后段金属连线间介质材料的填充工艺,测量得到的电容差异即为金属连线间寄生电容的差异。在下一小节中我们将具体研究不同的填充工艺与材料对空气隙的形成、以及最终对射频开关器件关断电容的影响。

3 实验结果与讨论

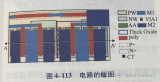

首先用 IC 工艺中常用的几种二氧化硅填充材料进行了实验,考量在不同金属连线间距处的填充性能(分别为 0.18μm和 0.46μm)。其中 0.18μm 的对应于0.13μm 工艺的最小设计规则,即最小金属连线间距,0.46μm 则对应于射频开关源漏端叉指结构的金属连线间距。具体试验分批方案参见表 1。

我们需要找到不同金属连线间距处填充一致性好的填充材料。也就是既要满足 0.46μm 金属间距处形成空气隙降低寄生电容,又不能使最小金属连线间距处台阶覆盖能力不足而导致侧壁保护不够,同时需要小心调整填充材料和厚度达到两者的平衡。对于更大的金属连线间距甚至无穷远的间距,由于空气隙没有实际作用,所以我们不予考虑。从图 3 可以看出,对沟槽的填充能力从强到弱为:HDP > PETEOS > PEFSG = PEUSG。PETEOS 填充能力明显强于 PEFSG和 PEUSG,并可以形成比较小的空气隙。而 HDP 由于是边填充边在沟槽两侧上方减薄的方式,导致填充能力过强,完全没有空气隙。所以我们考虑先一层较薄的 PETEOS,利用其较强的填充能力作为金属线侧壁保护层,然后填充 PEUSG,利用其较弱的填充能力形成空气隙。同时由于 USG 材料中不含 F 元素,还可以省略 SRO 阻挡层。

依据以上的实验结果,我们确定了用 PETEOS+ PEUSG 作为填充材料。由于 4 000 Å 的 PETEOS 在 0.18μm 和 0.46μm 的金属连线间距处已经将空气隙封口,后续再填充 PEUSG 已经无效。所以我们选择500 Å,1 000 Å,1 500 Å 和 2 000 Å PETEOS 作为实验对照。具体试验分批情况参见表 2。

从以上电子显微镜扫描照片可以看出增加 PETEOS厚度对金属连线侧壁覆盖能力改善明显。但是当PETEOS 厚度增加到 150 nm 甚至 200 nm 后,0.46 μm 金属连线间距的空气隙变小,并且抬高至金属连线上方,这样反而会使寄生电容增加。因此PETEOS 厚度介于 50 nm 和 100 nm 之间是比较理想的。我们最终选择了厚度为 70μm 的 PETEOS 用来改善金属连线侧壁覆盖形貌,厚度为 1 000 μm 的 PEUSG 用于形成空气隙。多片晶圆多点电学测试结果表明,并没有观察到满足最小设计规则的(0.18 μm )金属连线间出现短路现象。

最后我们将新的填充工艺应用在射频开关器件上,并测试了在关断状态下的 S12 参数,分批条件见表 3,测试结果见图 5。其中条件 1 为原来的填充工艺。由于 PEFSG 和 PEUSG 本身的介电常数有差别,也加入了 PEFSG 实验条件作为比对。从条件 2 和条件 3 的结果来看,使用 PEFSG和 PEUSG 填充对带有空气隙的金属互联电容基本没有区别。我们同时也可以看出条件 3 中 70 nm 的 PETEOS与 650 nm PEUSG 的组合对整体电容的影响小于 3%,对射频开关性能影响非常小。

4 结语

本文以射频开关器件的应用为背景,提出了在 IC工艺节点变小之后,在不影响性能的基础上改善金属连线侧壁填充的二氧化硅形貌的方法。通过分析和实验,改善了最小金属互联间距处由于二氧化硅覆盖不够导致的短路问题。同时射频器件源漏区域的大间距金属连线处空气隙仍然能高于金属高度。并且实测了新的填充工艺的金属互联电容与原有的工艺之间的电容值差异,得到了比较理想的结果。

参考文献

[1] B.Shieh,K.C.Saraswat,J.P.McVittie, S.List,S.Nag,M.Islamraja,R.H. Havemann.Air-gap formation during IMD deposition to lowerinterconnect capacitance[J].IEEE Electron Device letter,1998,19(01):16-18.

[2] R.Wolf,D.Wang,A.Joseph,A.Botula, P.Rabbeni,D.Harame,J.Dunn.Highly Resistive Substrate CMOS on SOI for Wireless Front-End Switch Application[C].CS MANTECH Conference, 2011,Palm Springs,California,USA.

[3] M.Jaffe,M.A.Khalil,A.Botula,J.E. Monaghan,J.Gambino,J.Gross,Z.X.He, A.Joseph,R.Phelps,S.Shank,J. Slinkman,R.Wolf.Improvements in SOI technology for RF switches[C].2015 IEEE 15th Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems, 2015:30-32.

-

集成电路

+关注

关注

5387文章

11540浏览量

361704 -

射频开关

+关注

关注

7文章

78浏览量

20595

原文标题:金属连线间形成空气隙的改进工艺研究

文章出处:【微信号:appic-cn,微信公众号:集成电路应用杂志】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Sic mesfet工艺威廉希尔官方网站 研究与器件研究

一种电磁型射频微机电系统开关的软磁悬臂梁制备工艺研究

MEMS开关缺陷的改进概述

射频开关在高低温电测试实验的改进

开关电源pcb线间距规则

空气的开关原理 空气开关的安装方式

半大马士革工艺:利用空气隙减少寄生电容

基于射频开关器件的金属连线间形成空气隙的改进工艺研究

基于射频开关器件的金属连线间形成空气隙的改进工艺研究

评论