CMOS与非门电路多余输入端的处理

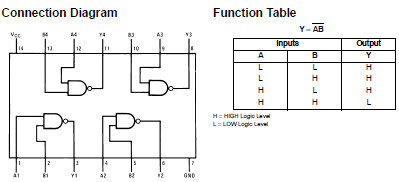

与非门电路的逻辑功能是输入信号只要有低电平.输出信号就是高电平.

只有当输入信号全部为高电平时.输出信号才是低电平。所以某输入端输入电平为高电平时.对电路的逻辑功能并无影响.即其它使用的输入端与输出

端之间仍具有与或者与非逻辑功能。这样对于CMOS与门、与非门电路的多余输入端就应采用高电平,即可通过限流电阻接电源。

TTL与非门电路多余输入端的处理

对于TTL 与非门,只要电路输入端有低电平输入,输出就为高电平.只有输入端全部为高电平时.输出才为低电平。根据其逻辑功能.当某输入端外接高电平时耐其逻辑功能无影响.根据这一特点应采用以下四种方法

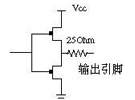

1、将多余输入端接高电平.即通过限流电阻与电源相连接。

2、根据TTL门电路的输入特性可知,当外接电阻为大电阻时.其输入电压为高电平。这样可以把多余的输入端悬空.此时.输入端相当于外接高电平。

3、通过大电阻到地,这也相当于输入端外接高电平。

4、当TTL门电路的工作速度不高.信号源驱动能力较强.多余输入端也可与使用的输入端并联使用。

TTL与非门多余的输入端比较

CMOS集成电路是一种新型的MOS集成电路,具有很多独特的优点,如静态功耗极低,允许电源电压波动范围大,抗干扰能力强,工作速度高,扇出系数大,输出逻辑振幅大。正因为如此,CMOS集成电路在各种科技领域中得到非常迅速而广泛地应用。类似于TTL门电路,CMOS集成门电路同样会存在多余输入端,对于多余输入端的处理方式不同,仍然会对电路性能带来不同的影响,而且有的影响是比较大的。

1.与门和与非门

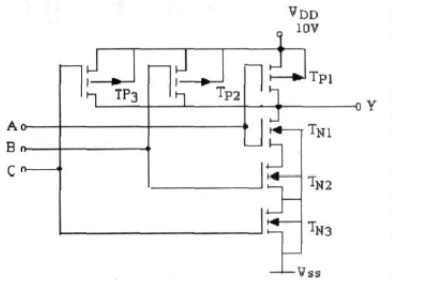

对于CMOS与非门的多余输入端,主要的处理方法仍然是将之与有用输入端并联或者将之设为高电平。CMOS输入端并联使用时,会影响CMOS电路的输出电阻。以与非门为例(图2),假设单个MOS管的输出电阻为RON,输入端并联后,在高电平输出时,输出电阻最小可达RON/3,输出电阻变小。输入端并联还会对CMOS门电路转折电压(即阀值电压)产生影响,使得转折电压变大,降低了高电平噪声容限。因此输入端并联后,一方面由于输出电阻变小而增强了与非门带拉电流负载的能力,另一方面使得电压传输特性右移。并联的输入端越多,高电平输出时输出电阻越小,电压传输特性右移越大,高电平噪声容限也就越小。输入端并联,还会降低开关速度,增大前级门的功耗。并联的输入端越多,这些影响越严重。由于MOS管的栅极与其它电极之间有绝缘层相隔,因此CMOS门电路的输入电阻很高,静态时几乎没有电流,所以即使通过高达几百kΩ的电阻接地也不能获得高电平。综上所述,对于CMOS与非门和与门电路的多余输入端的处理,通过限流电阻接VDD较好。

CMOS三输入端与非门

2.或门和或非门

对于或非门的多余输入端,我们可以将之与有用输入端并联或者通过限流电阻接地。与非门多余输入端并联使用时遇到的问题在或非门中同样存在。因为或非门电路中与VDD连接的三个TP管串联,与地连接的三个TN管并联,所以多余输入端并联后对或非门的影响刚好和与非门的相反,或非门输入端并联使用,使传输特性左移,转折电压减小,低电平噪声容限减小,带灌电流负载的能力有所增强[5]。

由上面分析可知,不管是TTL还是CMOS门电路的多余输入端,我们一般都不宜采取输入端并联的方法来处理多余输入端。不过在要求不高的情况下,这种处理方法却又是最方便的。所以大家可以根据实际情况,采取最有效的处理方法。

-

TTL

+关注

关注

7文章

503浏览量

70232 -

输入端

+关注

关注

0文章

34浏览量

11636

发布评论请先 登录

相关推荐

TTL与非门多余的输入端处理方法及其比较

TTL与非门多余的输入端处理方法及其比较

评论