4位二进制加法器原理

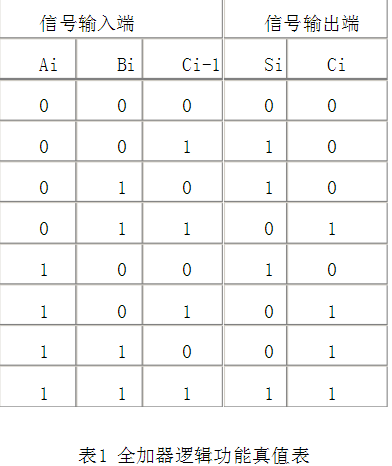

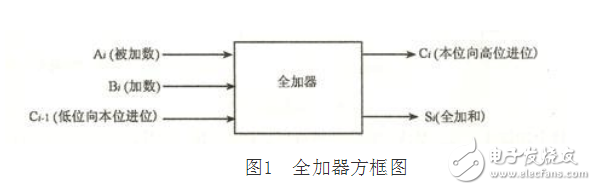

除本位两个数相加外,还要加上从低位来的进位数,称为全加器。图1为全加器的方框图。图2全加器原理图。被加数Ai、加数Bi从低位向本位进位Ci-1作为电路的输入,全加和Si与向高位的进位Ci作为电路的输出。能实现全加运算功能的电路称为全加电路。全加器的逻辑功能真值表如表1中所列。

4位二进制加法器设计

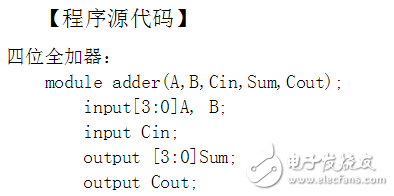

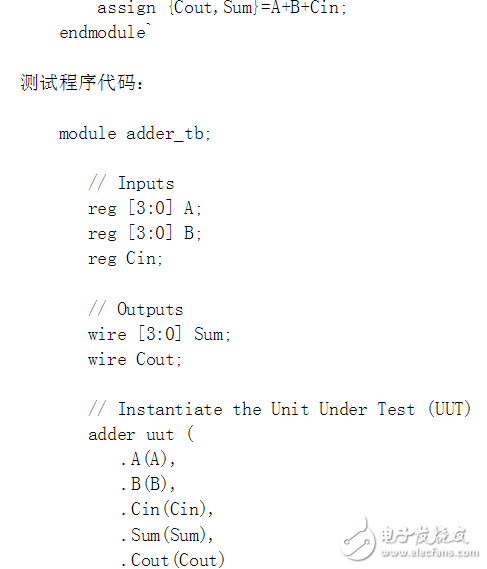

四位全加器

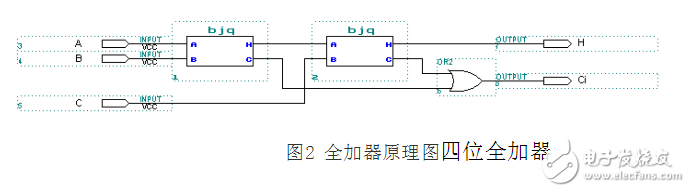

如图所示,四位全加器是由半加器和一位全加器组建而成:

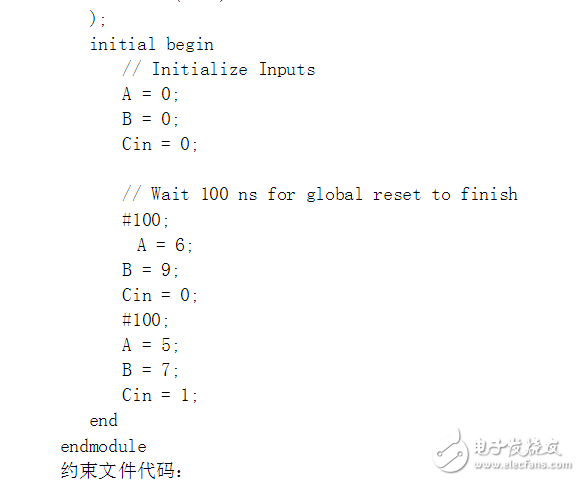

下图为四位全加器仿真图:

由仿真图可知电路正确。

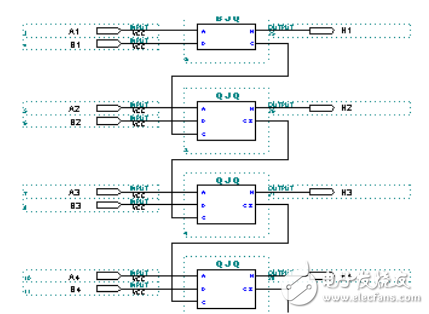

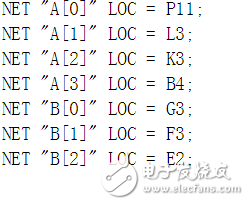

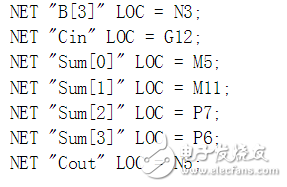

下图为内部电路模块图:

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

加法器

+关注

关注

6文章

183浏览量

30120 -

二进制加法器

+关注

关注

0文章

3浏览量

3271

发布评论请先 登录

相关推荐

加法器工作原理_加法器逻辑电路图

。在电子学中,加法器是一种数位电路,其可进行数字的加法计算。三码,主要的加法器是以二进制作运算。由于负数可用二的补数来表示,所以加减器也就不

发表于 02-18 14:40

•3.3w次阅读

串行加法器和并行加法器的区别?

串行加法器和并行加法器是两种基本的数字电路设计,用于执行二进制数的加法运算。它们在设计哲学、性能特点以及应用场景上有着明显的区别。

4位二进制加法器原理 4位二进制加法器设计

4位二进制加法器原理 4位二进制加法器设计

评论