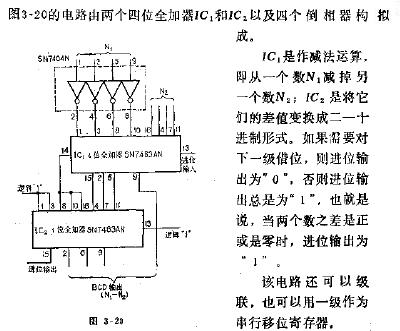

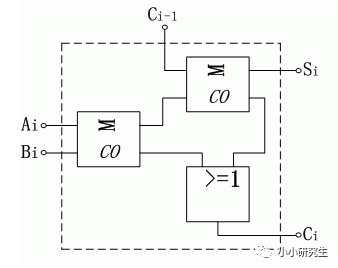

两个半加器组成全加器的做法

用门电路实现两个二进数相加并求出和的组合线路,称为一个全加器。

全加器是能够计算低位进位的二进制加法电路

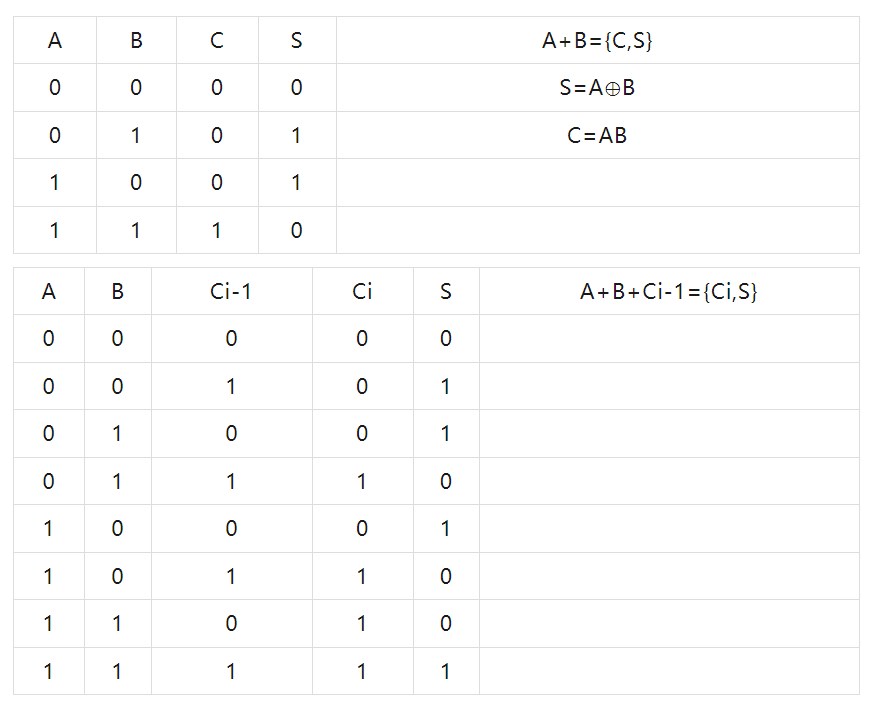

一位全加器(FA)的逻辑表达式为:

S=A⊕B⊕Cin

Co=AB+BCin+ACin

其中A,B为要相加的数,Cin为进位输入;S为和,Co是进位输出;

如果要实现多位加法可以进行级联,就是串起来使用;比如32位+32位,就需要32个全加器;这种级联就是串行结构速度慢,如果要并行快速相加可以用超前进位加法。

全加器和半加器的应用

应用原理

计算机最基本的任务之一是进行算数,在机器中四则运算——加、减、乘、除——都是分解成加法运算进行的,因此加法器便成为计算机中最基本的运算单元。

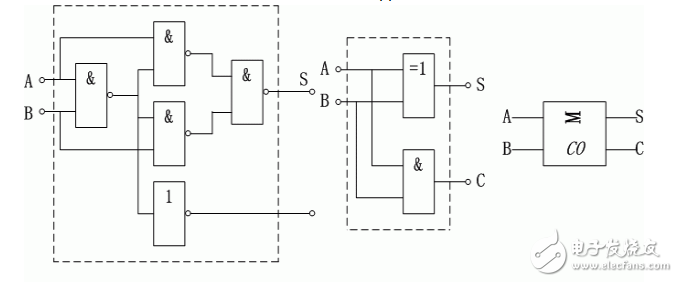

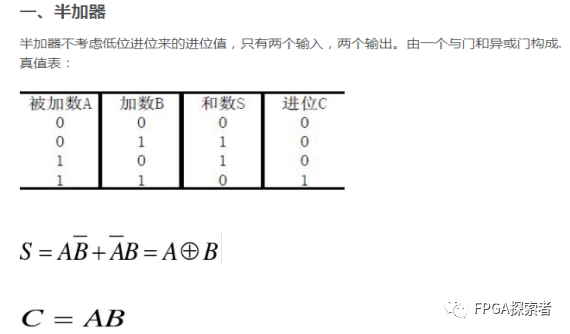

半加器原理

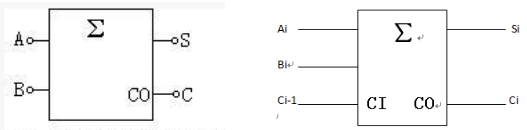

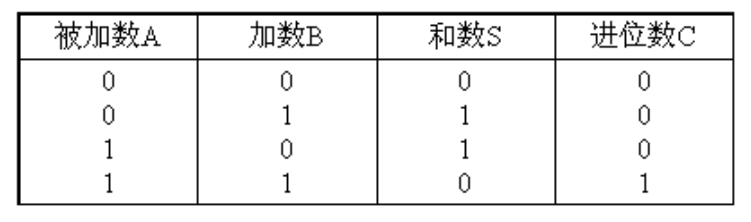

两个二进制数相加,叫做半加,实现半加操作的电路,称为半加器。表2.6.1是半加器的真值表,图a为半加器的符号,A表示被加数,B表示加数,S表示半加和,C表示向高位的进位。

从二进制数加法的角度看,真值表中只考虑了两个加数本身,没有考虑低位来得进位,这就是半加器的由来。由真值表可得半加器逻辑表达式

(a)半加器符号 (b)全加器符号

全加器原理

全加器能进行加数、被加数和低位来的进位信号相加,并根据求和的结果给出该位的进位信号。图b为全加器的符号,如果用Ai,Bi表示A,B两个数的第i位,Ci-1表示为相邻低来的进位数,Si表示为本位和数(成为全加和),Ci表示为相邻高位的进位数。可以很容易的求出S、C的简化函数表达式。表2.6.2是全加器的真值表

用一位全加器可以构成多位加法电路。由于每一位加法的结果必须等到低一位的进位产生后才能产生(这种结构称为串行进位加法器),因而运算速度很慢。为了提高运算速度,制成了超前进位那加法器。这种电路各进位信号的产生只需经历一级与非门和一级或非门的延迟时间,比串行进位的全加器大大缩短了时间。

1.实现半加/半减器

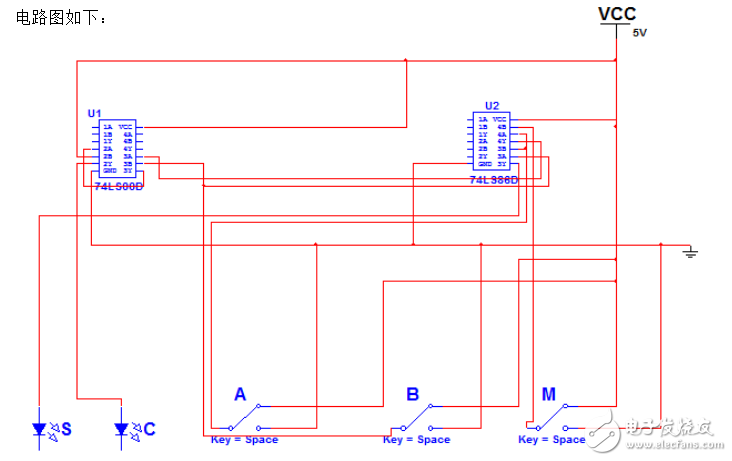

用异或门74LS86和与非门74LS00组成半加%2F半减器,当控制信号M%3D0时实现半加器功能,当控制信号M%3D1时实现半减器功能。

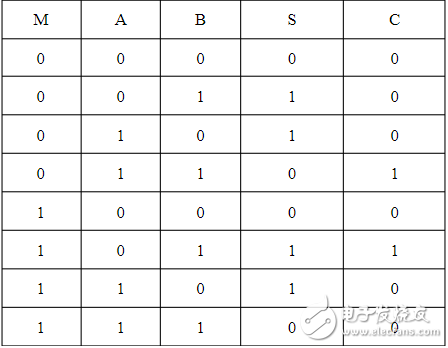

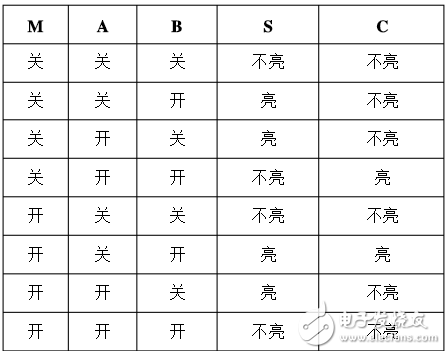

半加/半减器真值表

结果:

注意:开关开表示输入1,关表示输入0。灯亮表示输出1,不亮表示0。

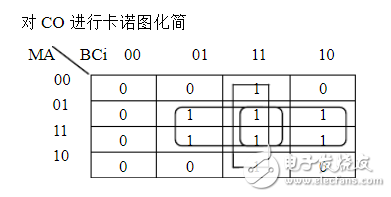

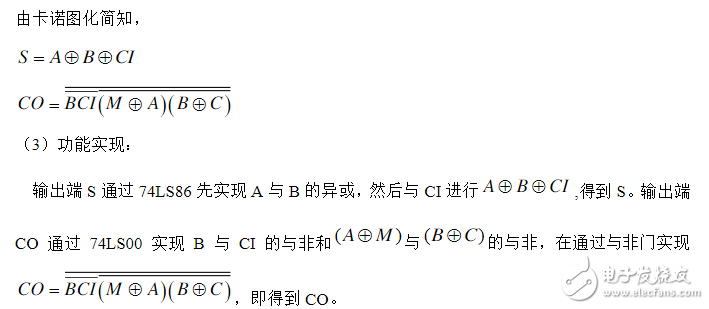

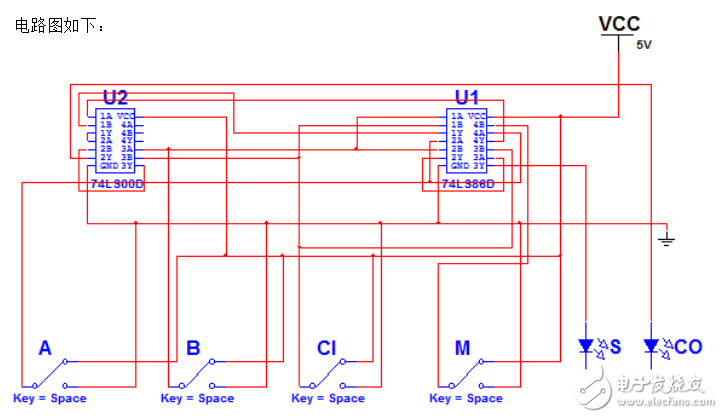

2.实现全加/全减器

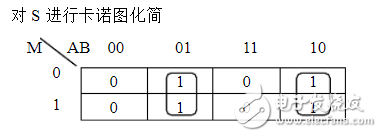

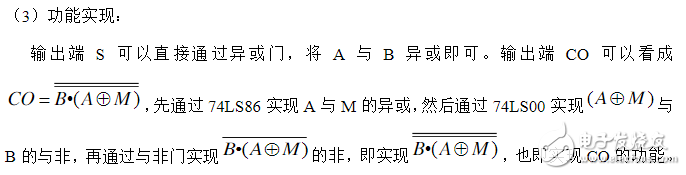

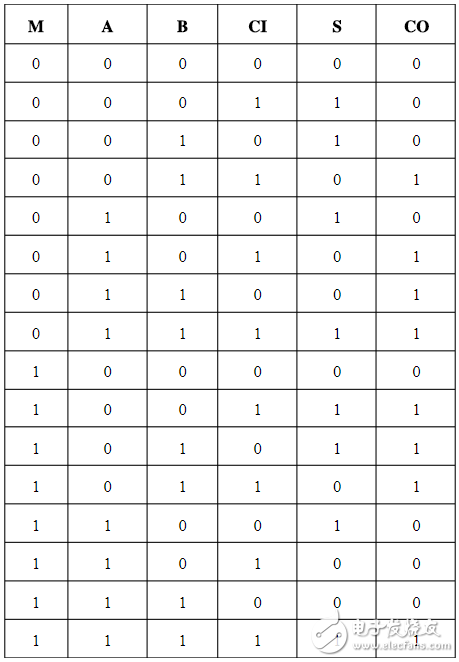

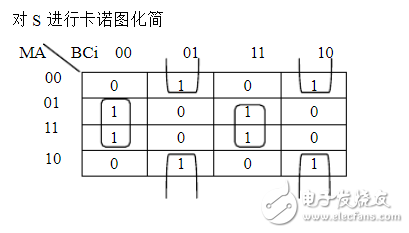

用74LS86和若干与非门组成全加%2F全减器,当控制信号M%3D0时实现全加器功能,当控制信号M%3D1时实现全减器功能。要求设计的逻辑电路门数量最少。

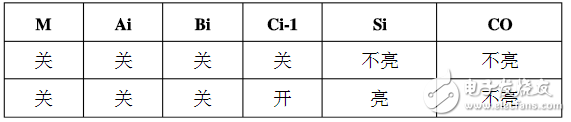

全加/全减器真值表

结果:

结论:通过开关控制输入,观察输出信号灯的亮与灭符合真值表。

-

全加器

+关注

关注

10文章

62浏览量

28497 -

半加器

+关注

关注

1文章

29浏览量

8791

发布评论请先 登录

相关推荐

两个半加器组成全加器的做法 浅谈全加器和半加器的应用

两个半加器组成全加器的做法 浅谈全加器和半加器的应用

评论