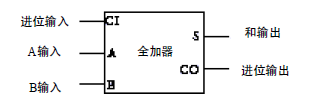

实际上,一个完整的加法器的输入端有3个:A、B和低位的进位结果CI。

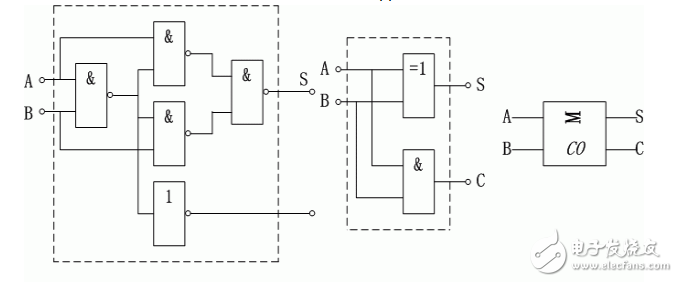

全加器(Full Adder)

这个全加器相当于是计算3个位(A、B、CI)的和。因此,其最终的“和输出”为三个数的异或。进位输出的规律为:3个数中如果有2个或者以上的数为1时,“进位”位就为1.

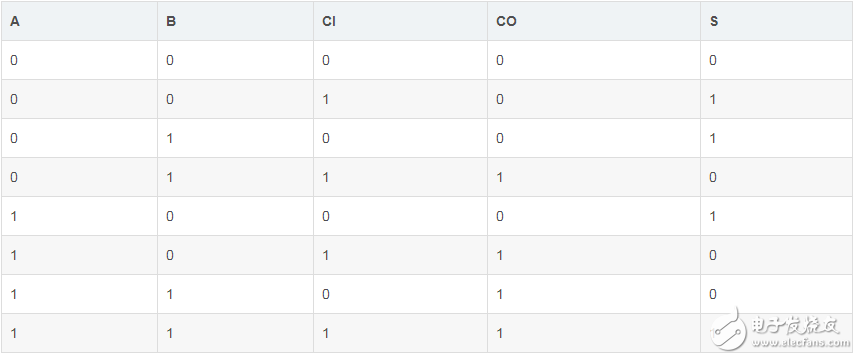

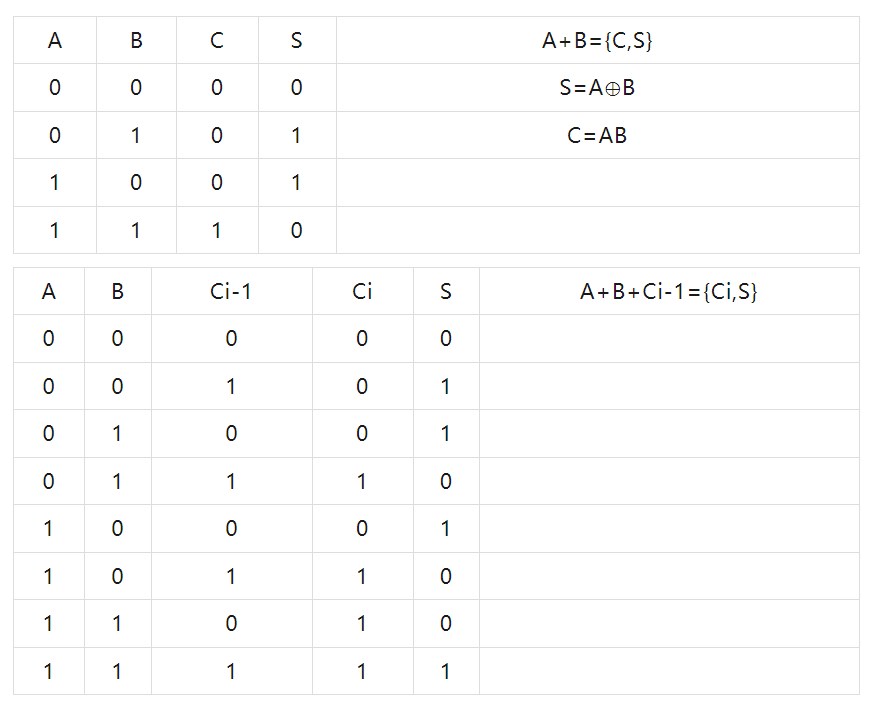

全加器真值表

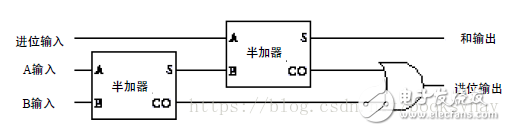

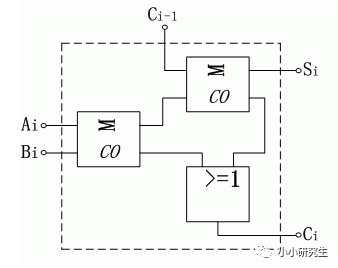

为了实现这个功能,可以使用两个半加器:

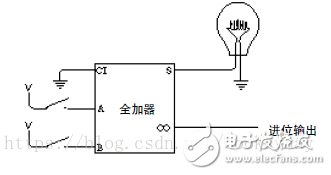

这个一位的全加器应用于个位时,需要将进位输出接到地,即置为0:

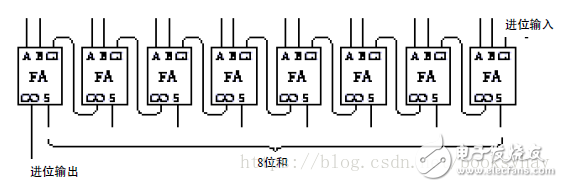

将多个“一位全加器”级联起来,可以变成“多位全加器”,上一个全加器的“进位输出”连到下一个全加器的“进位输入”。比如8位全加器如下:

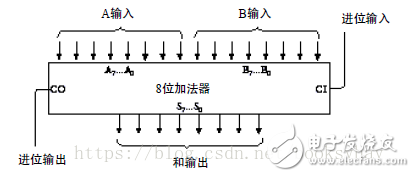

可以简化为:

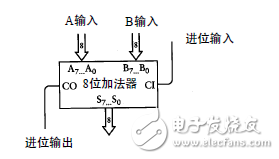

或者:

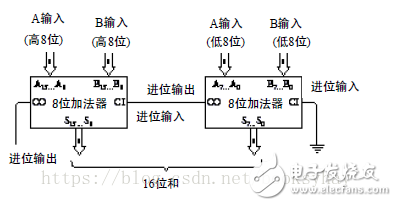

同样的,可以将两个8位全加器级联起来,变成一个16位的全加器:

最后:你可能会问:“计算机真的是以这种方式把数字加起来的吗?”

基本上是这样的,但不完全是。

首先,加法器应该做得更快。如果你明白这个电路是如何工作的,你会看到最低位相加产生的进位作为下一列数相加的一个输入,而第3列的加法又等着第2列加法的进位,依此类推。加法器总体的速度等于加数的位数乘以单个全加器的速度。这种进位方式称为行波进位。

更快的加法器使用称为先行进位的加法电路,从而加快了加法进程。

第二(但是十分重要),计算机再也不用继电器了!尽管它们曾经用过。建于2 0世纪3 0年代初的第一批数字计算机使用继电器,后来又用了真空管。现代计算机用晶体管。当用在计算机中时,晶体管和继电器的功能差不多,但是晶体管速度更快,体积更小,更安静,更省电,而且还便宜不少。构造一个8位加法器仍然需要1 4 4个晶体管(如果采用先行进位,则需要更多),但整体电路的体积却小多了。

-

全加器

+关注

关注

10文章

62浏览量

28498 -

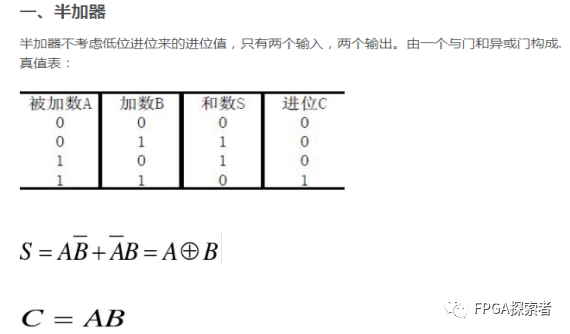

半加器

+关注

关注

1文章

29浏览量

8791

发布评论请先 登录

相关推荐

如何用半加器实现全加器?

如何用半加器实现全加器?

评论