在设计高性能数据采集系统时,勤奋的工程师仔细选择高精度模数转换器(ADC)以及interwetten与威廉的赔率体系 前端调节电路所需的其他元件。在几个星期的设计工作之后,执行模拟并优化电路原理图,为了赶工期,设计人员迅速地将电路板布局布线组合在一起。一个星期之后,对第一个原型电路板进行测试。出乎预料的是,电路板性能与预期的不一样。

这种情景在你身上发生过吗?

最优PCB布局布线对于使ADC达到预期的性能至关重要。当设计包含混合信号器件的电路时,应该始终从良好的接地安排入手,并且使用最佳元件放置位置和信号走线将设计分为模拟、数字和电源部分。

参考路径是ADC布局布线中最关键的,这是因为所有转换都是基准电压的函数。在传统逐次逼近寄存器 (SAR) ADC架构中,参考路径也是最敏感的,因为基准引脚上有到基准源的动态负载。

由于基准电压在每次转换期间被数次采样,高电流瞬变出现在这个终端上,其中ADC内部电容器阵列在这个位置位时被开启和充电。基准电压在每个转换时钟周期内必须保持稳定,并且稳定至所需的N位分辨率,否则的话会出现线性误差和丢码错误。

图1显示典型12位SAR ADC基准终端上的转换阶段期间的电流瞬变。

图1. 12位SAR ADC基准引脚上的电流瞬变

由于这些动态电流,需要使用高质量旁路电容器(CREF)对基准引脚进行去耦合操作。此旁路电容器用作一个电荷存储器,在这些高频瞬变电流期间提供瞬时充电。应该将基准旁路电容器放置在尽量靠近基准引脚的位置上,并使用较短的低电感连接将它们连接在一起。

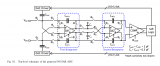

图2为有两个独立内部电压基准的14位双ADCADS7851的电路板布局布线示例。

图2.具有两个独立内部电压基准的双ADC布局布线示例

在这个四层PCB电路板示例中,设计人员使用了位于元件正下方的坚固接地平面,并将电路板划分为模拟和数字部分,以使敏感输入和基准信号远离噪声源。他用10μF,X7R级,0805尺寸的陶瓷电容器 (CREF-x) 来旁路REFOUT-A和REFOUT-B基准输出,以实现最优性能,并且将他们连接至使用小型0.1 Ω串联电阻的元件上,以保持总体阻抗高频时较低且恒定。他还使用宽迹线来减少电感。

我强烈建议把CREF与ADC放在同一层上。还应该避免在基准引脚和旁路电容器之间放置导孔。ADS7851的每一个基准接地引脚都有单独的接地连接,而每个旁路电容器都有到接地路径的低电感连接。

如果你正在使用需要外部基准源的ADC,你应该尽量降低参考信号路径中的电感——从基准缓冲器输出到旁路电容器,到ADC基准输入。

图3为使用外部基准和缓冲器的18位SAR ADCADS8881的布局布线示例。通过将电容器放置在引脚的0.1英寸范围以内,并且将其与宽度为20密耳的迹线和多个15密耳的接地导孔相连,设计人员将基准电容器和REF引脚之间的电感保持在小于2nH的水平上。我推荐使用额定电压至少为10V的单个,10uF,X7R级,0805尺寸的陶瓷电容器。

基准缓冲器电路到REF引脚的迹线长度保持为尽可能的短,以确保快速稳定响应。

REF引脚的正确去耦合对于实现最优性能十分关键。此外,在参考路径中保持低电感连接使得基准驱动电路在转换期间保持稳定,使你向获得所需的效果又迈进了一步。

图3.具有外部基准和缓冲器的ADC布局布线示例

-

pcb

+关注

关注

4319文章

23083浏览量

397558 -

SAR

+关注

关注

3文章

416浏览量

45952 -

adc

+关注

关注

98文章

6496浏览量

544483

发布评论请先 登录

相关推荐

求助,关于模拟电路的PCB布线及布局问题求解

高速ADC PCB布局布线技巧分享

关于SAR、ADC、PCB布局布线参考指南

关于SAR、ADC、PCB布局布线参考指南

评论