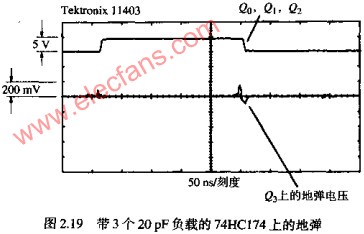

所谓“地弹”,是指芯片内部“地”电平相对于电路板“地”电平的变化现象。以电路板“地”为参考,就像是芯片内部的“地”电平不断的跳动,因此形象的称之为地弹(ground bounce)。当器件输出端有一个状态跳变到另一个状态时,地弹现象会导致器件逻辑输入端产生毛刺。

那么“地弹”是如何产生的呢?

首先我们要明白,对于任何封装的芯片,其引脚会存在电感电容等寄生参数。而地弹正是由于引脚上的电感引起的。

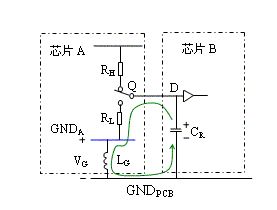

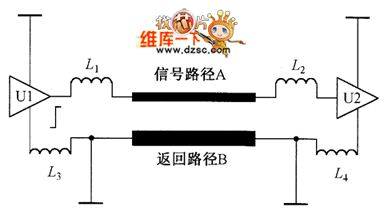

我们可以用下图来直观的解释一下。图中开关Q的不同位置代表了输出的“0”“1”两种状态。假定由于电路状态装换,开关Q接通RL低电平,负载电容对地放电,随着负载电容电压下降,它积累的电荷流向地,在接地回路上形成一个大的电流浪涌。随着放电电流建立然后衰减,这一电流变化作用于接地引脚的电感LG,这样在芯片外的电路板“地”与芯片内的地之间,会形成一定的电压差,如图中VG。这种由于输出转换引起的芯片内部参考地电位漂移就是地弹。

芯片A的输出变化,产生地弹。这对芯片A的输入逻辑是有影响的。接收逻辑把输入电压和芯片内部的地电压差分比较确定输入,因此从接收逻辑来看就象输入信号本身叠加了一个与地弹噪声相同的噪声。

现在,集成电路的规模越来越大,开关速度不断提高,地弹噪声如果控制不好就会影响电路的功能,因此有必要深入理解地弹的概念并研究它的规律。

-

芯片

+关注

关注

455文章

50812浏览量

423591 -

电路板

+关注

关注

140文章

4960浏览量

97833 -

电压

+关注

关注

45文章

5605浏览量

115767

原文标题:SI仿真分析——什么是地弹

文章出处:【微信号:PCBTech,微信公众号:EDA设计智汇馆】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

【连载笔记】信号完整性-有效电感、总电感或净地弹及地弹

认识地弹

高速电路PCB的地弹

基于DSP的弹载嵌入式系统该怎么设计?

电源扰动及地弹噪声的产生机理

同地弹现象的分析和讲解

减少DC-DC Converter中的地弹

如如何减弱“PCB地弹效应”

“地弹”是如何产生的呢?

“地弹”是如何产生的呢?

评论