首先举一个例子:

早期的DDR(注:DDR2开始支持ODT功能),当向内存写入数据时,如果只有一条内存,那么这条内存就自己进行信号的终结,终结电阻等效为150Ω。如果为两条内存,那么他们会交错的进行信号的 终结。第一个模组工作时,第二个模组进行终结操作,等第二个模组工作时,第一个模组进行终结操作,但等效电阻为75Ω。当有三条内存的时候,三条会交替进 行信号终结,但等效电阻为50Ω。对于省略终端电阻的DIMM(因为支持ODT,所以可以省略),也是同样的道理。假设使用同步模式ODT,且终结电阻被设置为150Ω,当向内存写入数据时,如果只有一个内存颗粒,那么这条内存就自己进行信号的终结,终结电阻等效为150Ω。

如果为两个内存颗粒,那么他们会交错的进行信号的 终结。第一个内存颗粒工作时,第二个内存颗粒进行终结操作,等第二个内存颗粒工作时,第一个内存颗粒进行终结操作,但等效电阻为75Ω。当有三个内存颗粒的时候,三个会交替进行信号终结,但等效电阻为50Ω。

这样一来,信号完整性就会受到不同程度的影响,为了能够保持等效电阻一致,我们希望ODT的RTT(终结电阻)是可以动态修改的,而不需要每次都要通过MRS Command进行修改。这就是接下来要介绍的动态ODT模式。

当MR2寄存器中的A9和A10位被置位为1,动态ODT模式将会被启用。具体的功能描述如下:

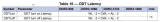

• Two RTT values are available: RTT_Nom and RTT_WR.– The value for RTT_Nom is preselected via bits A[9,6,2] in MR1.– The value for RTT_WR is preselected via bits A[10,9] in MR2.• During operation without write commands, the termination is controlled as follows:– Nominal termination strength RTT_Nom is selected.– Termination on/off timing is controlled via ODT pin and latencies ODTLon and ODTLoff.• When a write command (WR, WRA, WRS4, WRS8, WRAS4, WRAS8) is registered, and if DynamicODT is enabled, the termination is controlled as follows:– A latency ODTLcnw after the write command, termination strength RTT_WR is selected.– A latency ODTLcwn8 (for BL8, fixed by MRS or selected OTF) or ODTLcwn4 (for BC4, fixed by MRS

or selected OTF) after the write command, termination strength RTT_Nom is selected.– Termination on/off timing is controlled via ODT pin and ODTLon, ODTLoff.

需要注意的是,动态ODT并不支持DLL-off模式,用户必须通过设置MR2{A10, A9}={0,0},来禁用动态ODT功能。

由于时序图比较长,为了防止图像压缩后变得不清晰,所以改成了pdf文件的形式。

DynamicODT.pdf

异步ODT功能因为使用的频率较低,此处不再详细介绍。

-

电阻

+关注

关注

86文章

5509浏览量

171959 -

DDR

+关注

关注

11文章

712浏览量

65318 -

信号完整性

+关注

关注

68文章

1405浏览量

95459

原文标题:【博文连载】DDR3中的ODT动态模式详解

文章出处:【微信号:ChinaAET,微信公众号:电子威廉希尔官方网站 应用ChinaAET】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

DDRx的关键威廉希尔官方网站 介绍(中)

Q [17:0]和CQ输出需要FPGA/ASIC端的ODT吗?

DDR3 ZQ校准简单介绍

浅析DDR3 ODT

动态ODT功能

关于ODT与驱动强度的相关知识介绍

ODT在手,DDR5布线可以任性走?

什么是动态同步传输模式

聊一聊ODT的几种操作模式

什么是ODT,它是怎么工作的?

动态Sql介绍

动态无功补偿装置的三种运行模式

介绍动态ODT模式

介绍动态ODT模式

评论