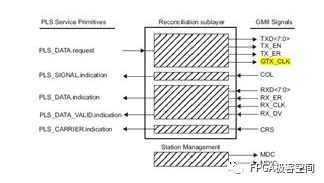

GMII接口提供了8位数据通道,125MHz的时钟速率,从而1000Mbps的数据传输速率。下图定义了RS层的输入输出信号以及STA的信号:

Reconciliation Sublayer (RS) and STA connectionsto GMII

下面将详细介绍GMII接口的信号定义,时序特性等。由于GMII接口有MAC和PHY模式,因此,将会根据这两种不同的模式进行分析。

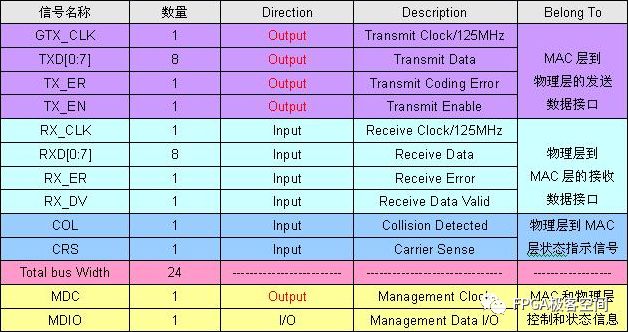

GMII接口信号定义

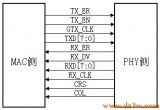

GMII接口可分为MAC模式和PHY模式,一般说来MAC和PHY对接,但是MAC和MAC也是可以对接的。

在GMII接口中,它是用8根数据线来传送数据的,这样在传送1000M数据时,时钟就会125MHz。

GMII接口主要包括四个部分。一是从MAC层到物理层的发送数据接口,二是从物理层到MAC层的接收数据接口,三是从物理层到MAC层的状态指示信号,四是MAC层和物理层之间传送控制和状态信息的MDIO接口。

GMII接口的MAC模式定义:

注意在表中,信号GTX_CLK对于MAC来说,此时是Output信号,这一点和MII接口中的TX_CLK的Input特性不一致。

GMII接口PHY模式定义:

注意在表中,信号GTX_CLK对于PHY来说,此时是Input信号,这一点和MII接口中的TX_CLK的Output特性不一致。

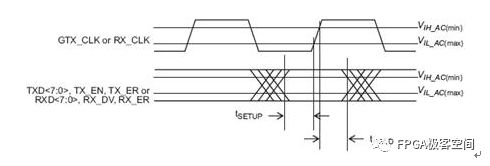

GMII接口时序特性

在GMII接口中,TX通道参考时钟是GTX_CLK,RX通道参考时钟是RX_CLK,802.3-2005定义了它们之间的关系。

GMII signal timing at receiver input

由上图可知,Spec只定义了TX通道和RX通道中接收端Setup时间和Hold时间。很明显,即该Spec只对TX通道上PHY这一侧的接收特性作了定义,而对TX通道MAC那一侧的发送特性并没有定义。ICVendor可在TX通道那一侧的MAC的发送特性作适当调整,只要最终的时序满足TX通道上PHY这一侧的接收特性就可以。

同样的道理,该Spec只对RX通道上MAC这一侧的接收特性作了定义,而对RX通道PHY那一侧的发送特性并没有定义。IC Vendor可在RX通道那一侧的PHY的发送特性作适当调整,只要最终的时序满足RX通道上MAC这一侧的接收特性就可以。

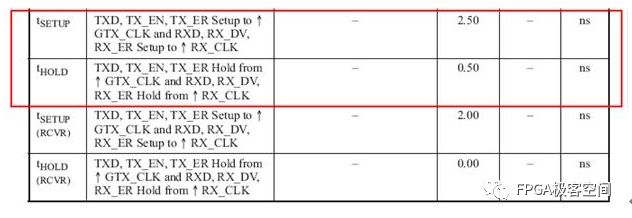

Setup和Hold Time的值

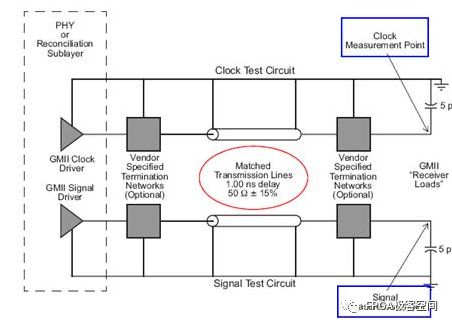

从图中可以看出,这里有两组setup和hold时间。其中第一组Spec则是根据下图给定的测试电路定义的,即该Spec未考虑PCB上传输线的不匹配等影响。而第二组Spec则是定义了receiver at its inputpins的时间要求,它考虑了PCB上传输线的长度不匹配等影响。一般IC Vendor需要按照第二组Spec来设计它们的IC。

GMII接口Setup和Hold Time测试电路

GMII信号功能特性:

<1>: GTX_CLK (transmit clock),GTX_CLK (Transmit Clock)是一个连续的时钟信号(即系统启动,该信号就一直存在),它是TX_EN, TXD, and TX_ER(信号方向为从RS到PHY)的参考时钟,PHY端在信号的上升沿采样,GTX_CLK由MAC驱动。GTX_CLK的时钟频率是数据传输速率的12.5,即125MHz。

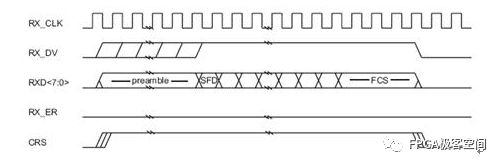

<2>:对于同样的RX_CLK,它与TX_CLK具有相同的要求,所不同的是它是RX_DV, RXD, and RX_ER(信号方向是从PHY到RS)的参考时钟,MAC端在时钟的上升沿采样。RX_CLK是由PHY驱动,PHY可能从接收到的数据中提取时钟RX_CLK,也有可能从一个名义上的参考时钟(e.g., the TX_CLK reference)来驱动RX_CLK

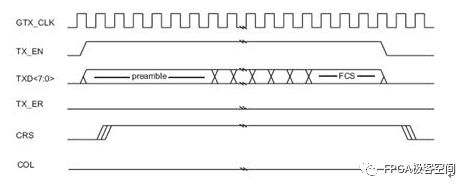

<3>:GMII接口的发送时序,接收时序如下图,至于其它信号的功能特性以及在数据传输过程中,不同信号的逻辑变化所代表的意义,这里不再描述,大体上和“MII信号功能特性”一节中描述类似,读者可以参阅802.3-3005的Spec。

GMII信号发送时序

GMII信号接收时序

-

接口

+关注

关注

33文章

8582浏览量

151067 -

Mac

+关注

关注

0文章

1105浏览量

51463 -

物理层

+关注

关注

1文章

148浏览量

34363

原文标题:GMII 接口分析

文章出处:【微信号:ALIFPGA,微信公众号:FPGA极客空间】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

GMII和RGMII主要的接口

RGMII的特点?RGMII与GMII转换电路设计

以太网接口知识

一文读懂以太网MII/RMII/GMII三种接口

千兆以太网MII接口类型_接口信号及时序介绍

RGMII接口信号和帧格式_RGMII接口应用框图

RGMII应用框图/接口信号/帧格式

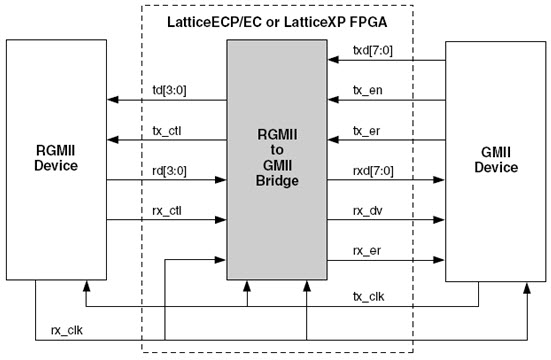

基于RGMII to GMII Bridge以太网接口的参考设计

详细介绍GMII接口的信号定义

详细介绍GMII接口的信号定义

评论