经过这几年的市场磨砺,Zynq-7000 FPGA SoC器件平台在开发者中的认知度和接受度越来越高,这种“ARM处理器+可编程逻辑”的创新架构,可以帮助开发者在设计中找到高性能与灵活性的完美平衡,对此大家也心知肚明。

但是在实际的应用中,想要玩转Zynq这种“异构”平台,并非信手拈来这样简单。其中很大的一个原因就是以往的开发工具都是彼此分立且松散连接的,设计和实现效率不高,因此需要一种全新的设计方法和开发工具来支持Zynq的应用开发。

Xilinx推出的Vivado设计套件恰好能够满足这一需求。Vivado是一种以IP和系统为中心、支持7系列以及更新系列器件的(包括7系列FPGA、Zynq-7000 AP SoC、UltraScale / UltraScale Plus FPGA、Zynq US+ MPSoC等)全新集成开发环境,可解决用户在系统级集成和实现过程中常见的生产力瓶颈问题。Vivado目前最新的HLx版本可为设计团队提供实现基于C的设计、重用优化、IP子系统复用、集成自动化以及设计收敛加速所需的工具和方法,结合UltraFast高层次生产力设计方法,可帮助设计人员以高层次抽象形式开展工作,加速高层次设计、验证和实现。

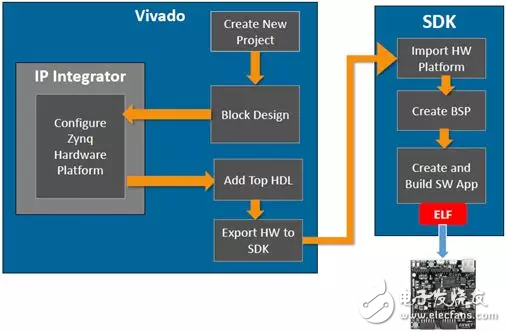

图1,Zynq全可编程平台设计开发流程

在近日举办的安富利MiniZed Speedway培训活动中,一个重要的议程就是:如何帮助开发者使用Vivado设计套件创建一个符合用户设计需求的Zynq-7000硬件平台。

与传统的处理器不同,Zynq平台的处理器系统(PS)包含一系列常用的外设资源(如I2C、UART、CAN、GPIO、SPI、USB 2.0、Ethernet MAC、SDIO等)以及多端口DRAM Controller(可支持DDR2、DDR3/3L或LPDDR2颗粒组成一个16-bit或32-bit的存储器系统)。而且,PS通过专用的端口可以直接和可编程逻辑(PL)进行通信和数据共享,使用PL可以创建用户自定义IP,扩展PS的外设和处理能力。虽然说PS可以在没有任何PL编程的情况下使用,但是为了充分利用PL中的软IP资源,或者完成PS特定的外设与PL器件引脚间的连接布线,对PL的编程还是必要的。这也是Zynq平台硬件设计不同于和优于传统处理器的重要特征。

在为期一天的MiniZed Speedway培训中,安富利讲师详细讲解了Zynq-7000 SoC的系统架构,硬件开发的设计流程,核心的知识点包括:

Zynq-7000 SoC的架构

Xilinx嵌入式设计工具和设计流程

如何使用Vivado IPI配置PS、外设以及PS和PL之间的接口

如何使用Vivado IP Package创建一个用户自定义IP

如何使用ILA和硬件管理器(Hardware Manger)调试用户自定义IP

与此同时,安富利还为本次培训精心准备了实操性的实验环节,指导开发者完成硬件设计中的关键环节。例如:

创建一个基础的Zynq设计项目

使用Vivado IP Integrator (IPI)配置PS

在Zynq设计中添加基于PL的外设

使用PS DMA优化PS和PL之间的数据流程

使用Vivado IP Packager创建一个用户自定义IP

使用Vivado Hardware Manager调试基于PL的用户自定义IP

可以看到,培训中“手把手”地介绍了Zynq硬件平台配置过程中Vivado的一些核心子工具的特性和使用方法,如Vivado IP集成器(IPI)。IPI可提供图形化的基于Tcl、自动连线、自动检查和纠正错误(correct-by-construction)的开发流程,可提供具有器件和平台意识的互动环境,能支持关键IP接口的智能自动连接、一键式IP子系统生成、实时DRC等功能,此外还提供强大的调试功能。在IP之间建立连接时,设计人员工作在“接口(Interface)”而不是“信号(Signal)”的抽象层面上,能充分利用IP资源快速组装复杂系统,从而大幅提高了生产力。通过利用Vivado中IPI和HLS(高层次综合)工具的完美组合,客户的开发效率相对于传统的RTL方式可提高数倍之多。

总之,按照MiniZed Speedway培训展示的“套路”,熟悉了Vivado这样高效的设计工具,掌握了系统的设计方法,释放出Zynq全可编程平台的硬件潜能,并非难事!

-

FPGA

+关注

关注

1629文章

21729浏览量

602960 -

Zynq

+关注

关注

10文章

609浏览量

47174

发布评论请先 登录

相关推荐

怎么集齐7个云平台?本文教你!

一文教你如何玩转Zynq平台

一文教你如何玩转Zynq平台

评论