面向高性能计算、金融领域应用和低延时交易的FPGA解决方案

作为大规模FPGA开发平台行业的领导者Dini Group在近日推出了一款面向定制网络应用,例如TOE(TCP/IP Offload)和线速算法交易应用的解决方案——DNPCIE_400G_VU_LL,该平台基于强大的Xilinx UltraScale+架构FPGA,容量高达2000万ASIC门。

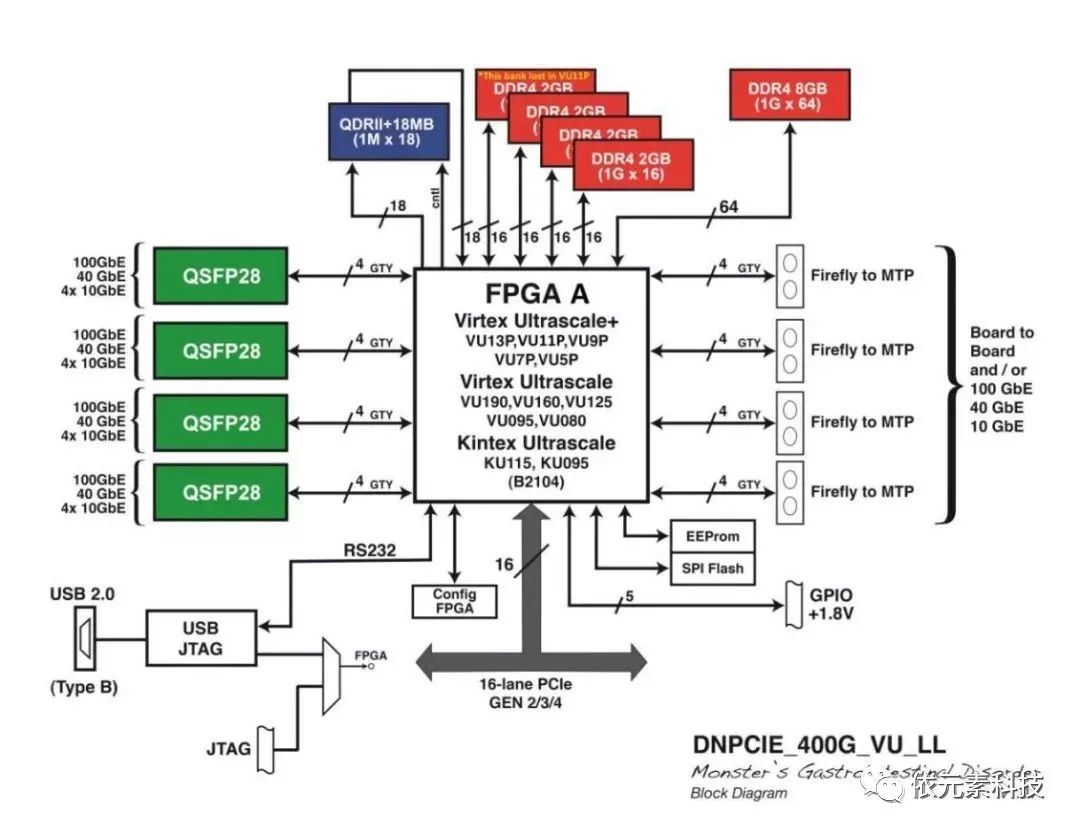

DNPCIE_400G_VU_LL系统框图

高速、低延时的存储器是算法加速应用的关键资源

DNPCIE_400G_VU_LL平台是全高半长的PCIe板,搭载一颗Xilinx UltraScale+系列FPGA,同时具有5个bank的DDR4内存和1个bank的QDRII+存储。

高速、低延时的存储器是算法加速应用的关键资源,Xilinx UltraScale+系列FPGA通过增加UltraRAM blocks资源来拓展内部存储容量。

DNPCIE_400G_VU_LL采用B2104封装,16-lane Gen4 PCIe接口使用了16个高速收发器,4个可拆分成4路的QSFP28,每个连接有4个高速速收发器,用于实现四个独立的40GbE/100GbE以太网接口,或者最多16个10GbE通道。

DNPCIE_400G_VU_LL实物照片

DNPCIE_400G_VU_LL平台支持用户自选Xilinx UltraScale+,Virtex UltraScale和Kintex UltraScale三种系列器件12款芯片

DNPCIE_400G_VU_LL可选择5种Xilinx UltraScale+ FPGAs,其中VU13P拥有2000万ASIC门和超过12000的27x18乘法器。此外还5款Virtex UltraScale和2款Kintex UltraScale器件可供选项。

DNPCIE_400G_VU_LL支持5个独立的PC2400 DDR4 banks,4个bank被配置为1G x 16(2GB),一个Bank被配置为1G x 64(8GB),总计16GB存储资源。对于数据查找最小延时的需求,DNPCIE_400G_VU_LL提供1Mx18的QDRII+存储器(可升级4Mx18)。

非常适合进行集群部署到Co-location的空间或交换

“我们制作的Xilinx最新UltraScale+平台尽可能的实现性能极限(高速)和多功能化”总裁Mike Dini说到“它非常适合进行集群部署到co-location的空间或交换。网络应用与高频/低延时算法交易可以享受线速通信和包处理。”

Dini Group是大规模FPGA板、系统、关键IP供应商的行业领导者。Dini Group FPGA板卡被广泛用于大规模ASIC和SOC原型、低延时交易和高性能计算等应用领域。

Dini Group的主营业务

无论您的设计在硬件上遇到什么工程问题,我们的FPGA平台都可以比市场上其他任何FPGA平台提供更快的速度,更好地解决工程问题。 无论是高性能计算,低延迟交易,多核大规模FPGA原型,SoC原型,电信分析,ASIC原型开发,代码验证,云计算,视频和音频压缩和滤波,算法加速-我们的平台都可以胜任所有这些问题。

-

FPGA

+关注

关注

1629文章

21729浏览量

603037 -

存储器

+关注

关注

38文章

7484浏览量

163770 -

Xilinx

+关注

关注

71文章

2167浏览量

121315

原文标题:基于Xilinx最新 UltraScale+ 架构面向高速低延时网络应用、算法加速、数据中心应用的400G解决方案

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA构建高性能DSP

Altera率先交付高性能28nm FPGA量产芯片

通过高性能FPGA搭建的客制硬体,更大幅缩短往返交易延迟

中科亿海微推出面向金融高频交易的超低延时交换机产品

如何通过DLP FPGA实现低延时高性能的深度学习处理器设计呢?

高性能计算、金融领域应用和低延时交易的FPGA解决方案

高性能计算、金融领域应用和低延时交易的FPGA解决方案

评论