地线干扰的共阻干扰

1、本文出发点

本文基于噪声产生的原理, 进一步论述简单而实用的应用:数模混合音频系统中最简单的规避地噪声手段—— “单点接地”。让读者明白“为什么要单点接地” 。希望读者着重认清单点接地的原理,从而化用、推广到其他地方,而不是简单地记住本文中所提到的例子。

2、本文适用的读者

“单点接地”是否有似曾相识的感觉?

假如你现在的情况是“听说过单点接地, 但是不知道具体应该如何单点接地;或者大致知道如何单点接地,但是不能清楚地理解单点接地的原理” 。那么很幸运,本文为你而写!

3、共阻干扰存在的几种形式

本文重点是:讲述了共阻干扰的几种常见形式,会产生几种经典后果:干扰会被放大后输出、干扰被衰减后输出、干扰被原原本本地输出等。

(地线)共阻干扰存在的根本原因是: (地)导线存在阻抗,且干扰与被干扰信号有共同的信号回路。

3.1、共阻干扰的几种形式

3.1.1、完全没有共阻噪声

理想状态,导线无阻抗、分布参数,不存在噪声。Av-niose = 0 :

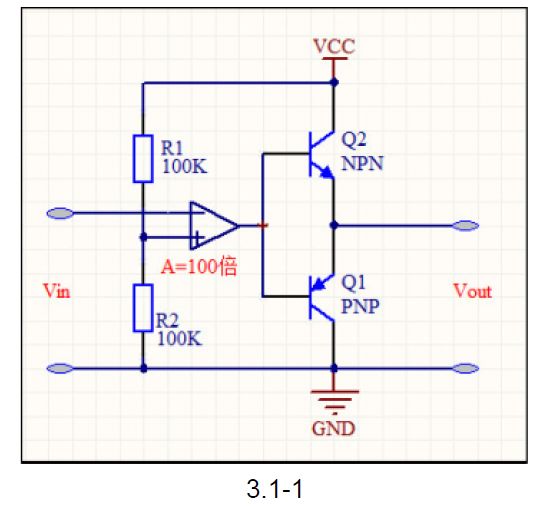

如图3.1-1,理想状态下, Vout = 100*Vin,输出没有噪声。

3.1.2、共阻噪声最糟糕的状态

最坏的布线情况,噪声会被“加倍放大” 。Av-niose >> 1 :

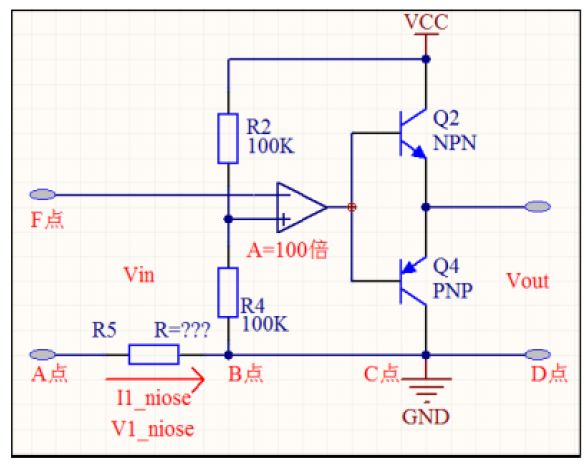

3.1-2

如图3.1-2,由于AB点在PCB板上是一段铜箔, 不可避免存在阻抗(虽然铜的电阻率极小),假设其阻抗为R5。interwetten与威廉的赔率体系 输入信号的回路经过A——B段,当有数字电流I1_niose 地回路流经A——B点时, R5既是模拟信号的回流地电阻,也是数字电路信号的回流地电阻,这个导线电阻由模拟、数字“共享” ,故称为共阻。而数字信号经过R5会产生V1_niose,这个V1_niose电压将会叠加在干净的模拟输入信号上,造成输入信号的污染(干扰) ,故把这种—— 因为有共同回流路径而产生的干扰现象叫“共阻干扰” 。

由于该电路放大的是BF端的电压。(而不仅仅是AF端,如果不明白这一点,必须重新学习功放!)所以Vout=(Vin+V1_niose)*100,其中输出噪声部分的信号是V1_niose*100!——可见,噪声被加倍放大了!!!这是共阻噪声最为严重的一种状况!

经验性现象解释:有人说:铜的电阻率这么低,即使V1_niose 放大一百倍也听不到,因为用示波器根本没有看到噪声的存在!而且数字噪声一般不在20—— 20KHz人耳可听见范围!

这个说法好像有道理,但是实际和理论都是不对的。原因如下: (1)人耳朵在安静环境中, 通过耳机,人们能清楚地听到毫伏级(几毫伏)的音频噪声信号,而普通示波器一般无法捕捉到这么微弱的波形。因为普通的数字示波器接上探头后显示在屏幕上的噪声电平有20mV 左右,非常昂贵的示波器在拔掉探头的情况下,显示在屏幕上的底噪才可能小于1mV。所以人耳朵能听到噪声但是示波器看不到,这很正常。(2)即使数字电路本身工作频率远超过20KHz,但MCU内部模块间的启动关闭动作的频率有可能落在音频范围。而且,即使大于20KHz的数字信号,经过导线的分布电感与分布电容“滤波”后,形成V1_niose 将落在音频范围。这是我们能听到数字噪声的原因。

3.1.3、共阻噪声1:1 放大输出

干扰不被放大、直接呈现在输出端。Av-niose = 1:

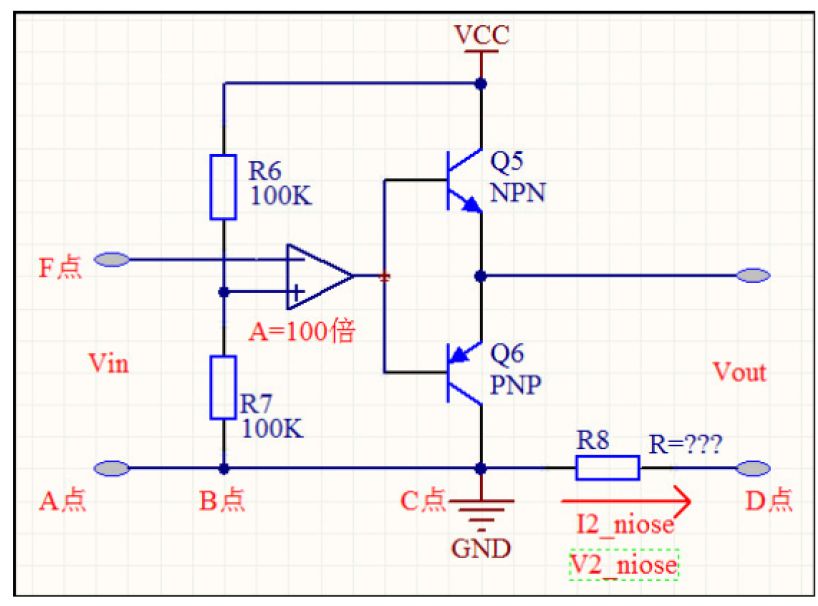

3.1-3

如图,若数字噪声只流过R8,那么Vout=Vin*100 + V2_niose,存在数字噪声,但是噪声没有被放大, 所以一般情况下, 数字噪声不明显, 只是是在安静的环境中可能可以听得到。

3.1.4、共阻干扰被衰减后输出

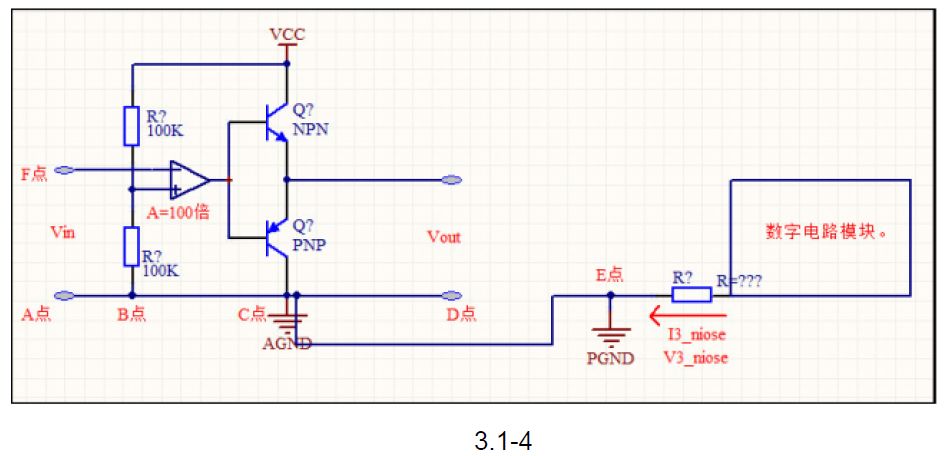

干扰会被功放器件抑制, Av-niose << 1 :

如图,假如在数字电路端单点接地。那么,数字噪声V3_niose 可以直接回流到电源,并没有流经功放区域, (其实深究起来,还是有非常微小的部分噪声流经EC段PCB,并从其他路径构成回路,但是这个影响非常小。回路路径如何形成?根据“噪声的起源”章节中的内容,其实足以领悟出来。)所以不会造成地线的共阻干扰噪声。但是,有两点值得担心的:

(1)电源不是理想的电源,会存在“内阻” ,所以数字电路会通过“干扰公共的电源从而干扰功放” ——幸运的是, 这个干扰非常小, 一般情况下都不会引起系统出现噪声,原因是:功放的电源纹波抑制比一般非常高!

(2)C与E之间同样是铜箔,实际上也存在内阻!这段地线也会产生共阻干扰。但是,实际上采用这种布线方式也不会出现干扰问题,原因是:一、其阻抗引起的干扰相当于电源抖动的干扰, 而功放有一定的电源纹波抑制能力(这个是地纹波抑制, 实际测试过的一些芯片, 都是电源纹波抑制能力比地纹波抑制能力好,这应该与Bypass电路有关,有兴趣者可以深究) 。二、这个干扰一般是声音较大时干扰才比较大,但是声音大后,噪声会被音乐“盖住” ,所以人感受不到噪声的存在。

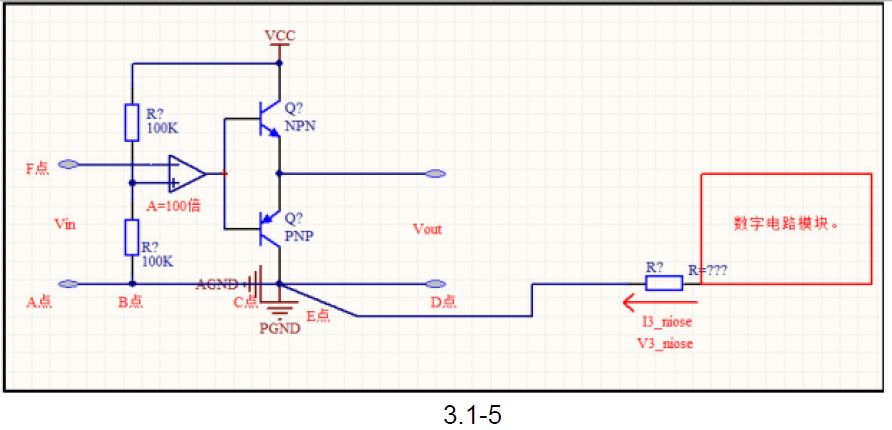

3.1.5、在电路板上不会存在地噪声

如图3.1-5,电池、数字地、模拟地的单点接地点都接在C、E点的重合处。这样接地,在电路板上不会出现噪声, Av-niose=0 。(但是,电池接上后,同样会产生“ 3.1.4”的类似情况,因为每个电源都有内阻。这个读者自行构建模型分析!)

无论如何, 对于图中的电路, 这已经是最好的接地方式了! 而且这种接地方式从未出现过噪声!

3.2、敏感点与不敏感点

由3.1 的内容知道, PCB走线不当,噪声会被“成倍放大” 、或会被“ 1 倍放大”。产生这种状况说明:对于音频功放放大电路, PCB上存在“地噪声敏感点和不敏感点”(或者说是敏感段) 。

3.2.1、地噪声敏感段PCB

图3.1-2 的AB段的噪声会被成倍放大, 所以AB段是“地噪声敏感段PCB”,经过敏感段PCB的数字地噪声将会被“加倍放大”后输出。

之所以会被加倍放大,是因为噪声信号经过功放的前端放大电路的地回流,这段PCB对应于实际应用中的很多功放的“ Bypass电容接地点(如图3.1-2 中B点)与功率地(如图3.1-2 中C点)之间的PCB”。也就是: BC间的PCB连走线极有可能成为地噪声敏感段PCB。

3.2.2、地噪声不敏感段PCB

图3.1-3 的CD段是地不敏感段PCB,因为经过这一段PCB的噪声放大倍数是1,噪声不会被加倍放大。其原因在于地噪声没有经过功放的前级放大区域,所以噪声信号只会原原本本地在喇叭端输出。

4、单点接地

本节重点:第3 节共阻干扰的各种案例中,存在地噪声可能会流经“敏感

段PCB”这个现象。所以为了最大地减小地噪声,要单点接地,让噪声不要经过敏感段PCB。

4.1、单点接地与“敏感信号段”的联系

细心的读者已经发现, 第三节已经存在单点接地。单点接地不应单纯理解为:在PCB上有一个物理的接地点;而应该理解为:在PCB上有一个接地点,而且不同性质的地回流信号(比如模拟回流和数字回流) 不会存在这个接地点以外的“公共路径”(公共路径—— 即地线上数字与模拟公有的PCB电阻“ R5”,前面已经解释过)。

图“ 3.1.4 和3.1.5”其实就是单点接地的情况,所以此处不再赘言。本节重点写:如何去真正理解单点接地。

4.2、如何去理解单点接地

单点接地的思想,在《印刷电路板排版设计》有很详细的讲解。很老的书,工艺可能和现在不同, 但其设计思想不变! 而且,作者认为这是国产少见的不是“ Ctrl + C”和“ Ctrl + V”的书。郑诗卫写的,感谢郑老前辈!

4.2.1、理解原理的重要性(经验性废话)

平时我们经常会听到“单点接地”这个词,很多人说“去掉数模混合电路噪声的终极武器就是单点接地” 。但是某日有个鞋童泪流满面的奔过来嚎叫:我已经单点接地了,可是噪声尚在· ·····

何故?

额!哥!不是单点接地就可以去掉噪声,而是要“正确的单点接地”才能够去掉噪声。正确的数字、模拟前端、电池、功率地的单点接地点是:功放的功率地引脚(或者功率地、功放电源的去耦电容引脚。)

例如,我们在设计一个实在的产品时, 存在很多互斥不可兼得的“布线定理”时,我们如何取舍? 究竟是让这个电路符合A 法则、放弃B 法则好呢,还是符合B法则、放弃A 法则好呢? 要做正确做出这种判断,就要求我们清楚:什么是影响最大的、而什么的影响几乎可以忽略不计的。

所以,除了实践,还得最终把握其原理。

4.2.2、例说:了解敏感信号区的方法

使用前想评估某个特定芯片有哪些特征,需要一定的理论+ 专业常识,推断出芯片内部的构造,从而可以判断“哪些是信号敏感点,哪些不是敏感点” 。

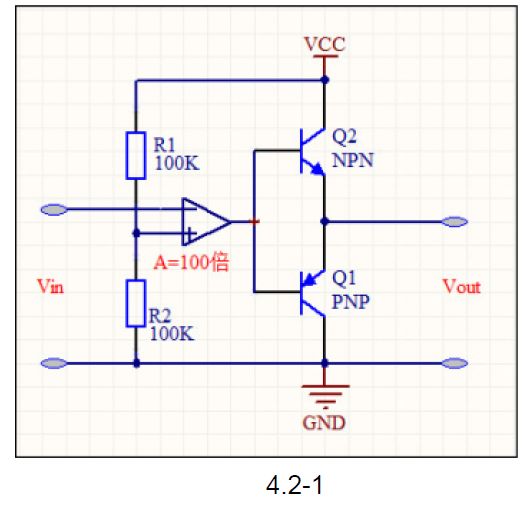

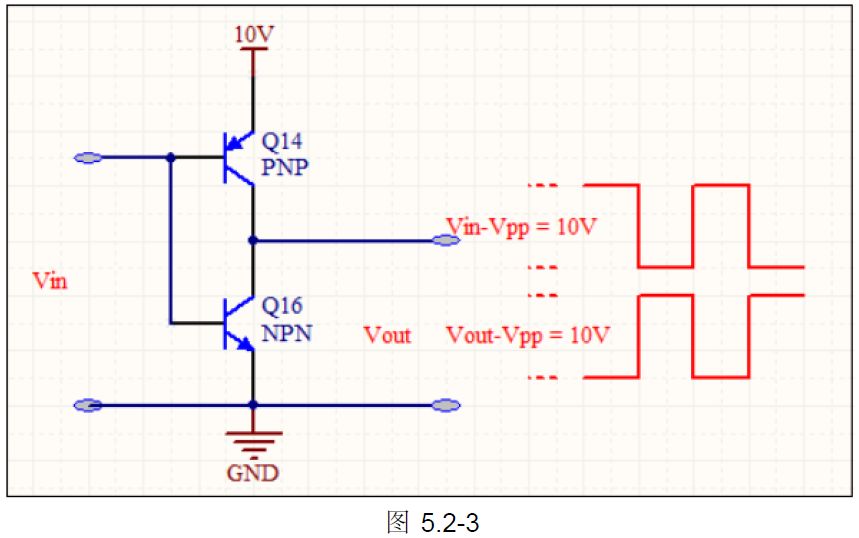

以功放为例,目前绝大多数AB类音频功放内部构造如下图所示。前端为电压放大,相当于运放,一般由偏置电路与共射放大电路组成,该部分功能是:对输入的信号(包括噪声)进行电压放大。而后级为射极跟随电路,一般电压放大倍数为1(没有电压放大能力) ,只是增强了输出电流驱动能力。

图中的运放“ +”端,通常相当于功放的“ Bypass”引脚;而Q1的接地点的

地相当于功放的功率地引脚。Bypass引脚通常接一个去耦电容到地, 该电容的地到功放的功率地间的PCB走线相当于图3.1-2 中的AC段PCB。假如这段PCB存在噪声,那么相当于噪声混进了功放前级的运放,噪声将会被“极大地放大” !

这就是“噪声混进了信号敏感段PCB”。

所以单点接地的目的是:不让噪声地回流经过“敏感信号区的地线区域” 。

5、理论的延伸

本节重点:从单点接地引出单点接电源,从单点接电源的“不够普遍”这个现象探讨“电源纹波抑制比” 。从原理上论证: 模拟芯片电源纹波抑制比较强,而数字芯片无电源纹波抑制能力。

5.1、既然有单点接地,那么有没有“单点接电源”?

显然,答案是肯定的。

但奇怪的是:为什么总是听到前辈强调“单点接地” ,却很少听到他们强调“单点接电源”?

日常生活常见的一个现象是: 当一个事情经常出现或者出现的后果十分严重时,经历过的人们时常会把它挂在嘴边, 没经历过的人也能耳熟能详。但当事情出现的概率很小、或者后果影响很小时,人们时常会把它忽略掉。

同样,“单点接电源”也是如此,电源当然会产生共阻噪声。但是在音频功放中,其影响通常非常小(原因是功放电源的纹波抑制比高) ,即在喇叭端一般听不到电源的纹波噪声;而且在电源端的共阻干扰不会出现“噪声被成倍放大”的情况(因为Bypass电容接到地,而不是接到电源) 。所以一般情下电源存在共阻干扰,但是在输出音频上听不到,所以在音频领域一般不会引起很大的重视。(这是对集成芯片而言, 对于分立元件搭建的功放电路, 有些构造对电源纹波还是非常敏感的。)

注意:电源处理不好会加重模块间的干扰,增加数字电路的电磁辐射。所以,在数字电路中, 必须得权衡是否要加强模块间的电源隔离(这个理论可以在“噪声的起源” 4.4 节中看到)。

5.2、讨论“电源纹波抑制”

5.2.1、综述:对电源纹波的敏感程度

模拟、数字电路通常对“电源纹波噪声”的抑制能力表现不同, 一般来讲模拟器件对电源纹波不敏感, 基本不会将电源纹波反应在输出上; 而数字电路通常会将电源纹波完全反应在输出上。

注意:模拟电路对信号噪声敏感,混进了噪声后,直接影响输出信号;数字电路对信号的噪声相对不敏感,因为即使噪声很大, IO口都能正确地判断出高低电平。

5.2.2、模拟电路电源纹波抑制能力强的原因

一般的功放和运放处理的都是模拟信号, 它们可以将信号放大、缩小N 倍,一般都有很强的电源纹波(噪声)抑制能力。至少将电源上的噪声衰减10000倍以上输出。

为什么运放等模拟器件有这么强的电源抑制能力?

归根结底,因为稳压电源、恒流源、放大区的共射放大电路、非饱和状态的射级放大电路等都有很强的电源纹波(噪声) 抑制能力—— 而运放、功放等都由这些基本电路作为其内部的偏置、放大电路单元,所以电源纹波抑制比很强。

深入的理论剖析并非一章一节可以阐明, 并且作者也自认为没有足够深厚的功底。下面将简单论述芯片内部其中一种电路模型: 为何放大区的共射电路有很强的电源纹波抑制比!

PS:请有兴趣深入研究的读者可以理解《模拟电子威廉希尔官方网站 基础》(童诗白第4版3、4 章节等相关内容)章节后,再进一步学习。

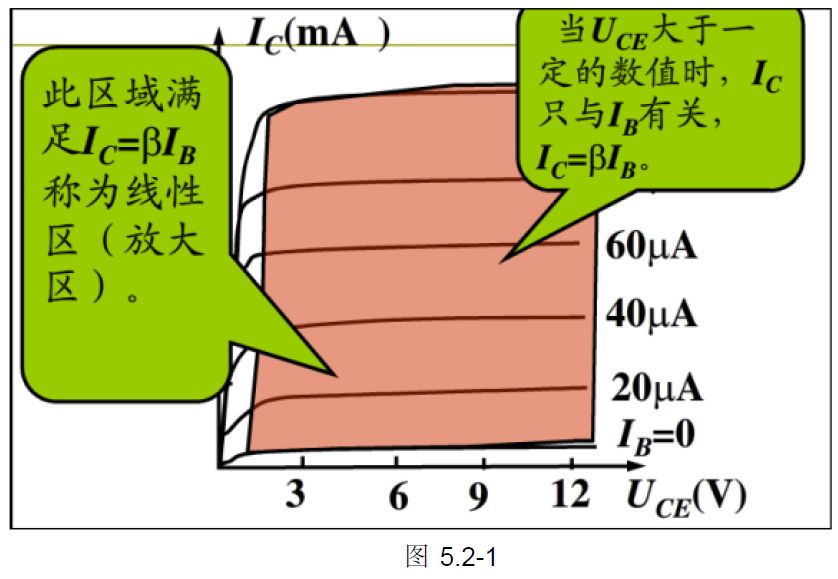

该图是经典的“三极管特征曲线图” ,该图已经蕴含了“共射放大区有很强的电源纹波抑制能力”这个信息!

真的吗?不会吧?!

我啥时候骗过你? —— 请看分析。

对于共射放大电路。假设在放大区(图中棕红色区域) ,给三极管B极提供固定的电流Ib1 = 20uA,那么即使电源电压( Uce电压)在3~9V 波动,而Ic1 基本保持不变(这个图中可以看到) 。Ic1 保持不变,意味着共射放大电路的电压输出不变!(理解这句话的前提是:理解共射放大电路。)

所以,对于图中的三极管共射放大电路,假如在B极输入一个信号Vin,即使电压在3~9V波动,输出只和输入有关,基本不受电源电压波动的影响!这表明:这个放大电路有很强的电源抑制能力!

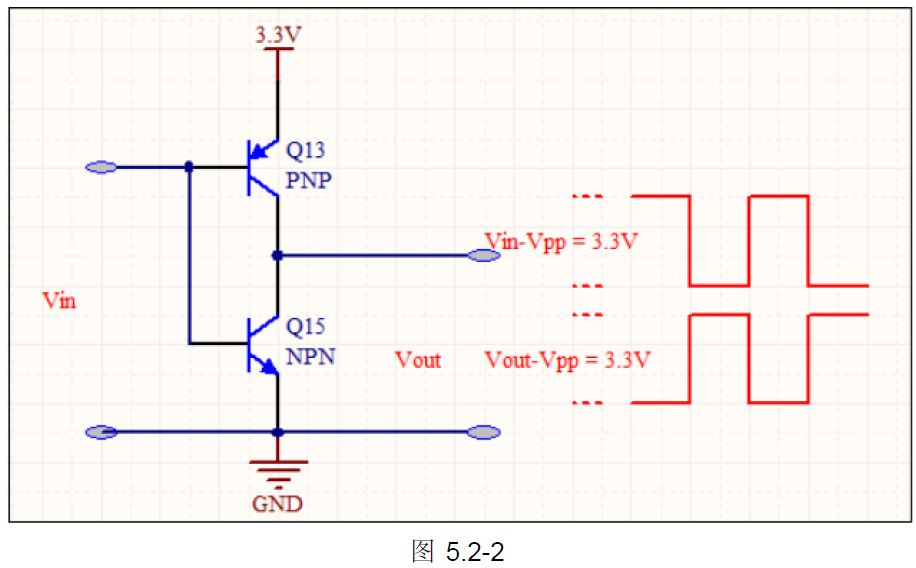

5.2.3、数字电路没有电源纹波抑制能力

小功率三级管在输出电流不是很大的情况下, 饱和导通的管压降非常小, 可以认为是0(对于这个压降问题, 有不少有了工作经验的硬件工程师也经常质疑。那么,烦请各位用使用数据验证。呵呵!)。所以,当输入为3.3V 时,输出为3.3V。

当电源电压由3.3V 变为10V 时,所有数字电路都工作在10V 电源下,每个数字门电路的电压也为10V——所以最终的结果是: Vin 和Vout 都变成一样:都是10V 输入、输出电压。

所以,由于数字电路IO 口的电压工作在饱和导通状态(不可以特殊的ECL等电路来论述),输出电压永远等于电源电压。所以电源波动毫不保留地反应在输出上,导致其电源纹波抑制能力为0. 这种特性在数字电路相互干扰的处理要十分留心。

6、本文精要

(1)因为有共同回流路径而产生的干扰现象叫“共阻干扰” 。

(2)人耳朵在安静环境中,通过耳机,人们能清楚地听到毫伏级(几毫伏)的音频噪声信号,而普通示波器一般无法捕捉到这么微弱的波形。

(3)因为共阻干扰存在地噪声的“敏感段PCB”,所以要单点接地,让噪声不要经过敏感段PCB。

(4)单点接地的思想,在《印刷电路板排版设计》有很详细的讲解。(作者:郑诗卫)

(5)一般来讲模拟器件对电源纹波不敏感, 基本不会将电源纹波反应在输出上;而数字电路通常会将电源纹波完全反应在输出上。

-

pcb

+关注

关注

4319文章

23096浏览量

397816 -

电路板

+关注

关注

140文章

4960浏览量

97817 -

地线

+关注

关注

10文章

219浏览量

26790

原文标题:写给硬件初学者--地线干扰的共阻干扰

文章出处:【微信号:fcsde-sh,微信公众号:fcsde-sh】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

地线干扰的共阻干扰深度解析(pcb电路板设计必知)

地线干扰的共阻干扰深度解析(pcb电路板设计必知)

评论