一、CAN总线协议介绍

CAN是 Controller Area Network 的缩写(以下称为 CAN ),是 ISO 国际标准化的串行通信协议。可以用来满足“多总线通信时,线束的数量过多”、“通过多个 LAN ,进行大量数据的高速通信”的需要。它的出现为分布式控制系统实现各节点之间实时、可靠的数据通信提供了强有力的威廉希尔官方网站 支持。

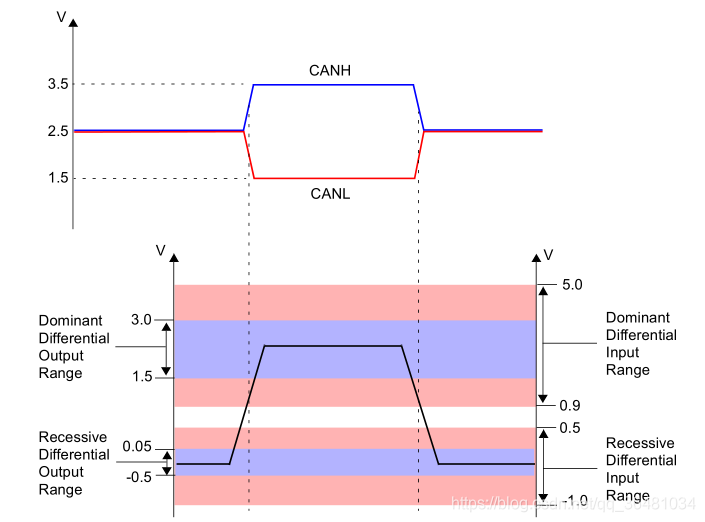

CAN控制器根据两根线上的电位差来判断总线电平。总线电平分为显性电平和隐性电平,二者必居其一。发送方通过使总线电平发生变化,将消息发送给接收方。

CAN协议具有以下特点:

CAN 总线是一种多主总线,总线上任意节点可在任意时刻主动地向网络上其他节点发送信息而不分主次,因此可在各节点之间实现自由通信。

CAN 总线采用非破坏性总线仲裁威廉希尔官方网站 。当多个节点同时向总线发送信息时,优先级低的节点会主动退出发送,而最高优先级的节点可以不受影响地继续传输数据,从而大大节省总线冲突的仲裁时间。即使在网络负载很重的情况下也不会发生网络瘫痪情况。

CAN 总线的通信介质可以是双绞线、同轴电缆或光导纤维,选择灵活。

CAN 总线的通信速率可达 1Mbit/s(此时通信距离最长为 40 米),通信距离最远可达 10km(速率在 5kbit/s 以下)。

CAN 总线上的节点信息分成不同的优先级,可以满足不同级别的实时要求,高优先级的数据可以在 134μs 内得到传输。

CAN 总线通过报文滤波即可实现点对点、一点对多点及全局广播等几种方式传送数据,无需专门的调度。

CAN 总线的数据采用短帧结构,传输时间短,受干扰概率低,具有极好的检错效果。

CAN 总线采用 CRC 检验并可提供相应的错误处理功能,保证了数据通信的可靠性。

CAN 总线上的器件可被置于无任何内部活动的睡眠方式,相当于未连接到总线上,可以有效降低系统功耗。

CAN总线采用差分信号传输,通常情况下只需要两根信号线就可以进行正常的通信。在差分信号中,逻辑0和逻辑1是用两根差分信号线的电压差来表示。当处于逻辑1,CAN_H和CAN_L的电压差小于0.5V,称为隐性电平(Recessive);当处于逻辑0,CAN_H和CAN_L的电压差大于0.9V,称为显性电平(Dominant)。

CAN有四种帧类型:

◆ 数据帧:发送单元向接收单元传送数据的帧

◆ 远程帧:总线单元发出远程帧,请求发送具有同一识别符的数据帧

◆ 错误帧:由检测到错误的任何节点发送的帧

◆ 过载帧:在数据或远程帧之间注入延迟的帧

数据帧是唯一实际传输数据的帧,结构上由7个段组成,其中根据仲裁段ID码长度的不同,分为标准帧(CAN2.0A)和扩展帧(CAN2.0B):

➢ 标准帧格式:具有11个标识符位

➢ 扩展帧格式:具有29个标识符位

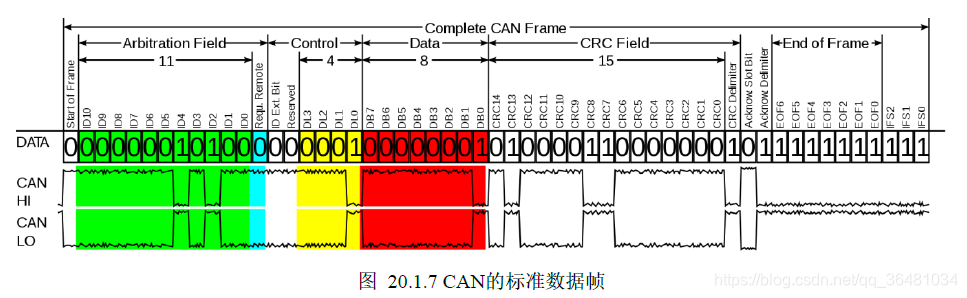

标准数据帧的构成如下图所示:

数据帧一般由7个段构成,即:

(1)帧起始:表示数据帧开始的段。

(2)仲裁段:表示该帧优先级的段。

(3)控制段:表示数据的字节数及保留位的段。

(4)数据段:数据的内容,一帧可发送0~8个字节的数据。

(5)CRC段:检查帧的传输错误的段。

(6)ACK段:表示确认正常接收的段。

(7)帧结束:表示数据帧结束的段。

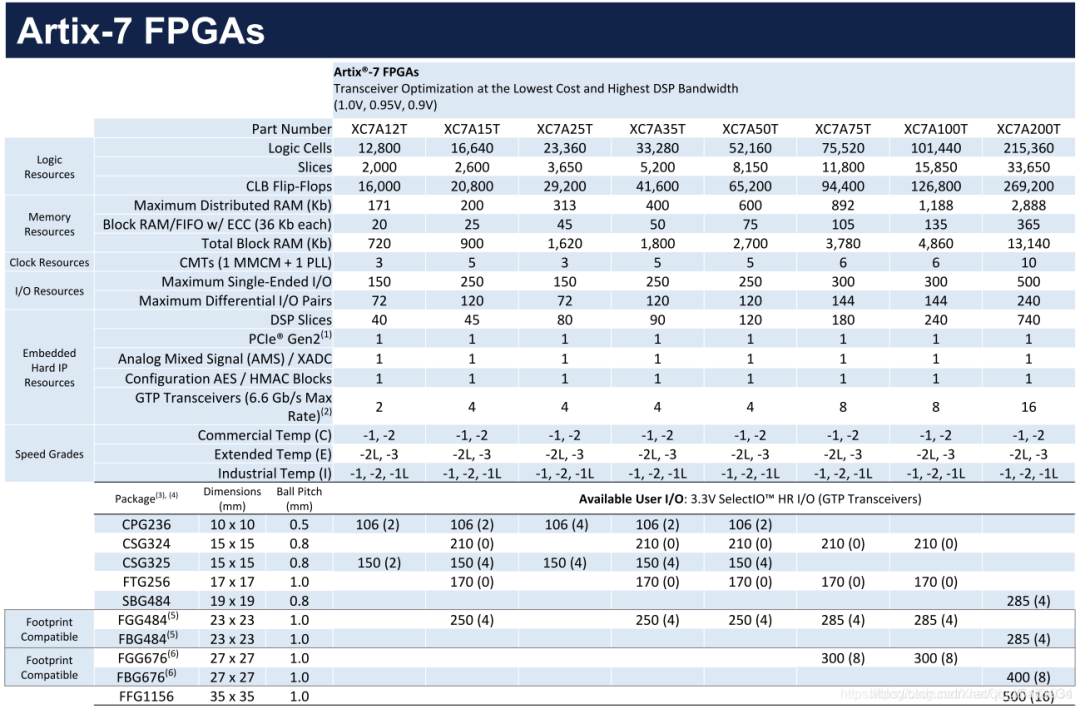

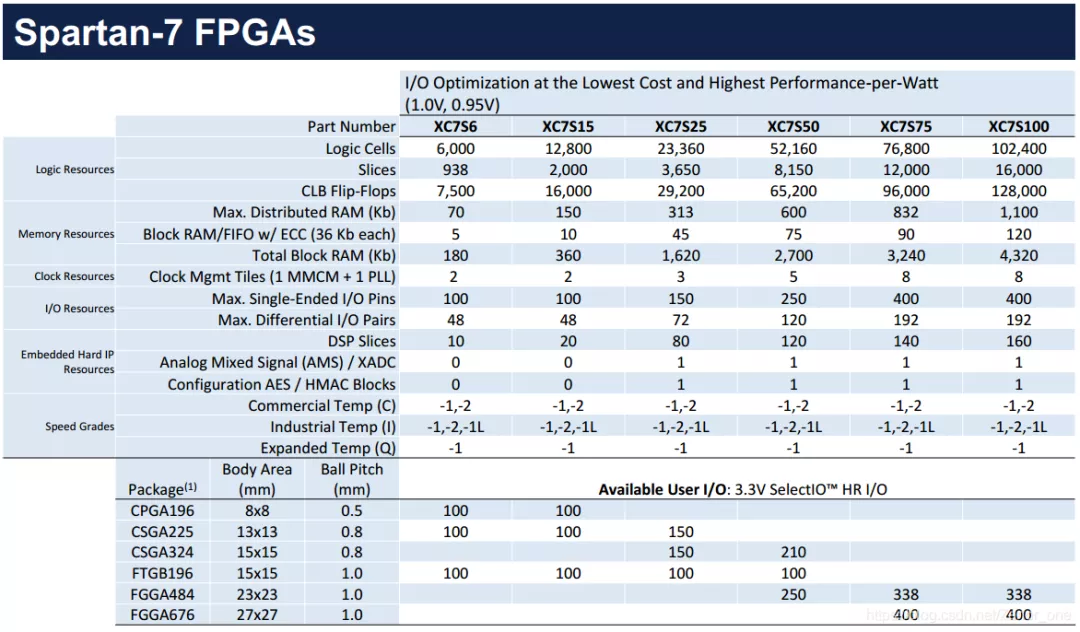

Artix7系列是7系列中的普通青年,相对Spartan7系列则增加了串行收发器和DSP功能,其逻辑容量也更大,适合逻辑一些稍微复杂的中低端应用。

三、FPGA的相关设计介绍

设计思路一:在FPGA内部编写CAN通信控制器

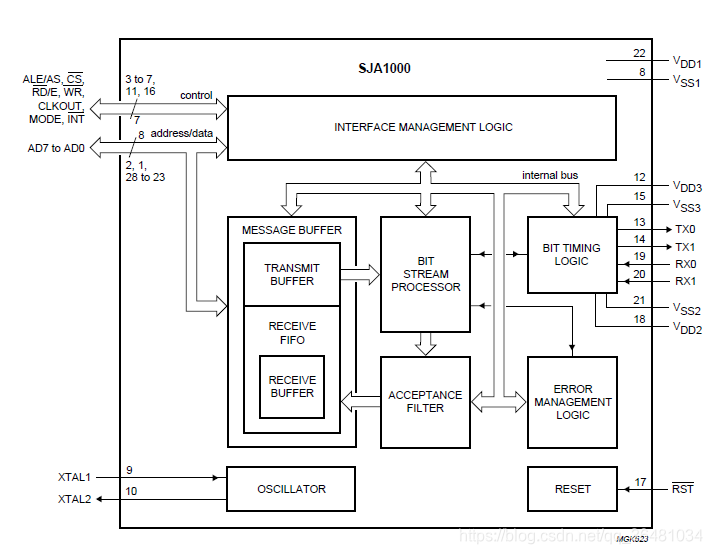

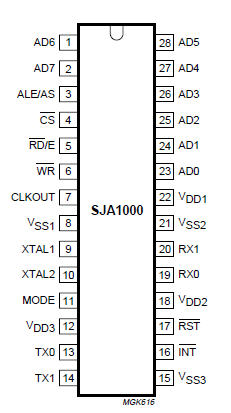

采用这个设计方案,本质上是在FPGA内部设计了一款CAN通信控制芯片。威廉希尔官方网站 门槛较高。下面这个设计实例仿照的是SJA1000 CAN通信控制器的工作流程,用Verilog语言完成了CAN控制接口的开发。

CAN 总线的通信协议由 CAN 通信控制器完成。CAN 通信控制器由实现 CAN 总线协议部分和微控制器部分的电路组成。下面将通过一个实例讲解如何用 FPGA 实现 CAN 通信控制器的功能。这个实例从功能和结构上完全参照 SJA 1000 CAN 通信控制器。

网址一:基于FPGA的CAN总线控制器的设计(上) - 知乎 (zhihu.com)

网址二:基于FPGA的CAN总线控制器的设计(中) - 知乎 (zhihu.com)

网址三:基于FPGA的CAN总线控制器的设计(下) - 知乎 (zhihu.com)

上述资料是按照SJA1000 CAN通信控制器的内部结构用FPGA进行了重新设计。

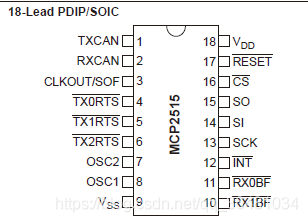

设计思路二:用FPGA通过串口或者SPI去配置外部的CAN控制器芯片实现通信。

这个设计方案一般用在单片机作主控的项目中,如果用FPGA作主控,有这么几个缺点,成本高、硬件设计繁琐、受限于控制芯片的性能和发挥不出FPGA的性能。

CAN通信控制芯片:

MCP2515(SPI通信)

SJA1000

CAN接口驱动芯片:

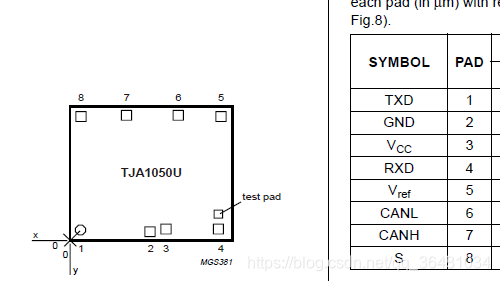

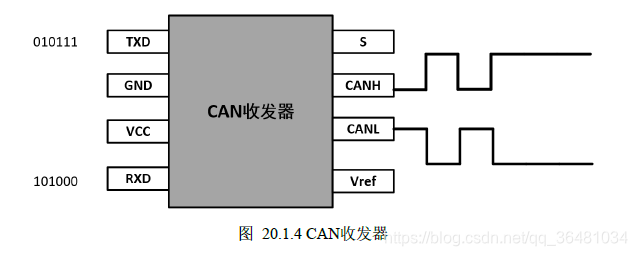

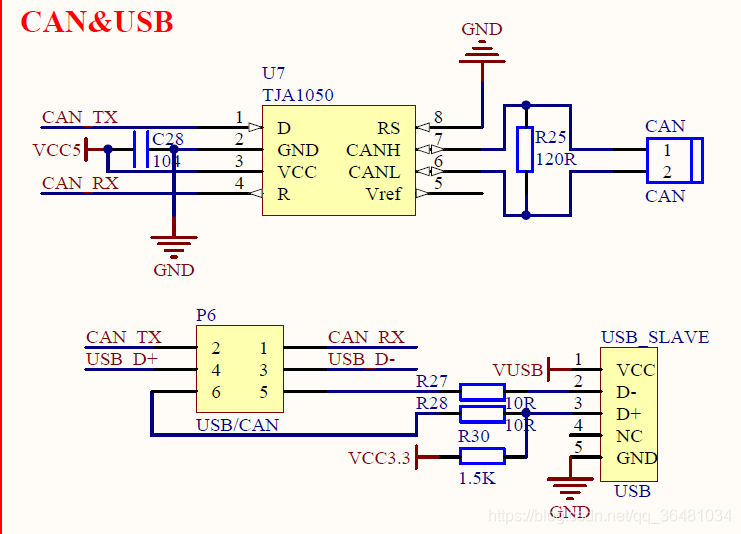

TJA1050芯片引脚图

常用的外设电路设计

如上图所示,CAN_TX和CAN_RX接CAN通信控制芯片,实现对驱动芯片转换后的信息流的处理。

-

FPGA

+关注

关注

1629文章

21729浏览量

603013 -

CAN总线

+关注

关注

145文章

1947浏览量

130728 -

Xilinx

+关注

关注

71文章

2167浏览量

121307

原文标题:基于Xilinx的A7系列FPGA的CAN总线协议开发

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Xilinx 7系列FPGA的时钟结构解析

cmos的slvs-ec协议40针引脚该如何连接到xilinx a7开发版上?

【Artix-7 50T FPGA申请】FPGA由Altera转Xilinx系列笔记

xilinx A7 200t PCI协议使用问题

Xilinx 7系列FPGA管脚是如何定义的?

Xilinx 7系列与Ultrascale系列FPGA的区别

基于Xilinx的A7系列FPGA的CAN总线协议开发

基于Xilinx的A7系列FPGA的CAN总线协议开发

评论