在现代电子设计自动化(EDA)领域,Verilog作为一种硬件描述语言,已经成为数字电路设计和验证的标准工具。它允许设计师以高级抽象的方式定义电路的行为和结构,从而简化了从概念到硅片的整个设计流程。然而,在实际应用中,设计师可能会遇到各种问题,这些问题可能会影响仿真的准确性和设计的可靠性。

Verilog电路仿真常见问题

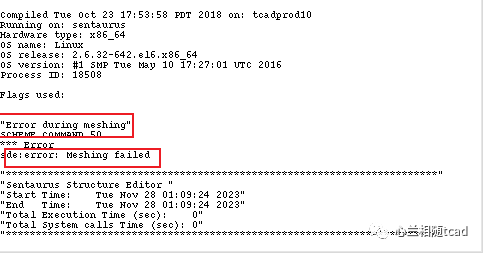

- 仿真环境的搭建问题

- 仿真环境的搭建是进行Verilog仿真的第一步。设计师需要选择合适的仿真工具,并确保所有必要的库和模型都被正确加载。环境搭建不当可能导致仿真结果不准确或仿真失败。

- 时序问题

- Verilog中的时序问题包括时钟域交叉、亚稳态和时钟偏斜等。这些问题可能导致电路在实际硬件中无法正常工作,即使仿真结果显示正常。

- 竞争条件和冒险

- 竞争条件发生在多个信号同时尝试驱动同一节点时,而冒险则是由于信号传播延迟导致的短暂不稳定状态。这些问题在仿真中可能不明显,但在实际硬件中可能导致功能错误。

- 资源利用和优化问题

- 在进行Verilog仿真时,设计师需要考虑资源的利用和优化,以确保设计的可合成性和性能。不恰当的资源分配可能导致硬件资源浪费或性能瓶颈。

- 测试和验证问题

- 测试和验证是确保电路设计正确性的关键步骤。在Verilog仿真中,设计师需要编写有效的测试用例来覆盖所有可能的场景。测试不充分可能导致设计中的缺陷未被发现。

Verilog在芯片设计中的应用

- 行为级建模

- Verilog允许设计师在行为级对电路进行建模,这使得可以在不涉及具体硬件细节的情况下,对电路的功能进行描述和验证。

- RTL设计和验证

- 在寄存器传输级(RTL)设计中,Verilog用于描述电路的逻辑和控制流。设计师可以利用Verilog的模块化特性来构建复杂的电路,并进行详细的验证。

- 时序分析

- Verilog提供了时序分析工具,可以帮助设计师预测电路在不同时钟频率下的行为,以及识别潜在的时序问题。

- 综合和优化

- Verilog设计可以被综合到具体的硬件描述,如门级或晶体管级。在这个过程中,Verilog的优化指令可以帮助设计师提高电路的性能和效率。

- 可测试性设计(DFT)

- Verilog支持可测试性设计,允许设计师在设计阶段就考虑测试的需求,从而降低后期测试的成本和复杂性。

- 功耗分析

- 随着功耗成为芯片设计中的一个重要考虑因素,Verilog提供了工具来分析和优化设计的功耗。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

芯片

+关注

关注

455文章

50721浏览量

423165 -

硬件

+关注

关注

11文章

3315浏览量

66202 -

Verilog

+关注

关注

28文章

1351浏览量

110077 -

电路仿真

+关注

关注

36文章

208浏览量

95679

发布评论请先 登录

相关推荐

Cadence原理图仿真常见问题

`本文章介绍我在PSpice原理图仿真的常见问题及其解决方法。1、出现错误提示:SubcircuitADA4817 used by X_U1 is undefined解决方法是我在ht

发表于 12-02 09:51

gazebo仿真常见问题遇见的坑记录

大家好,我是一到周五就很开心的小鱼。今天旧话重提,说一说做机器人仿真的时候遇到的一些问题,这里小鱼基于之前写过的文章,再总结一次。1.gazebo仿真常见问题以下的坑,是从小鱼自己的悲惨经历

发表于 09-15 06:42

基于Verilog的顺序状态逻辑FSM的设计与仿真

基于Verilog的顺序状态逻辑FSM的设计与仿真

硬件描述语言Verilog为数字系统设计人员提供了一种在广泛抽象层次上描述数字系统的方式,同时,为计算机辅助设计工具

发表于 02-04 09:32

•1883次阅读

如何使用Icarus Verilog+GTKWave来进行verilog文件的编译和仿真

本文将介绍如何使用Icarus Verilog+GTKWave来进行verilog文件的编译和仿真。 Icarus Verilog Icarus V

FPGA CPLD中的Verilog设计小技巧

FPGA CPLD中的Verilog设计小技巧(肇庆理士电源威廉希尔官方网站

有限)-FPGA CPLD中的Verilog设计小技巧

发表于 09-18 16:49

•37次下载

从仿真器的角度理解Verilog语言1

要想深入理解Verilog就必须正视Verilog语言同时具备硬件特性和软件特性。在当下的教学过程中,教师和教材都过于强调Verilog语言的硬件特性和可综合特性。将

verilog中initial和always的区别

Verilog是一种硬件描述语言(HDL),用于设计和模拟数字电路。在Verilog中,关键字initial和always都是用于描述

verilog inout用法与仿真

Verilog语言是一种硬件描述语言(HDL),用于描述数字逻辑电路和系统。它是一种非常强大且广泛使用的语言,在数字电路设计中扮演着重要的角色。其中, inout 是

电路仿真软件如何使用 电路仿真软件操作流程

第一步是下载电路仿真软件,并按照安装向导的提示完成安装过程。常见的电路仿真软件有SPICE、Multisim、PSpice等。在安装过程中

Verilog 测试平台设计方法 Verilog FPGA开发指南

Verilog测试平台设计方法是Verilog FPGA开发中的重要环节,它用于验证Verilog设计的正确性和性能。以下是一个详细的Verilog

Verilog 与 ASIC 设计的关系 Verilog 代码优化技巧

,Verilog在ASIC设计中的作用主要体现在以下几个方面: 逻辑设计 :使用Verilog可以描述数字电路的行为和逻辑结构,包括输入输出

Verilog 电路仿真常见问题 Verilog 在芯片设计中的应用

Verilog 电路仿真常见问题 Verilog 在芯片设计中的应用

评论