电子发烧友网报道(文/梁浩斌)博通最近推出了3.5D XDSiP的芯片封装平台威廉希尔官方网站

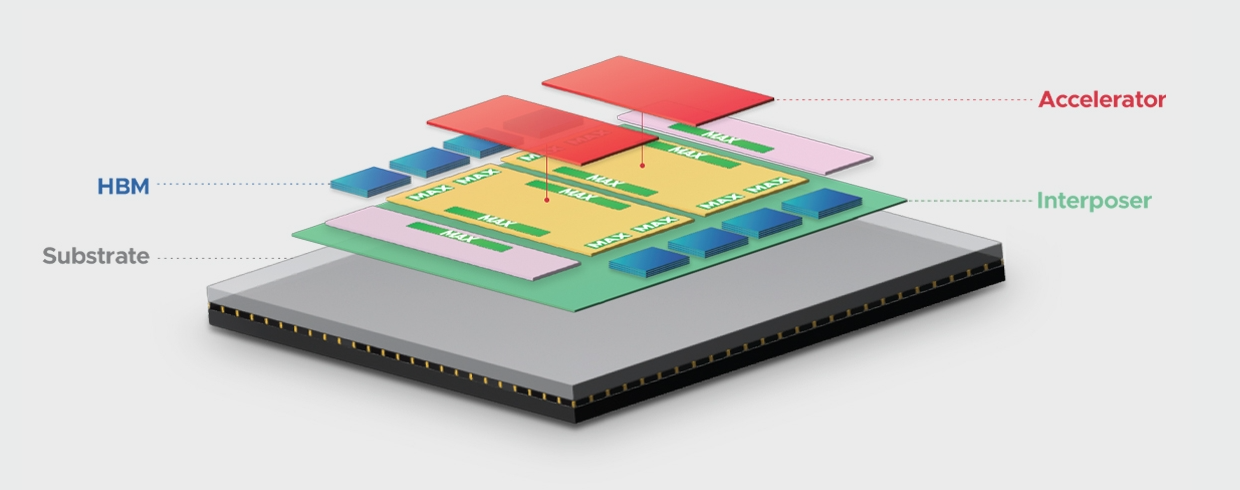

,面向下一代高性能AI、HPC应用的定制XPU和ASIC。3.5D XDSiP的最大亮点,在于可以将超过6000平方毫米的3D堆叠硅晶片和12个HBM模块集成到一个系统级封装中。这是什么概念?

目前手机移动端的旗舰处理器骁龙8Elite核心面积是124.1平方毫米;英伟达H200核心面积1526平方毫米;今年英伟达推出的首款Blackwell架构GPU B200,采用双die合封,核心面积也达到1600平方毫米左右。也就是说博通的3.5D XDSiP平台,可以支持近4个B200核心集成在一个封装中。

那么这么“巨大”的芯片是怎么封装的,市场上真的需要这么大规模的芯片吗?

2.5D封装、3D堆栈、F2F堆叠结合,首批产品2026上市

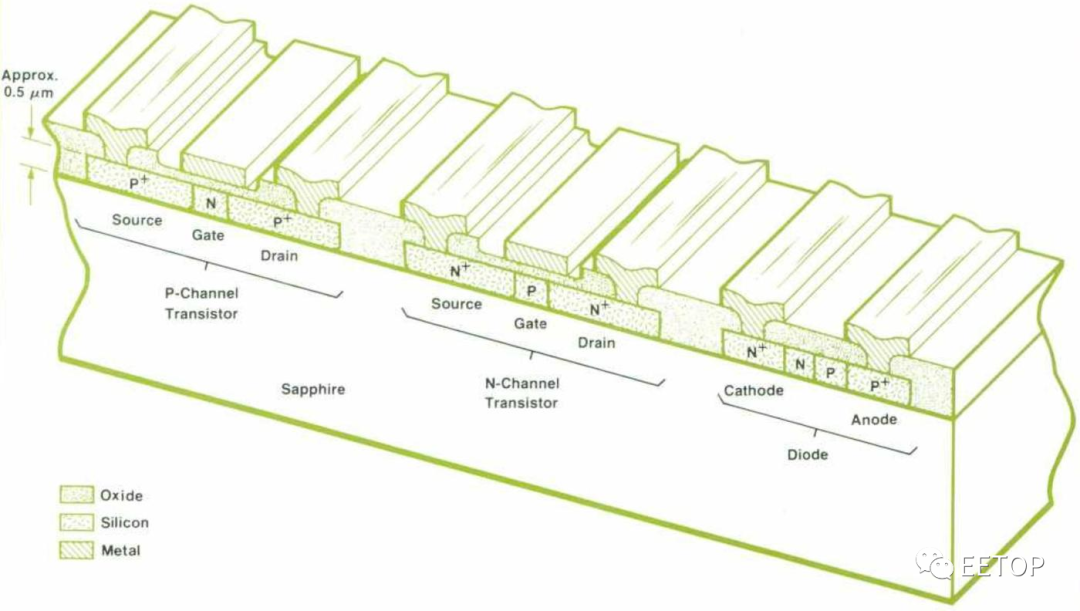

图源:博通

随着摩尔定律的进一步减缓,先进封装在大规模计算集群中XPU上的应用已经成为了业界共识,在AI计算中,XPU需要计算、内存、I/O等功能的复杂集成,以最大限度地降低功耗和成本。

而博通的3.5D XDSiP平台,作为用于定制计算芯片的平台,优势主要包括:

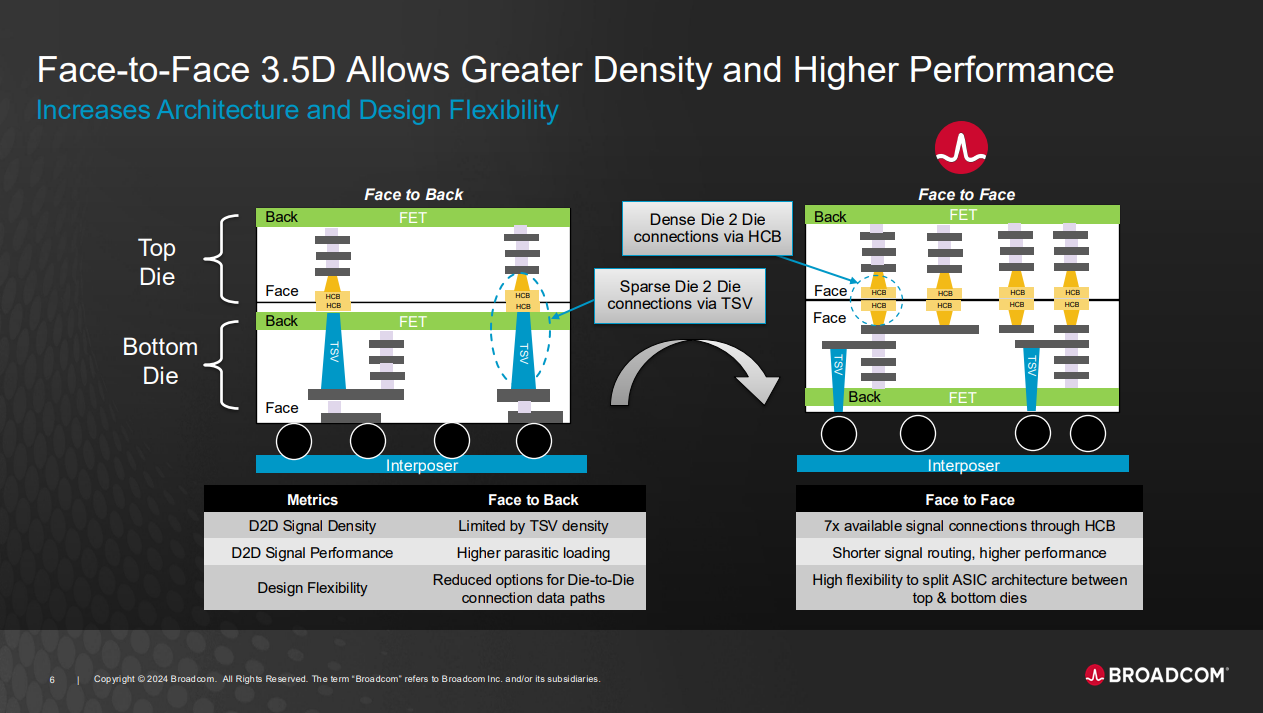

图源:博通

增强的互连密度:与传统采用硅通孔TVS的F2B(面到背)的威廉希尔官方网站

相比,3.5D XDSiP采用HCB(混合铜键合)以F2F(面对面)的方式将逻辑芯片堆叠,堆叠芯片之间的信号密度提高了7倍;

高能效:通过利用3D HCB代替平面芯片到芯片物理接口,芯片到芯片接口的功耗降低了90%;

低延迟:最大限度地减少3D堆栈中计算、内存和I/O组件之间的延迟;

小尺寸:支持更小的转接板和封装尺寸,从而节省成本并改善封装翘曲。

这项封装威廉希尔官方网站

是博通与台积电多年合作的成果,博通ASIC产品部高级副总裁兼总经理Frank Ostojic表示:“随着我们达到摩尔定律的极限,先进封装对于下一代XPU集群至关重要。通过与我们的客户密切合作,我们在台积电和EDA合作伙伴的威廉希尔官方网站

和工具基础上创建了一个3.5D XDSiP平台。通过垂直堆叠芯片组件,Broadcom的3.5D平台使芯片设计师能够为每个组件配对正确的制造工艺,同时缩小插入器和封装尺寸,从而显著提高性能、效率和成本。”

台积电业务发展高级副总裁张晓强博士表示,台积电和博通在过去几年中密切合作,将台积电最先进的逻辑处理和3D芯片堆叠威廉希尔官方网站

与博通的设计专业知识结合在一起。

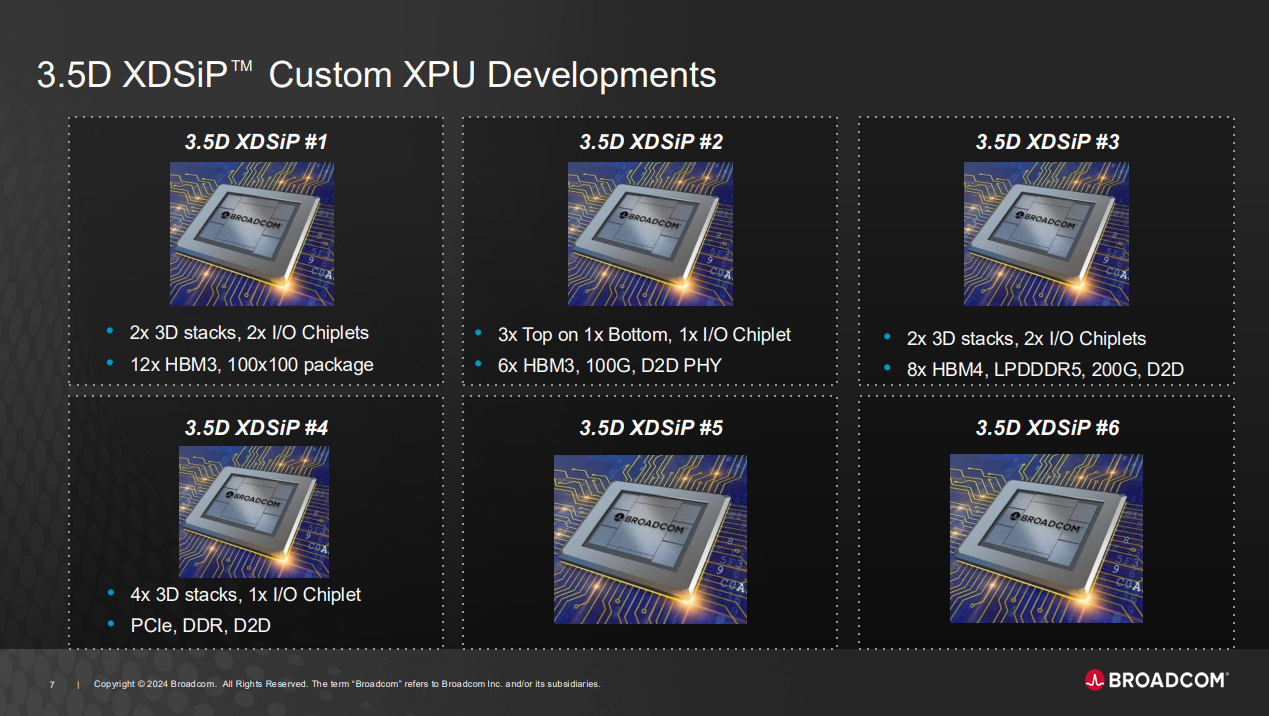

图源:博通

博通表示,3.5D XDSiP威廉希尔官方网站

目前已经被主要的AI领域客户使用,已经有6款产品正在开发中。其中富士通下一代2nm制程的Arm处理器FUJITSU-MONAKA已经确认使用博通3.5D XDSiP威廉希尔官方网站

,这款处理器面向数据中心、边缘计算等应用,据此前富士通的介绍,MONAKA每颗CPU包含一个中央的I/O die和四个3D垂直堆叠die,并集成SRAM,预计2027年出货。

使用3.5D XDSiP威廉希尔官方网站

的芯片产品,博通预计最早在2026年2月实现出货。

小结:

先进封装作为未来AI计算芯片的重要部分,博通这种大面积的芯片封装方案,能够极大程度上提高系统集成度,同时通过创新的互连方案,提高片内互连的带宽和提高能效,有望成为未来高性能处理器的一个重要方向。

-

博通

+关注

关注

35文章

4325浏览量

106889

发布评论请先 登录

相关推荐

博通股价跃升 或因苹果与博通合作开发人工智能芯片的利好刺激

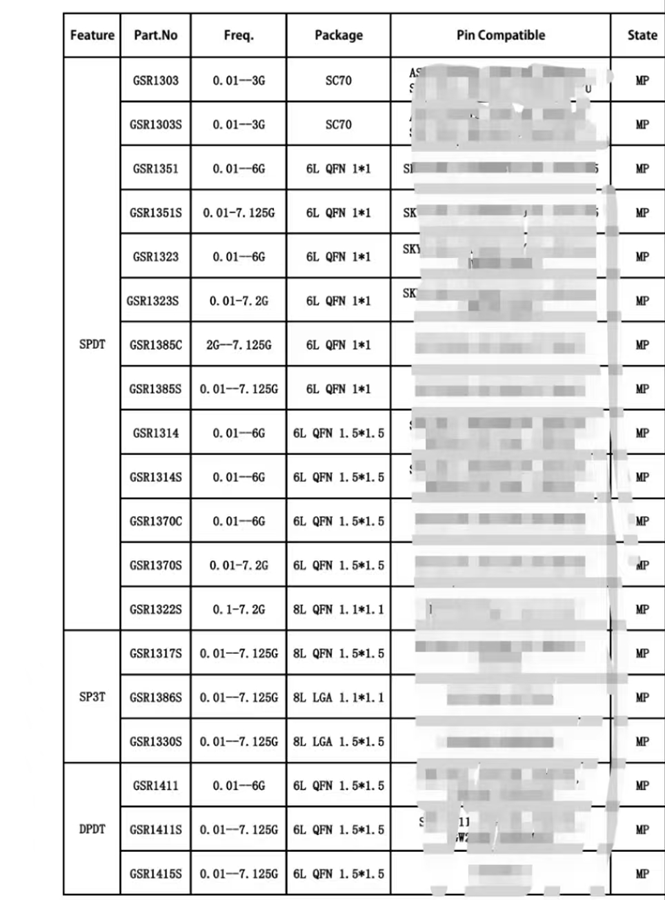

一颗射频开关的独白

什么是3.5D封装?它有哪些优势?

英伟达H200芯片将大规模交付

这是个什么芯片?

一颗改变了世界的芯片

一颗芯片面积顶4颗H200,博通推出3.5D XDSiP封装平台

一颗芯片面积顶4颗H200,博通推出3.5D XDSiP封装平台

评论