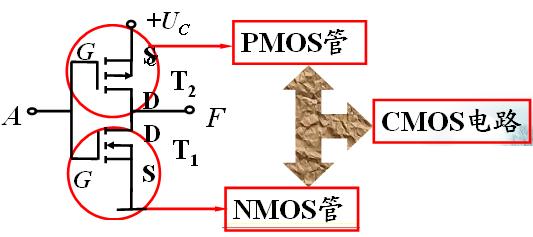

当今的电子设计领域,CMOS逻辑IC因其低功耗、高集成度和良好的噪声抑制能力而得到广泛应用。然而,要充分发挥CMOS逻辑IC的性能优势,确保系统的稳定可靠运行,必须严格遵守一系列使用注意事项。从本期芝识课堂起,芝子将向大家奉上一份详细的设计指南,帮助大家更好地避免潜在的设计陷阱和故障。

对于未使用输入引脚的处理

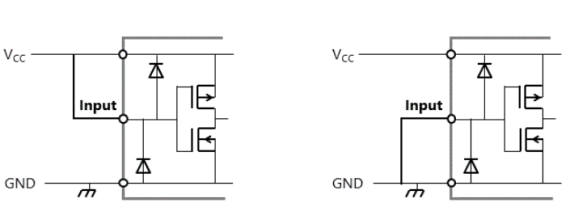

在设计和使用CMOS逻辑IC时,正确处理未使用的输入引脚是确保系统稳定性和可靠性的关键步骤。通常而言,所有未使用的输入端都应连接到VCC或GND。

连接到VCC或GND的CMOS逻辑IC的未使用输入端

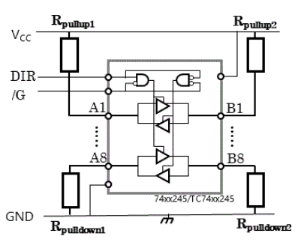

对于可配置为输出端的双向总线缓冲器来说,任何引脚(如总线引脚)应通过上拉电阻器连接到VCC或通过下拉电阻器连接到GND。同时,建议将缓冲器两端上拉或下拉至相同电位,以避免不必要的电流流动。但是,请保持总线引脚的输入引脚保持为打开状态。

双向总线缓冲器的未使用的双向引脚上拉至VCC或下拉至GND

即使采用典型的CMOS逻辑IC,仍会在电源接通瞬间,因寄生电容而产生短暂的浪涌电流。虽然这种电流通常较小(几毫安量级),但在某些敏感应用中仍需注意。通过将未使用的输入引脚连接到VCC或GND,可以有效降低这种浪涌电流的影响,提高系统可靠性。

另外,由于CMOS逻辑IC具有非常高的输入阻抗,任何开放的输入端都可能由于周围电场的影响而导致错误的输出值。此外,直通电流可能会在VCC和GND的中点流动,从而导致电流增加,这可能会导致器件损坏。除非数据手册中另有说明,否则务必将这些注意事项应用至所有不具有总线保持能力的输入端。

输入上升和下降时间规范

在数据表中,针对通用CMOS逻辑集成电路(IC)明确界定了其输入信号的上升与下降时间标准,这些标准旨在确保IC在预定的工作环境下能够稳定且高效地执行其功能。遵循这些时间规范对于防止因输出信号振荡等不利现象导致的系统故障至关重要。

当向CMOS逻辑IC的输入端施加缓慢的上升或下降信时,切换过程中可能会产生显著的电流峰值。这些峰值电流不仅可能引发电源电压(VCC)和地电位(GND)的瞬态波动(俗称“弹跳”),还可能进一步导致输出信号的振荡或功能异常。

为应对这一挑战,可使用带有施密特触发器输入的IC来缓慢更改输入。但是如果输入变化过慢,即使带有施密特触发器输入的IC仍可能无法抑制电源或信号线上的噪声,从而导致输出振荡或不稳定。

下表显示了每个系列中典型IC的上升和下降时间。

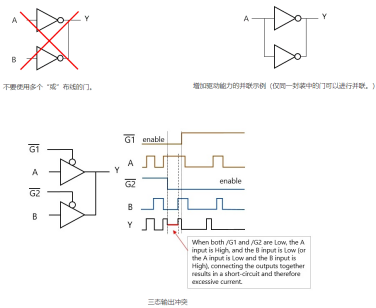

通用CMOS逻辑IC的多个输出

发生冲突(短路)

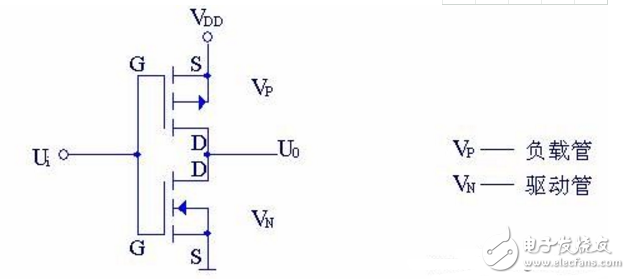

与二极管不同,典型CMOS逻辑IC的输出不能进行线或运算,除非具有三态输出。即使是具有三态输出的CMOS逻辑IC,如果同时启用,也可能会有非预期电流流动,导致IC劣化。所以在创建电路设计时,请确保在任何既定时间都不会启用多个输出。此外,如果所有的CMOS逻辑IC都被禁用(即处于高组态),而没有被上拉到VCC或下拉到GND,那么不具有总线保持功能的CMOS逻辑IC的输出就会变得不稳定。

仅同一封装中的门才可以进行线与运算,以增加驱动能力(即输出电流)。但是,建议使用高驱动IC(IO为±24 mA)。

正确使用CMOS逻辑IC不仅需要理解其电气特性,还需要关注实际应用中的细节。通过本文提供的指南,设计师可以预防常见的设计错误,提高电路的整体性能和可靠性。在后续文章中,们将继续探讨如何优化CMOS逻辑IC的性能和电容连接技巧,敬请期待。

关于东芝电子元件及存储装置株式会社

东芝电子元件及存储装置株式会社是先进的半导体和存储解决方案的领先供应商,公司累积了半个多世纪的经验和创新,为客户和合作伙伴提供分立半导体、系统LSI和HDD领域的杰出解决方案。

东芝电子元件及存储装置株式会社十分注重与客户的密切协作,旨在促进价值共创,共同开拓新市场,期待为世界各地的人们建设更美好的未来并做出贡献。

-

CMOS

+关注

关注

58文章

5706浏览量

235336 -

噪声

+关注

关注

13文章

1120浏览量

47395 -

引脚

+关注

关注

16文章

1190浏览量

50367 -

GND

+关注

关注

2文章

539浏览量

38692 -

逻辑IC

+关注

关注

0文章

21浏览量

6426

原文标题:芝识课堂【CMOS逻辑IC的使用注意事项】—深入电子设计,需要这份指南(一)

文章出处:【微信号:toshiba_semicon,微信公众号:东芝半导体】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何利用CMOS模拟开关实现平衡混频器?有什么注意事项?

胆机使用的注意事项

CMOS集成逻辑门电路的使用注意事项

CMOS逻辑IC的使用注意事项

CMOS逻辑IC的使用注意事项

评论