在FPGA中,动态相位调整(DPA)主要是实现LVDS接口接收时对时钟和数据通道的相位补偿,以达到正确接收的目的。ALTERA的高端FPGA,如STRATIX(r) 系列中自带有DPA电路,但低端的FPGA,如CYCLONE(r)系列中是没有的。下面介绍如何在低端FPGA中实现这个DPA的功能。

实现架构

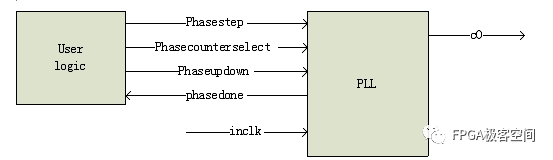

在LVDS输入接收时,时钟和数据的相位可能是不确定的,因此我们需要将时钟的相位作出调整,使得时钟能稳定的采集到输入数据。工作的核心就是用锁相环PLL的相位调整功能,产生若干个时钟的不同相位,看哪些相位能准确的采集到输入数据,然后取窗口中间的一个时钟相位,作为正常工作时的采样时钟。比如通过PLL产生0,45,90,135,……,315度8个相移的时钟,如果0,45,90度相移的时钟能正确采样到输入,那么最后选取中间相位,即45度的时钟作为采样时钟。这样接口上具有最大的时序裕量,从而保证链路的可靠性。下图为这个设计的基本结构,通过PLL调整相位的接口,产生了时钟的不同相位来采集数据,最后选择一个最合适的相位。

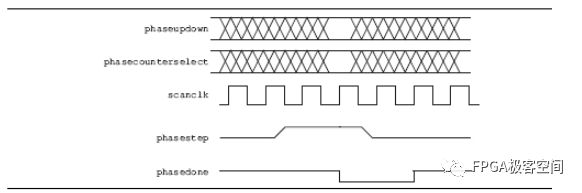

CYCLONE系列的PLL的相位调整接口时序如下图所示:

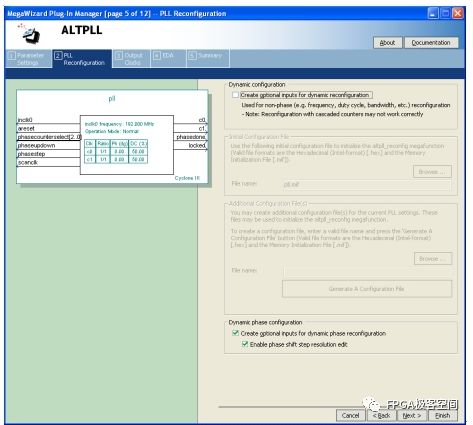

当用户逻辑控制phasestep, phasecounterselect与phaseupdown信号时,PLL的输出时钟C0就改变一次相位。在QII生成PLL时,用户必须选上create optional inputs for dynamic phase reconfigure,否则缺省是不会有这些管脚的,如下图所示。另外必须在output clock tab中写入phase shift step resolution的值,这样才能确定每次相位调整的步长。

-

FPGA

+关注

关注

1629文章

21735浏览量

603196

原文标题:低成本FPGA中实现动态相位调整

文章出处:【微信号:ALIFPGA,微信公众号:FPGA极客空间】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

使用TPS54308设计简单且低成本的Flybuck解决方案

MS3010:单通道低压DC电机驱动与低成本的完美结合

相位超前校正装置适用于什么场合

涂鸦HEDV本地化部署方案,助你低成本实现定制化开发!

低成本FPGA中实现动态相位调整方案

低成本FPGA中实现动态相位调整方案

评论