混合键合在先进封装领域越来越受到关注,因为它提供了功能相似或不同芯片之间最短的垂直连接,以及更好的热学、电气和可靠性结果。

其优势包括互连缩小至亚微米间距、高带宽、增强的功率效率以及相对于焊球连接的更好的缩放性。但是,尽管一些芯片制造商确实在大批量制造 (HVM) 中采用了混合键合,但目前该工艺的成本太高,无法大规模采用。而且由于混合键合将前端和后端生产线连接在一起,因此芯片放置等组装工艺现在必须满足前端规格。

其他挑战包括需要更好的铜凹陷均匀性、更快的芯片到晶圆放置和更佳的对准、多个键合和解键合载体(这会增加成本)以及低温退火能力。最后,必须降低颗粒水平,特别是在芯片放置和切割步骤中。

Brewer Science首席应用工程师 Alice Guerrero 表示:“要成功将混合键合扩展到大批量生产,需要解决与缺陷控制、对准精度、热管理、晶圆翘曲、材料兼容性和工艺吞吐量相关的挑战。”

AI 芯片和模块是混合键合和先进封装的巨大推动力。它们的高性能和高价格有助于推动行业发展。事实上,DRAM 制造商正在评估从焊料凸点键合(通过热压)转向混合键合的净收益(见图 1)。混合键合之后的下一代微缩是顺序 3D 集成,其中键合甚至延伸到薄膜。

混合键合是实现将 SoC 分解为单个威廉希尔官方网站 块(称为小芯片)这一更大目标的关键推动因素。imec 高级研究员、研发副总裁兼 3D 系统集成项目总监 Eric Beyne 表示:“如今,我们对单片 IC 进行了某种分解,其中将拥有用于 SoC、逻辑和 I/O 设备的逻辑和 SRAM 内存等专门威廉希尔官方网站 。我们需要推动一种看似单片或完全集成的解决方案,这样你就看不到不同设备之间的界限。我们必须打破这种障碍,即脱离芯片会在带宽或能耗方面造成损失。”

高带宽内存(HBM) 制造商可以转向混合键合或熔融键合(电介质-电介质),但这样做存在缺点。EV Group (EVG) 业务开发总监 Thomas Uhrmann 表示:“熔融键合目前确实是一种经过验证的 300 毫米晶圆制造工艺,而且这种键合对 HBM 非常有效。HBM 目前堆叠了 12 个芯片,制造商很快就会达到 16 层。但由于每个芯片的性能并不相同,因此基本上最薄弱的环节限制了整个堆栈的性能。这与其说是产量问题,不如说是产量问题,因为 DRAM 晶圆的产量非常好。速度分级实际上是一个很大的障碍。您需要实施预分类才能进行补偿。”

工艺工作原理

晶圆对晶圆键合方案是 CMOS 图像传感器混合键合的首个威廉希尔官方网站 ,其中像素阵列芯片与逻辑芯片键合,以最大化背面照明面积。现在,其他应用也开始流行起来,结合了处理器/缓存、3D NAND、microLED 以及用于 ChatGPT 等 LLM 应用的 AI 模块。

先进封装中的小芯片集成概念提供了全新的灵活性。“在先进封装中,您可以定制系统,” Tignis首席执行官 Jon Herlocker 表示。“您可以说,‘这部分逻辑非常复杂,所以我将在 300 毫米代工厂的先进节点上进行这项工作,但我将从一个或多个更成熟的节点中获取其他功能并将其放在同一个封装上。’您可以有效利用成熟节点及其可预测的高良率工艺,从而降低整体风险。因此,一旦您决定进行先进封装(先进封装存在一定的风险),那么从复杂芯片中提取尽可能多的东西并使用更成熟的威廉希尔官方网站 ,然后通过该先进封装将其连接起来,将带来各种好处。”

电源管理和对电源效率的需求是芯片堆叠和新键合方法的额外驱动因素。混合键合使公司能够创建“阻力最小的路径”,这意味着更短的互连、更大的互连密度以及更大的散热挑战。

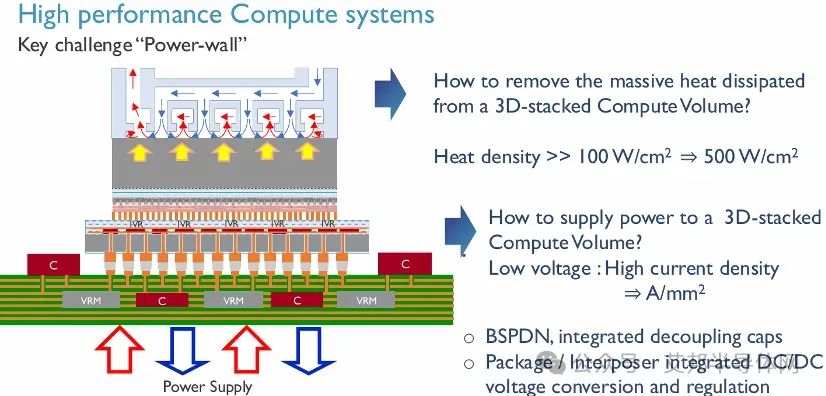

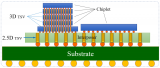

在这一发展过程中,需要降低半导体的功耗。可扩展性变得至关重要(见图 2)。“我们有功率墙,因此目前的能量密度通常为每平方厘米 100 瓦,但未来我们需要以每平方厘米 500 瓦的速度抽离,因此这是一个相当显着的增长,”Beyne 说。“如果你取每平方毫米 500 安培的电流,那么通过微凸块和焊料凸块发送可能不是最好的方法,因为电流高达每平方毫米 500 安培。“这可以通过将电源管理系统集成到设备附近来解决。也许我们不只通过全堆栈发送 1.7V,但也许你会想到更高的电压,例如 48V,然后在封装或电路板级别使用 DC/DC 转换来达到最终电压。”

图 1:细间距混合键合,即使采用背面电源分布,也会导致高热量集中,需要散热器。资料来源:imec

Uhrmann 指出,测试又增加了一层复杂性。“虽然凸块器件可以轻松测试,但混合键合就不那么容易了。您可以为混合键合创建一个双层,因为这样您就有了一个可以测试的底层,但您仍然需要在顶层有键合层。”

工艺工作原理

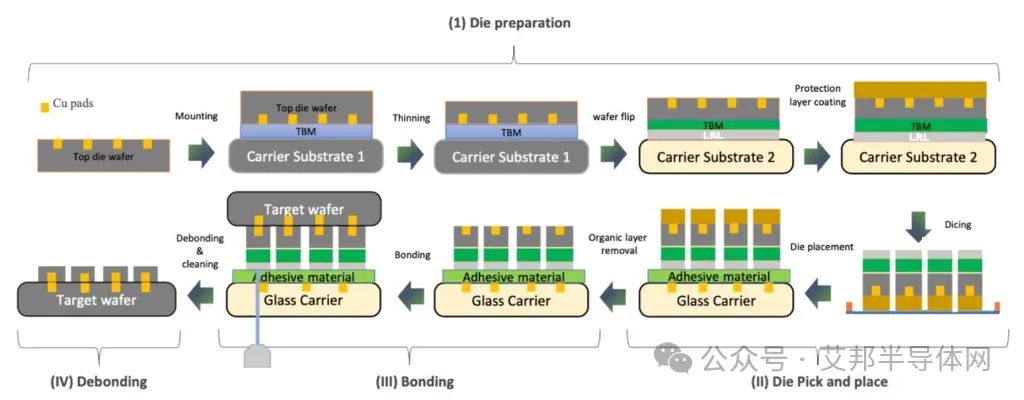

晶圆到晶圆键合工艺比芯片到晶圆方案更成熟,但它有一个主要缺点——芯片必须大小相同。这对于处理器堆栈上的 SRAM 等应用效果很好,但更大的设计和制造灵活性需要芯片到晶圆键合,其中较小的芯片键合到较大的芯片。在这里,集体 D2W 键合的概念变得有吸引力(见图 2)。

图 2:集体芯片到晶圆混合键合流程在激光释放层(绿色)上添加了一个声学层(灰色),使转移良率达到 100%。来源:imec

如图所示,该工艺使用多种载体,包括硅和玻璃。混合键合工艺流程采用经过最终金属化层处理的晶圆,然后执行类似于片上镶嵌工艺的步骤。

电介质蚀刻在 SiCN 电介质中最佳地形成方形腔,然后通过电化学沉积 (ECD) 用阻挡金属、铜种子和铜填充。随后的 CMP 工艺经过优化,可实现极高的晶圆间均匀性,以产生尽可能光滑的电介质表面,同时在铜垫区域形成小凹陷。

第二步是将晶圆安装到载体上,然后研磨/减薄硅晶圆。将晶圆翻转并粘合到第二个载体上,然后旋涂一层光刻胶层,以在胶带框架上切割时保护表面。第三个载体粘合到该芯片区域,然后剥离光刻胶。将其放置在新的载体上,准备与目标晶圆粘合,然后通过刀片、红外激光或紫外线进行脱粘。

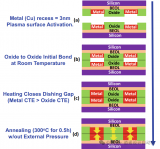

接下来,真空室中的电介质活化步骤使用等离子体来优化具有悬空 Si-O 键的键合表面。随后使用 DI 水冲洗以使电介质水合。第二片晶圆以与晶圆 1 相同的方式通过铜 CMP 进行处理,然后与晶圆 1 对齐并键合。然后,这对晶圆在 350°C 的炉内退火两小时。

现在,键合对可以变薄以用于下一个晶圆。Imec 和其他公司已经证明,非常薄(50 µm)到非常厚(775 µm)的芯片可以从临时载体转移到目标晶圆,转移率和键合率均为 100%。对于超薄芯片,硅载体是首选。玻璃载体确实允许紫外线脱键,但它们与前端工具不兼容。

Imec、Brewer Science 和 Suss MicroTec 最近展示了集体芯片到晶圆键合流程可以扩展到三到四个晶圆。在有机激光释放层中添加了一层所谓的声学层,以吸收由烧蚀(脱键)工艺引起的冲击波,这种冲击波可能会损坏芯片边缘。值得注意的是,通过红外显微镜测量的对准是倒装芯片工具和键合工具对准相结合的功能。

转移良率和粘合良率是关键指标,在完全优化的制造和装配工艺下,这些指标可达到 100%。将集体芯片到晶圆流程扩展到两个、三个和四个晶圆会使工艺变得复杂,因为在加工过程中会出现翘曲、粘合剂去除不完全以及芯片损坏等问题。[3]

载体基板的选择取决于临时粘合材料 (TBM) 及其脱粘能力。“粘合剂将芯片临时粘合到 TBM 的能力取决于其机械、热和化学特性以及芯片表面状况,”Brewer Science 的 Guerrero 说道。“通常,粘合头温度和载体(卡盘)温度之间的相互作用将根据 TBM 的热特性进行调整,以实现最佳芯片粘合效果。激光脱粘最适合在芯片释放过程中将力降至最低。”

Guerrro 指出,薄芯片存在损坏芯片的风险,但这些风险可以通过材料和工艺设计来减轻。“机械脱键是一种更具成本效益的解决方案,因为与激光相比,设备成本更低,但其应用范围并不广泛,”她说。“紫外线脱键并不普及,而且在载体层面实施起来具有挑战性。紫外线脱键胶带很容易买到,是最经济的脱键方法,但在处理小于 50 µm 的芯片时会受到限制。

工具清洁度对于防止键合界面出现空隙至关重要,空隙在 C-SAM 图上显示为白点。“有趣的是,由于清洁方式和工艺,一些颗粒仍会在表面上移动。所以这并不意味着你不能有一个颗粒,”Adeia 工程高级副总裁 Laura Mirkarimi 说。“这是一个可以处理一些颗粒的工艺,但不移动的大颗粒会阻止它键合。键合前沿在晶圆键合中移动得非常快,甚至在芯片到晶圆键合中也是如此,所以它实际上是一种自发键合,需要通过仔细处理表面来管理。”

这解释了为什么必须在整个混合键合流程中优化多个清洁步骤。

最近还有其他工艺改进:

SiCN 沉积中的碳/氮含量经过优化,具有高键合强度和低粗糙度。对于 HBM,这种典型的 350°C 工艺可以降低到 200°C 范围 [3]

应用材料公司开发了一种 300°C、5 分钟的退火工艺,可将产量提高两个数量级,同时满足 500 纳米间距的低电阻 250 纳米铜 CD 的要求。[1]

铜 CMP 应留下平坦的晶圆表面(总厚度变化或 TTV),并且根据间距,1nm 铜凹槽变化

EV Group 推出的新型无机粘合剂粘合和激光脱模工艺可使用硅载体晶圆,该晶圆可提供 100nm 的 TTV、更好的几何稳定性和更高的热导率

硅载体上的后一种工艺还允许硅载体重复使用,从而减少工艺步骤并降低拥有成本。EVG 的 Urhmann 表示:“我们使用了一种完全不同的释放层,一种与前端兼容的无机层。但硅载体可以到处使用。所以现在你可以拥有与熔合键合配合使用的载体,你还可以携带混合键合晶圆或非常薄的器件、外延层。因此,它将整个产品组合扩展到前端传输,但并不局限于此。高精度意味着远小于 100nm。”

这种发展也会影响可持续性。“水循环和保持水清洁的成本很高,”他说。“研磨和抛光会产生大量颗粒——甚至是纳米颗粒——因此过滤成本很高。”

“虽然人们经常谈论面对面键合,但许多工艺都需要面对面键合,这意味着你首先需要将其放在载体上并将其变薄,然后将其转移到另一个载体上,”他说。“因此,你拥有薄的设备晶圆,然后如果需要减薄另一个载体晶圆,你就得牺牲两片晶圆,这是不划算的。”

直到最近,具有 HVM 能力的倒装芯片键合机的对准公差为 ±3µm (3 sigma),但已降至 1µm (3 sigma)。“对准精度的经验法则是键合机必须是焊盘直径的 0.1 至 0.25 倍,或 1µm 焊盘的 100 至 250nm,”Adeia 的 Mirkarimi 说道。最近,多家供应商已经开发并提供了具有亚微米精度的键合机,包括 BESI (BE Semiconductor) 和 Suss MicroTec。“尽管 D2W HB 具有诸多优势,但它也面临两大组装挑战,”英特尔的 Feras Eid 及其同事表示。[2] “首先是对准,目前甚至下一代键合设备都无法满足 1µm 以下间距的贴装要求。其次是吞吐量,即使在当今相对宽松的间距(例如 9µm)下,D2W HB 贴装步骤也是整个 HB 流程中最慢且成本最高的步骤。”

因此,英特尔和其他公司正在探索拾取和放置的替代方案,例如流体自对准,它使用两个芯片上的微小水珠和引导图案来自对准结构。[2] 该工艺由 CEA-Leti 和英特尔联合开发。重要的是,芯片到晶圆在 x、z 和 theta(旋转)方向上可能会错位。液体限制在特定条件下将芯片到晶圆的错位降低到 200nm。虽然该工艺还不适合生产,但它有可能取代耗时的芯片放置,预计吞吐量将提高 10 倍。

尽管半导体行业已证明混合键合适用于各种应用,但业界仍在不断努力减少晶圆步骤数量和成本。虽然制造 AI 芯片的公司可以负担得起更复杂的工艺,但为了让该威廉希尔官方网站 渗透到更便宜的系统中,它必须更简单。

直接芯片到晶圆键合工艺比集体芯片到晶圆方法简单得多,集体芯片到晶圆方法只将已知良好的芯片放置在重建的晶圆上,然后将其键合到另一晶圆上。然而,直接键合容易受到污染,因为芯片放置工具直接接触敏感的键合表面,需要非常高的工具清洁度,甚至可能需要现场芯片清洁能力。

-

晶圆

+关注

关注

52文章

4894浏览量

127936 -

先进封装

+关注

关注

2文章

400浏览量

241

原文标题:混合键合在可制造性方面取得进展

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

先进封装威廉希尔官方网站 -7扇出型板级封装(FOPLP)

先进封装威廉希尔官方网站 - 6扇出型晶圆级封装(FOWLP)

Cu-Cu Hybrid Bonding威廉希尔官方网站 在先进3D集成中的应用

从发展历史、研究进展和前景预测三个方面对混合键合(HB)威廉希尔官方网站 进行分析

先进封装威廉希尔官方网站 激战正酣:混合键合成新星,重塑芯片领域格局

混合键合,成为“芯”宠

晶圆微凸点威廉希尔官方网站 在先进封装中的应用

混合键合威廉希尔官方网站 :开启3D芯片封装新篇章

大算力浪潮下,国产先进封装威廉希尔官方网站 取得了怎样的成绩?面临怎样的挑战?

混合键合在先进封装领域取得进展

混合键合在先进封装领域取得进展

评论