一、氮化硅薄膜制备方法及用途

氮化硅(Si3N4)薄膜是一种应用广泛的介质材料。作为非晶态绝缘体,氮化硅薄膜的介电特性优于二氧化硅,具有对可移动离子较强的阻挡能力、结构致密、针孔密度小、化学稳定性好、介电常数高等优点,在集成电路制造领域被广泛用作表面钝化层、绝缘层、扩散阻挡层、刻蚀掩蔽膜等。

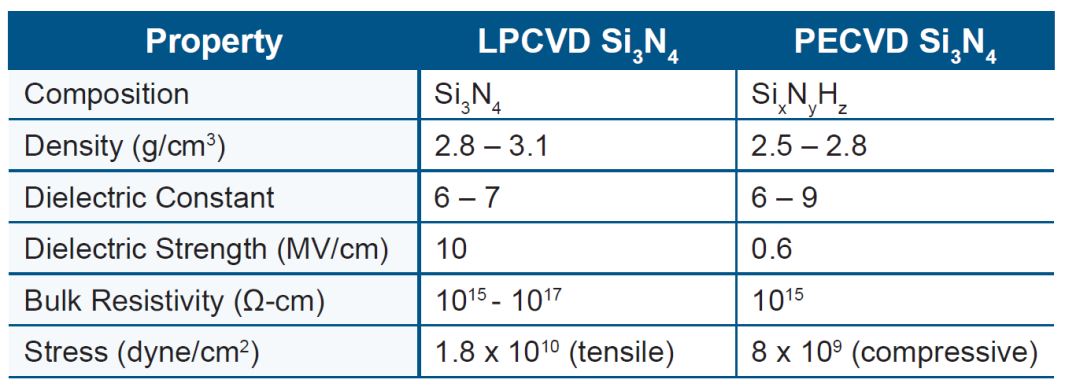

LPCVD和PECVD制备氮化硅薄膜特性对比(下表)

低压化学气相沉积(LPCVD)氮化硅工艺需要高温,通常在700~800°C,而等离子体增强化学气相沉积(PECVD)氮化硅可以在低于 400°C 的温度下沉积。相较于PECVD氮化硅薄膜,LPCVD氮化硅具备更加致密的薄膜特性,更耐腐蚀,薄膜硬度更好,掩膜性更好,更加广泛的应用于碱性溶液刻蚀硅材料的掩膜层。不过这两个过程通常存在工艺温度和薄膜质量之间的利弊权衡,LPCVD 工艺沉积高质量的氮化硅薄膜,而PECVD工艺沉积包含不同浓度硅氢键的氮化硅薄膜。

氮化硅薄膜是无定形的硬质材料,在半导体器件制造中有两个主要用途:掩蔽膜和钝化层。掩蔽膜通常使用 LPCVD 沉积,因为这会产生最不透水的薄膜。氮化硅掩蔽特别适用于热氧化过程,因为氧气很难经由氮化硅扩散。

氮化硅作为钝化层也具有许多理想的品质。PECVD 方法允许其在与底层器件结构兼容的工作温度下沉积。该薄膜几乎不受水分和钠离子等关键环境污染物的影响。最后,通过调整 PECVD 工艺条件,还可以调整薄膜中的固有应力,以消除薄膜分层或开裂的任何风险。

二、低应力 PECVD氮化硅薄膜制备

对于很多常用材料,如氮化硅、多晶硅等,本征应力是不可避免的。不过在半导体工艺中往往需要较低的薄膜应力,以保证较小的器件形变。通常的方法是采用多层薄膜结构,并通过选择材料、控制厚度和应力方向(一层由于压应力而产生了形变的薄膜,理论上增加一层张应力的材料,可以使总的变形降低为零)来进行补偿以消除应力带来的结构变形。

在PECVD制备氮化硅薄膜工艺中,薄膜应力主要来源于两个方面。一是由于薄膜和衬底之间不同的热膨胀系数所导致的热应力,这种应力是由于在高温条件下淀积的薄膜当降低到室温时相对于衬底会产生一定的收缩或膨胀,表现出张应力或压应力。

另外,淀积薄膜的微结构也是产生应力的重要原因,这种应力的产生主要是由于薄膜和衬底接触层的错位,或者是因为薄膜内部的一些晶格失配等缺陷和薄膜固有的分子排列结构造成的。

在PECVD系统中,由于淀积温度较低(通常不超过400℃),并且引用射频放电产生等离子体来维持反应,因此射频条件(频率和功率)成为影响氮化硅薄膜应力的关键因素之一。

PECVD淀积的氮化硅薄膜化学比分波动较大,其硅-氮比随反应气体比例的变化而变化,同时淀积的氮化硅薄膜中通常还含有一定量的氢元素,氢的存在会使薄膜的结构性能产生退化,但也会降低薄膜的应力。

在低频(380kHz)条件下,反应气体的离化率较高,等离子体密度较大,在淀积反应过程中比较容易减少氢元素的掺入,使薄膜变得致密,因此会产生较大的压应力,较高等离子体密度也会产生较快的淀积速率。

在高频(13.56MHz)条件下,反应气体的离化程度远低于低频时,因此等离子体密度较低,在淀积反应中引入较多的氢元素,这种含氢较高且比较疏松的结构所带来的就是薄膜的张应力。

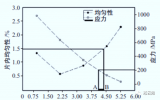

混频氮化硅薄膜的性质介于二者之间,可以视为低频氮化硅和高频氮化硅二者的叠加。因此可以使用混频工艺减小氮化硅薄膜的应力,并对混频工艺的参数进行控制来实现对薄膜应力大小甚至方向的控制。

不过对于混频工艺中低频和高频反应时间周期需要适当选取。当切换时间周期过短,反应腔中将频繁的进行高低频的交换,由于高频和低频条件下的等离子体性质有较明显的差异,因此这种频繁的切换会使等离子体变得不稳定,从而影响薄膜的均匀性。当切换时间周期过长,由于高频和低频氮化硅本身又在致密度、折射率等参数上有所不同,过长时间的单一频率淀积会影响氮化硅薄膜厚度方向上的均匀性。因此在进行工艺调整时对于以上两方面因素要折中考虑。

射频功率是 PECVD 工艺中最重要的参数之一。当射频功率较小时,反应气体尚不能充分电离,激活效率低,反应物浓度小,薄膜针孔多且均匀性较差;当射频功率增大时,气体激活效率提高,反应物浓度增大,并且等离子体气体对衬底有一定的轰击作用使生长的氮化硅薄膜结构致密,提高了膜的抗腐蚀性能。但射频功率不能过大,否则沉积速率过快,会出现类似“溅射”现象影响薄膜性质。低频条件下氮化硅薄膜应力为压应力,高频条件下为张应力,其大小均随功率的增大而减小。

-

薄膜

+关注

关注

0文章

292浏览量

29178 -

氮化硅

+关注

关注

0文章

73浏览量

287

原文标题:【推荐】氮化硅薄膜特性简介

文章出处:【微信号:芯长征科技,微信公众号:芯长征科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

氮化硅薄膜的特性及制备方法

透射电镜(TEM)样品制备方法

浅谈薄膜沉积

碳化硅 (SiC) 与氮化镓 (GaN)应用 | 氮化硼高导热绝缘片

碳化硅与氮化镓哪种材料更好

ATA-7010高压放大器在纳米薄膜制备中的作用有哪些

LPCVD威廉希尔官方网站 助力低应力氮化硅膜制备

氮化镓是什么结构的材料

氮化镓芯片生产工艺有哪些

氮化镓是什么威廉希尔官方网站 组成的

氮化镓功率器件结构和原理

氮化镓半导体和碳化硅半导体的区别

TOPCon核心工艺威廉希尔官方网站 路线盘点

氮化硅薄膜制备方法及用途

氮化硅薄膜制备方法及用途

评论