随着市场对嵌入式设备的功能需求越来越高,集成了嵌入式处理器和实时处理器的主控方案日益增多,以便更好地平衡性能与效率——实时核负责高实时性任务,A核处理复杂任务,两核间需实时交换数据。然而在数据传输方面,传统串行接口尽管成本较低,但其传输速率相对较慢;反之,并行接口虽然传输速度快,但成本却比较高。因此,单芯片多核异构处理器就成为能够满足需求的理想选择。

RISC-V作为一种开源指令集架构,以其简洁性、一致性、可扩展性以及高编译效率,为实时性处理场景提供了强大的支持。将A核与RISC-V核结合作为单芯多核异构方案,可以有效利用RISC-V的这些优势,实现高性能与高实时性的有效结合。

本文将以OK113i-S开发板为例,为大家介绍RISC-V核的资源和应用案例。

1、OK113i-S开发板的RISC-V核

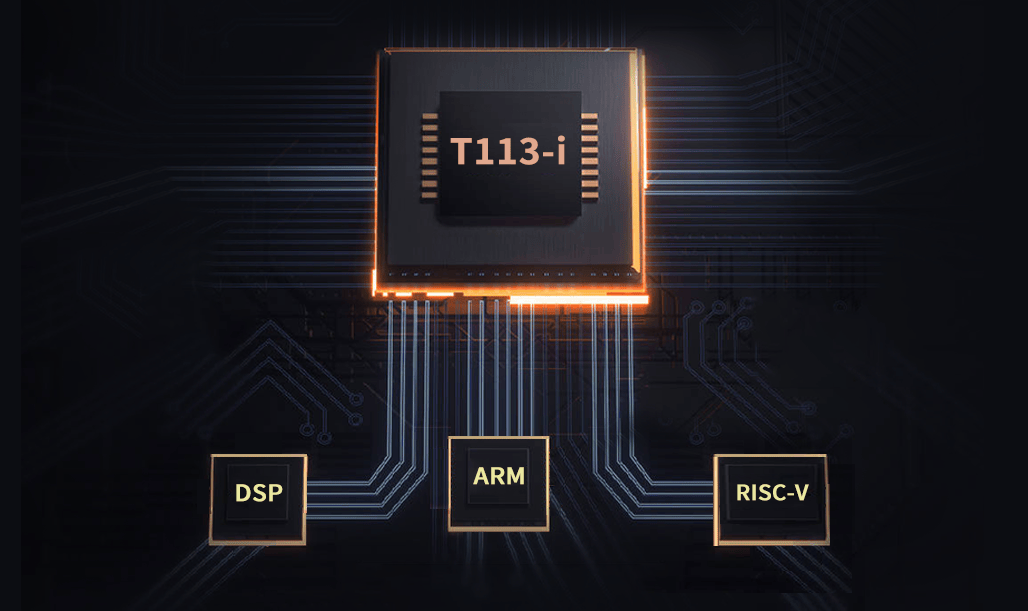

飞凌嵌入式OK113i-S开发板是一款基于全志T113-i工业级处理器开发的高性价比开发板,集成了双核Cortex-A7 CPU、64位玄铁C906 RISC-V和DSP,能够提供高效的计算能力和性价比。尤为值得一提的是,其内置的RISC-V核心作为一款超高能效的实时处理器,主频峰值可达1008MHz,并标准配备了内存管理单元,能够流畅运行RTOS系统或裸机程序,进一步提升了应用灵活性。

1.1 RISC-V核的特性

(1) 最高主频可达1008MHz;

(2) 32KB指令缓存;

(3) 32KB数据缓存;

(4) 可运行于超大容量的DDR

... ...

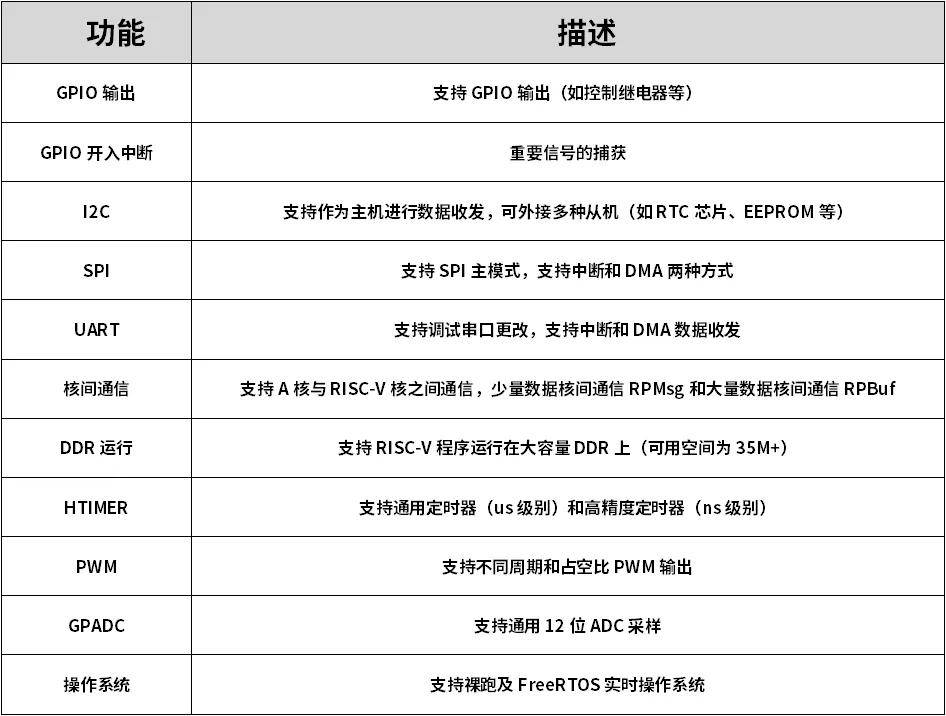

1.2 RISC-V核的接口资源

2、应用实例

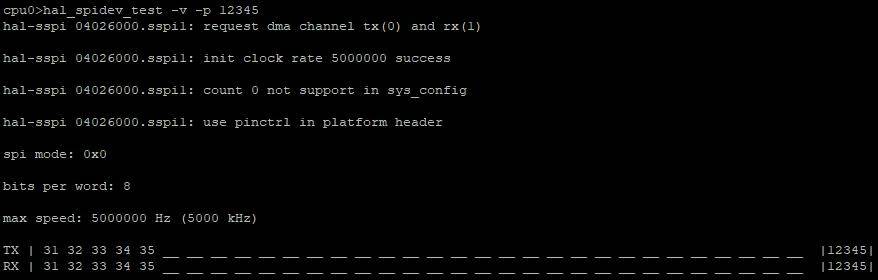

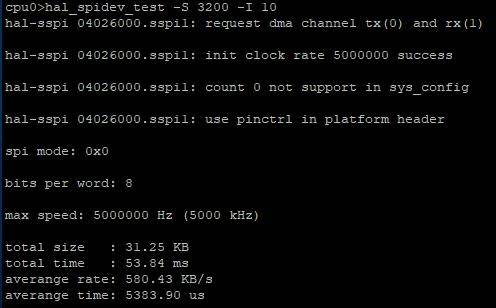

2.1 SPI数据收发

本案例为SPI回环测试,即将SPI的MOSI和MISO两个引脚短接进行数据收发。

(1) 功能介绍

(2) 效果实现

SPI发送和接收的FIFO均为64个,在底层hal库程序中,当数据长度小于64字节时,采用中断方式,当FIFO大于等于64字节时,采用DMA模式。

中断方式传输效果:

DMA方式传输效果:

在DMA传输方式下,SPI速率默认为5Mbit/s,案例中平均传输速率为580.43KB/s,即4.6Mbit/s,接近理论值。

2.2 核间通信RPbuf

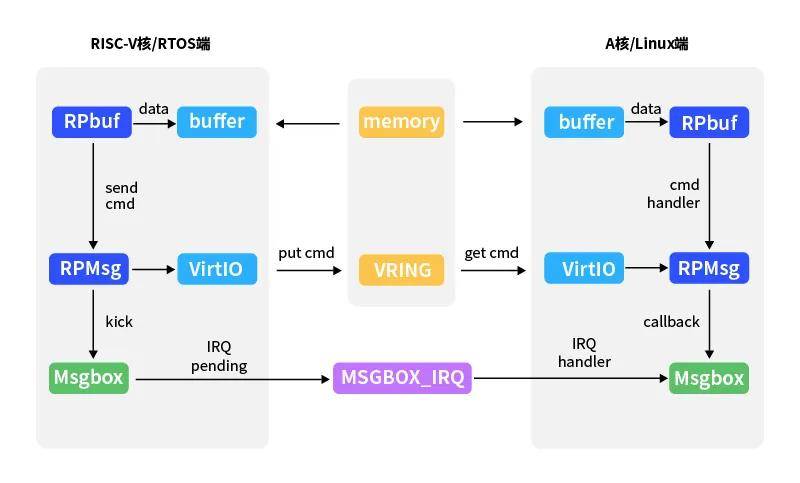

RPbuf是全志基于RPMsg所实现一套高带宽数据传输的框架。RPMsg是基于共享内存和Msgbox中断实现的一套核间通信机制,RPMsg除去头部的16字节数据外,单次最多可发送496字节有效数据。因此,全志基于RPMsg实现了一套大数据量传输机制RPbuf,实现原理是在DDR中放置传输的数据,通过RPMsg传输DDR的地址和大小。我们以单次32KB数据传输为例进行展示。

(1) 功能介绍

• VirtIO:一套虚拟化数据传输框架,用于管理共享内存VRING;

• VRING:由VirtIO管理的一个环形共享内存;

• Msgbox:全志提供的一套消息中断机制,已与linux内核中原生的mailbox框架适配;

• MSGBOX_IRQ:Msgbox中断;

• RPMsg:基于VirtIO管理的共享内存所实现一套少量数据传输的框架;

• RPbuf:全志基于RPMsg所实现一套大量数据传输的框架。

由上图可知(以RISC-V核向A核发送数据为例),RPbuf首先将数据放置在DDR中,再将缓冲区首地址和大小通过RPMsg发送至A核(RPMsg将缓冲区首地址和大小放入VRING,然后请求Msgbox中断,A核收到这个中断后,在回调函数中使用RPMsg接口函数来从VRING中取出cmd)。

随后A核从cmd handler中获取缓冲区内的地址和长度,最后在应用层读取数据,从而完成双核间的数据传输。

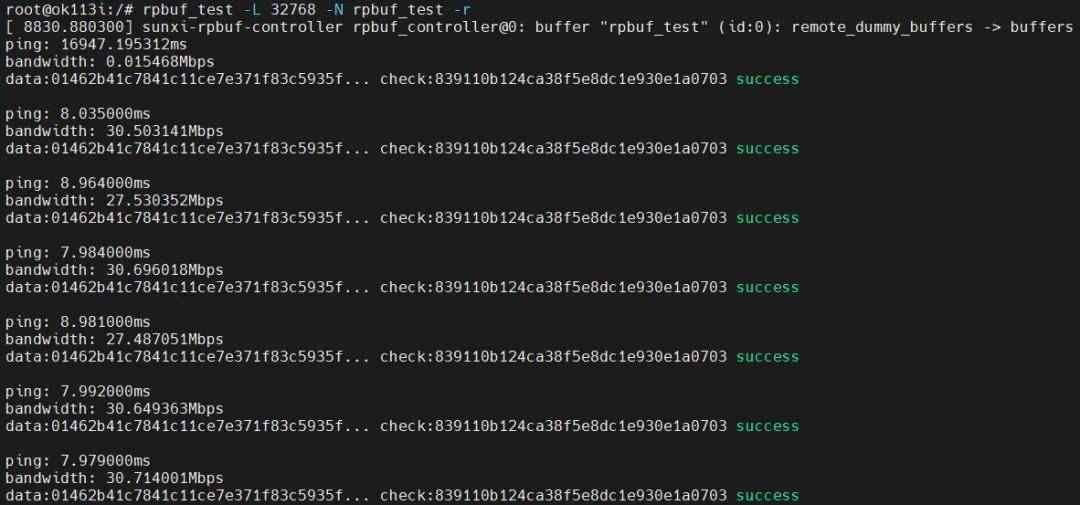

(2) 效果展示

由上图测试效果可以看到,带宽大约为27~30Mbps。

以上就是飞凌嵌入式OK113i-S开发板RISC-V核部分外设的使用方法,是不是感觉和单片机的开发一样简单方便呢?

-

嵌入式

+关注

关注

5082文章

19104浏览量

304829 -

开发板

+关注

关注

25文章

5032浏览量

97375 -

多核异构

+关注

关注

0文章

18浏览量

5439 -

RISC-V

+关注

关注

45文章

2270浏览量

46131 -

全志T113

+关注

关注

0文章

52浏览量

248

发布评论请先 登录

相关推荐

国产RISC-V案例分享,基于全志T113-i异构多核平台!

基于全志T113-i多核异构处理器的全国产嵌入式核心板简介

国产RISC-V基于全志T113-i异构多核平台

哇!0.8秒启动!Linux快速启动方案分享,全志T113-i国产平台!

G2D图像处理硬件调用和测试-基于米尔-全志T113-i开发板

飞凌嵌入式T113-i开发板RISC-V核的实时应用方案

飞凌嵌入式T113-i开发板RISC-V核的实时应用方案

评论