“持续更新 8 年,Github 超过 1k star 的项目。一种使用文本替代原理图的语言。”

追踪 skidl 项目很久了,之所以之前没有分享是因为老版本只能支持 KiCad 5.0 符号库的解析,而且生成的网表也仅能支持 KiCad 6,所以用起来比较麻烦。最近作者又更新了一个大版本,全面支持 KiCad 7 和 KiCad 8,虽然仍有一些问题,但跑起来比之前方便了很多。AI 时代的到来,让自动化设计又多了一个研究的方向。由于 skidl 的设计初衷就是用文本描述原理图,这对于机器学习来说无疑是非常合适的!感兴趣的小伙伴赶紧学习起来吧,有兴趣进一步讨论的也可以私信我或留言。SKiDL 简介

通过 SKiDL Python 软件包,您可以用文本描述电子元件之间的连接。生成的 Python 程序可对常见错误进行电气规则检查,并输出网表,作为 PCB Layout 工具的输入。-

项目主页:https://github.com/devbisme/skidl

-

License: MIT

-

文档:http://devbisme.github.io/skidl

-

用户论坛:https://github.com/devbisme/skidl/discussions

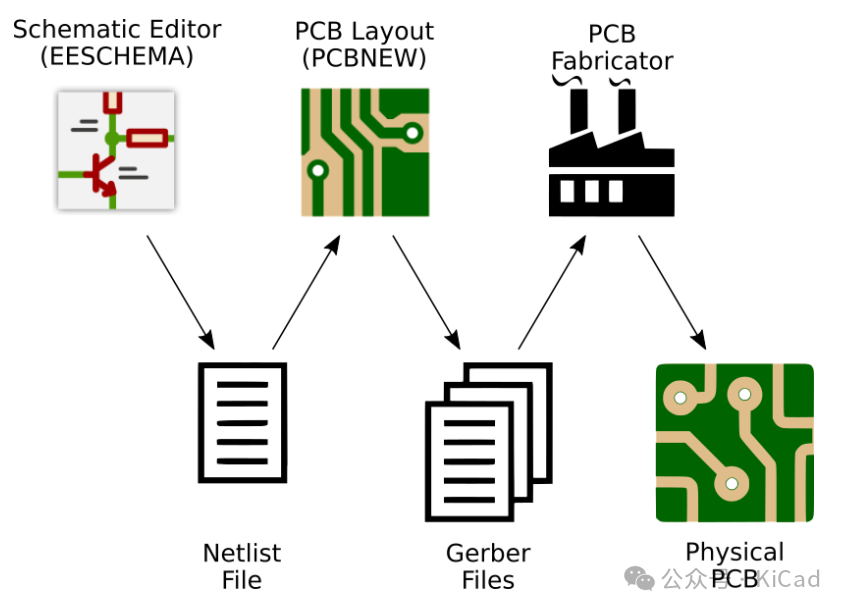

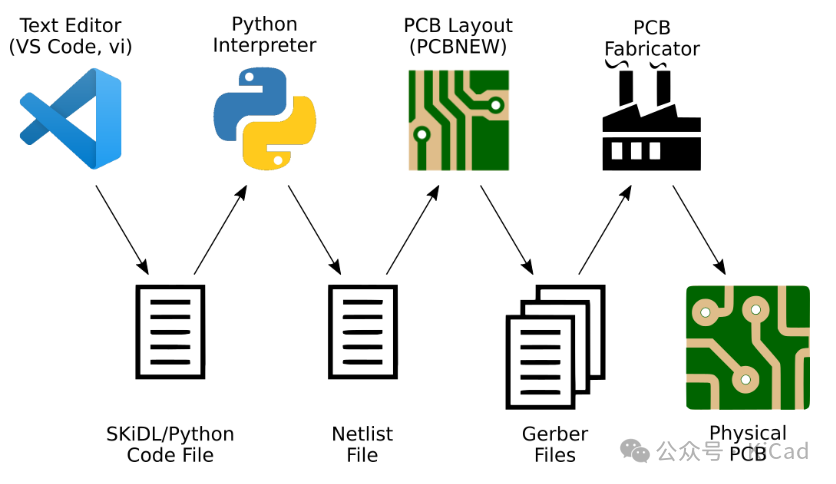

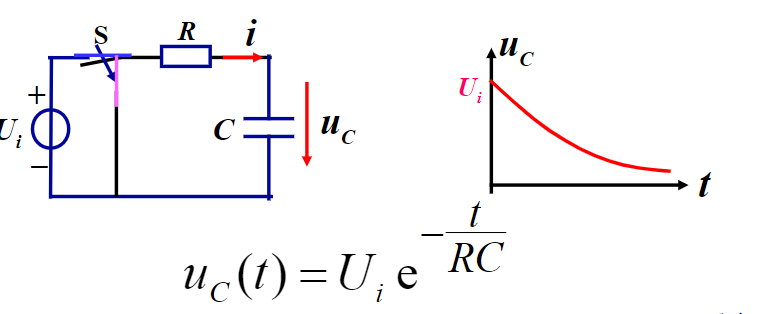

skidl 希望做到的,提供一个选项,既可以通过传统方式设计原理图(下图一),也可以用代码的方式实现(下图二):

功能

-

语法强大、灵活(因为它是 Python)。

-

允许对电子电路进行简洁描述(想象一下不需要在多页原理图中追踪信号)。

-

允许对电子电路进行文本描述(想想在电路中使用 diff和 git)。

-

针对常见错误(如未连接器件的 I/O 引脚)执行电气规则检查 (ERC)。

-

支持电子设计的平铺/分层/混合描述。

-

支持设计复用(想象一下使用 PyPi 和 Github 发布电子设计)。

-

可与任何 ECAD 工具配合使用(只需两种方法:一种用于读取元件库,另一种用于输出正确的网表格式)。

-

充分利用 Python 生态系统的所有优势(因为它是 Python)。

举例

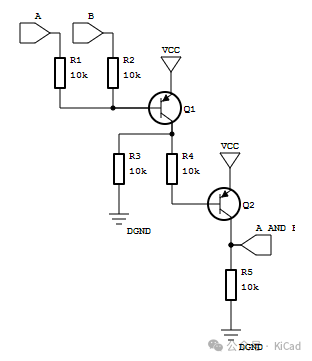

下面的 SKiDL 程序描述了一个由分立晶体管构建的双输入 AND 门,作为一个非常简单的例子:

以下是输出的网表,可以直接在 KiCad 中导入:from skidl import *# Create part templates.q = Part("Device", "Q_PNP_CBE", dest=TEMPLATE)r = Part("Device", "R", dest=TEMPLATE)# Create nets.gnd, vcc = Net("GND"), Net("VCC")a, b, a_and_b = Net("A"), Net("B"), Net("A_AND_B")# Instantiate parts.gndt = Part("power", "GND") # Ground terminal.vcct = Part("power", "VCC") # Power terminal.q1, q2 = q(2) # Two transistors.r1, r2, r3, r4, r5 = r(5, value="10K") # Five 10K resistors.# Make connections between parts.a & r1 & q1["B C"] & r4 & q2["B C"] & a_and_b & r5 & gndb & r2 & q1["B"]q1["C"] & r3 & gndvcc += q1["E"], q2["E"], vcctgnd += gndtgenerate_netlist(tool=KICAD8) # Create KICAD version 8 netlist.

(export (version D)(design(source "/home/devb/projects/KiCad/tools/skidl/tests/examples/svg/simple_and_gate.py")(date "07/19/2024 05:54 AM")(tool "SKiDL (1.2.2)"))(components(comp (ref(value GND)(footprint )(fields(field (name F0)(field (name F1) GND))(libsource (lib power) (part GND))(sheetpath (names /top/18388231966295430075) (tstamps /top/18388231966295430075)))(comp (ref(value VCC)(footprint )(fields(field (name F0)(field (name F1) VCC))(libsource (lib power) (part VCC))(sheetpath (names /top/12673122245445984714) (tstamps /top/12673122245445984714)))(comp (ref Q1)(value Q_PNP_CBE)(footprint )(fields(field (name F0) Q)(field (name F1) Q_PNP_CBE))(libsource (lib Device) (part Q_PNP_CBE))(sheetpath (names /top/5884947020177711792) (tstamps /top/5884947020177711792)))(comp (ref Q2)(value Q_PNP_CBE)(footprint )(fields(field (name F0) Q)(field (name F1) Q_PNP_CBE))(libsource (lib Device) (part Q_PNP_CBE))(sheetpath (names /top/12871193304116279102) (tstamps /top/12871193304116279102)))(comp (ref R1)(value 10K)(footprint )(fields(field (name F0) R)(field (name F1) R))(libsource (lib Device) (part R))(sheetpath (names /top/17200003438453088695) (tstamps /top/17200003438453088695)))(comp (ref R2)(value 10K)(footprint )(fields(field (name F0) R)(field (name F1) R))(libsource (lib Device) (part R))(sheetpath (names /top/12314015795656540138) (tstamps /top/12314015795656540138)))(comp (ref R3)(value 10K)(footprint )(fields(field (name F0) R)(field (name F1) R))(libsource (lib Device) (part R))(sheetpath (names /top/11448722674936198910) (tstamps /top/11448722674936198910)))(comp (ref R4)(value 10K)(footprint )(fields(field (name F0) R)(field (name F1) R))(libsource (lib Device) (part R))(sheetpath (names /top/2224275500810828611) (tstamps /top/2224275500810828611)))(comp (ref R5)(value 10K)(footprint )(fields(field (name F0) R)(field (name F1) R))(libsource (lib Device) (part R))(sheetpath (names /top/3631169005149914336) (tstamps /top/3631169005149914336))))(nets(net (code 1) (name A)(node (ref R1) (pin 1)))(net (code 2) (name A_AND_B)(node (ref Q2) (pin 1))(node (ref R5) (pin 1)))(net (code 3) (name B)(node (ref R2) (pin 1)))(net (code 4) (name GND)(node (ref(node (ref R3) (pin 2))(node (ref R5) (pin 2)))(net (code 5) (name N$1)(node (ref Q1) (pin 2))(node (ref R1) (pin 2))(node (ref R2) (pin 2)))(net (code 6) (name N$2)(node (ref Q1) (pin 1))(node (ref R3) (pin 1))(node (ref R4) (pin 1)))(net (code 7) (name N$3)(node (ref Q2) (pin 2))(node (ref R4) (pin 2)))(net (code 8) (name VCC)(node (ref(node (ref Q1) (pin 3))(node (ref Q2) (pin 3)))))

注意事项

skidl 在 Windows 上运行的时候经常会碰到问题。最常见的问题是没有正确设置符号库的环境变量,导致无法找到符号库,解析错误。这个错误可以在代码中加入以下语句解决:

os.environ["KICAD8_SYMBOL_DIR"] = "C:\symbols"

“=” 号后面的路径为实际的符号路径。

如果您使用的不是 KiCad 8,而是其他版本的 KiCad,那么最好设置一下默认工具:

set_default_tool(KICAD8)

同样的,输出网表的时候也要指定网表的版本(K8/K7/K6 网表格式有变动):

generate_netlist(tool=KICAD8)

此外, 目前版本的 skidl 还可以直接生成原理图和 PCB,但功能尚不完备,环境配置比较复杂,建议编程基础较好的小伙伴尝试。结束语

skidl 的具体使用方式,这里就不再赘述了,有兴趣的小伙伴可以自行阅读 skidl 的文档,遇到问题也可以搜索仓库中的 issue 和 forum,作者 Dave 也非常乐意与大家互动,解答大家的问题。 最后总结一下 skidl 做了什么:用 python 代码实现图形界面的原理图设计。具体的实现方式为:- 通过环境变量找到需要使用的原理图符号,parse出符号的引脚编号(名称)

- 在文本编辑器(或IDE)中使用编程语言连接这些管脚

- 生成 KiCad 格式的网表

-

电路原理图

+关注

关注

40文章

347浏览量

38318 -

python

+关注

关注

56文章

4792浏览量

84628 -

KiCAD

+关注

关注

4文章

149浏览量

8747

发布评论请先 登录

相关推荐

如何读懂电路原理图

开源工具SkiDL - 用Python来描述电路

SkiDL:使用 Python 设计电路原理图

SkiDL:使用 Python 设计电路原理图

评论