希姆计算的RISC-V矩阵扩展开源项目已升级至0.5版本

-----支持向量+矩阵的实现

范福杰博士&陈炜博士

项目背景

Background

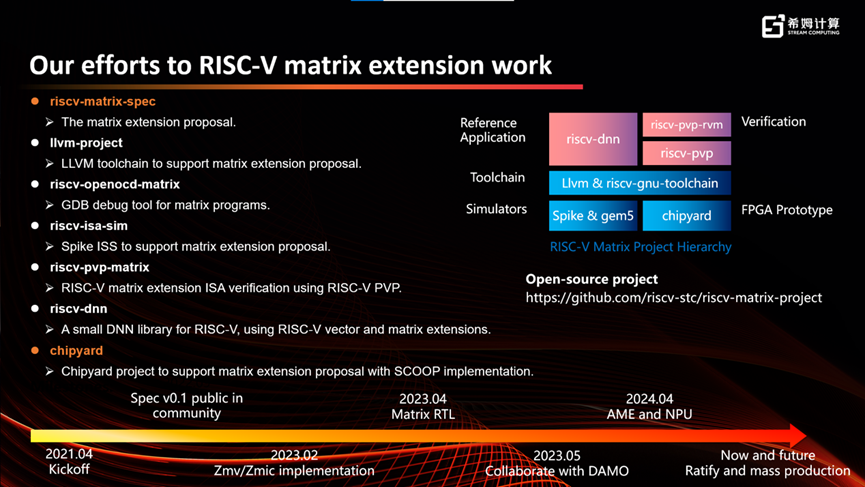

为了解决RISC-V在人工智能领域中指令碎片化的问题,推动加速人工智能行业的发展,自2021年开始,希姆计算启动了针对RISC-V矩阵指令集和支持工具的开源工作,工作的目标是提高人工智能应用的兼容性、降低软件开发成本,并实现新一代的标准和可扩展的领域特定架构。

2022年9月,完成了RISC-V矩阵ISA规范0.1版本,并向RISC-V国际基金会提交了开源提案和支持工具。

2023年5月,与达摩院建立了协商机制,共同探索RISC-V矩阵指令集。

2024年8月,完成了RISC-V矩阵ISA规范0.5版本。

2024年10月,完成了RISC-V矩阵ISA规范0.5版本支持工具链的开发。

今天,希姆计算正式发布了RISC-V矩阵指令集0.5版本及其支持工具,成为首家向全球社区提交完整RISC-V矩阵指令集及其支持工具的公司。这将推动RISC-V矩阵指令集国际标准的快速形成,并推动整个RISC-V生态系统的发展。

项目亮点

Highlights

最新的RISC-V矩阵指令集采用Tile-based的矩阵乘法架构设计,在原有基础上进一步完善了编程模型和类型支持。

同时提供了基本版32位指令编码(https://github.com/riscv-stc/riscv-matrix-spec) 和扩展版64位长指令编码(https://github.com/riscv-stc/riscv-matrix-spec/tree/matrix64) 。

通过参数化寄存器架构和模块化类型系统,它能够适应从边缘到云端的各种应用场景。

为了推动标准化和商业实施,提供了以下工具并进行了更新:

基于LLVM的编译器 (https://github.com/riscv-stc/llvm-project/tree/matrix)

基于Spike的interwetten与威廉的赔率体系 器 (https://github.com/riscv-stc/riscv-isa-sim)

基于GDB的调试器 (https://github.com/riscv-stc/riscv-openocd-matrix/tree/matrix)

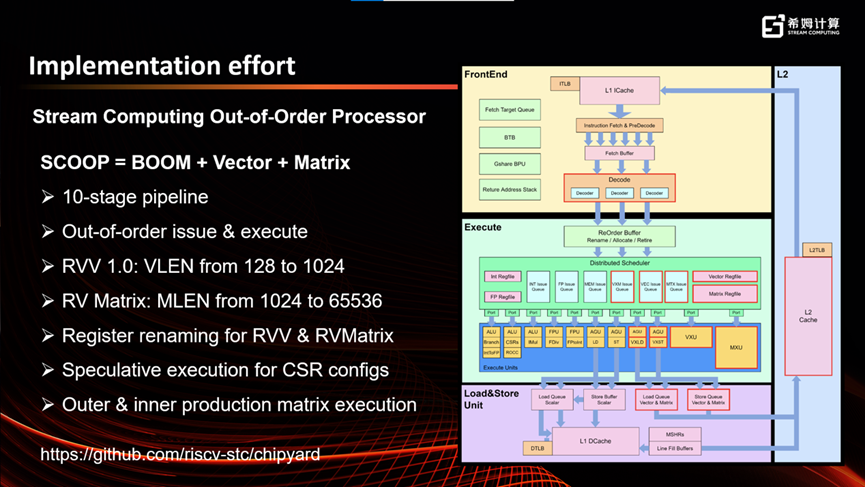

基于SCOOP(Stream Computing Out-of-Order Processor)平台的开源核心实现,包含RVV和RV Matrix支持(https://github.com/riscv-stc/chipyard)

SCOOP(Stream Computing Out-of-Orfer Processor)开源平台基于BOOM(Berkeley Out-of-Order Machine)增加了RVV 1.0和矩阵功能的支持,这使得它成为业界首个开源的RISC-V向量和矩阵项目。

截至目前,编译器、模拟器和调试器均已更新至0.5版本。开源核心已经更新到了0.2版本,并将在将来逐步更新到最新版本。

社区反馈

Community Response and Evaluations

希姆计算的研发总监范福杰博士表示:“我们非常激动能推出这个新的版本。通过引入对RISC-V矩阵指令集扩展的支持,可以大大增强希姆计算基于RISC-V架构开发高性能AI芯片的能力,同时为RISC-V指令集的改进做出贡献。此外,我们的SCOOP(Stream Computing Out-of-Order Processor)实现了与Chipyard项目的结合,这充分展示了先进威廉希尔官方网站 在现实世界的硬件设计中得到了极好的应用。”

RISC-V国际的首席执行官Calista Redmond对此次升级也给予了高度评价:“看到像希姆计算这样的创新项目积极采用和支持了RISC-V的新特性,真是令人鼓舞。矩阵指令集扩展代表了RISC-V生态系统向前迈出了重要一步,能够在特定应用场景中显著提升性能。我们对希姆计算团队的努力表示感谢,这对整个社区来说是一个巨大的胜利。”

“我们非常兴奋能与希姆计算合作,将RISC-V AI核心威廉希尔官方网站 引入我们的课堂。通过具体的工程案例进行实践学习,我们的学生将能够接触最前沿的威廉希尔官方网站 和发展趋势。这将显著提升他们的实践技能和创新能力,”北京大学集成电路学院助理教授贾天宇博士说,他已将SCOOP项目纳入今年秋季的SOC设计研究生课程中。

未来展望

Future outlook

RISC-V的开源特性已经吸引了学术界和产业界的广泛关注,其模块化设计和可扩展性能力满足了近年来人工智能计算能力的应用需求。基于RISC-V架构的AI芯片不仅能够通过扩展指令实现AI应用所需的高计算能力,还因为与RISC-V标准指令集的兼容性而在编程灵活性方面具有显著优势。

我们期待更多合作伙伴加入这个开源项目,推动计算威廉希尔官方网站 的持续进步。希姆计算将进一步加强与合作伙伴的合作,推动RISC-V在人工智能领域的发展,繁荣RISC-V生态系统,提高AI应用的兼容性,降低软件开发成本,并实现新一代的标准和可扩展的领域特定架构。

-

人工智能

+关注

关注

1791文章

47274浏览量

238468 -

开源

+关注

关注

3文章

3348浏览量

42498 -

RISC-V

+关注

关注

45文章

2277浏览量

46158

发布评论请先 登录

相关推荐

关于RISC-V学习路线图推荐

《RISC-V能否复制Linux 的成功?》

什么是RISC-V?以及RISC-V和ARM、X86的区别

RISC-V,即将进入应用的爆发期

希姆计算与开芯院签署生态合作伙伴协议,共同打造高性能RISC-V AI大算力芯片

希姆计算的RISC-V矩阵扩展开源项目已升级至0.5版本,支持向量+矩阵的实现

希姆计算的RISC-V矩阵扩展开源项目已升级至0.5版本,支持向量+矩阵的实现

评论