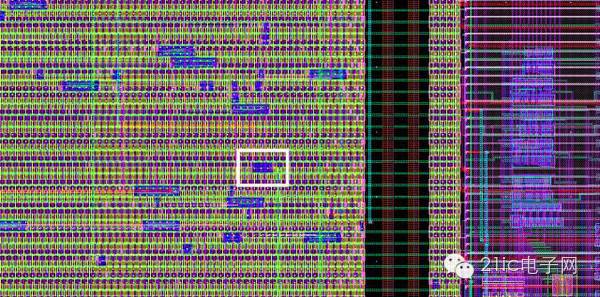

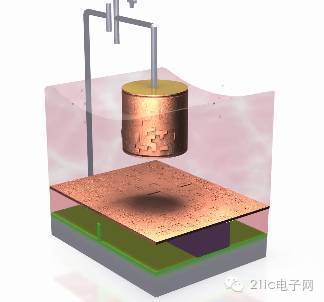

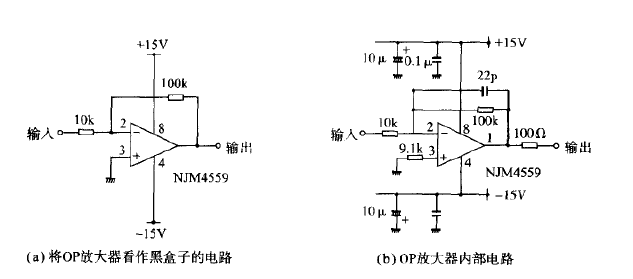

要想造个芯片, 首先, 你得画出来一个长这样的玩意儿给Foundry (外包的晶圆制造公司)(此处担心有版权问题… 毕竟我也是拿别人钱干活的苦逼phd… 就不放全电路图了… 大家看看就好, 望理解!)

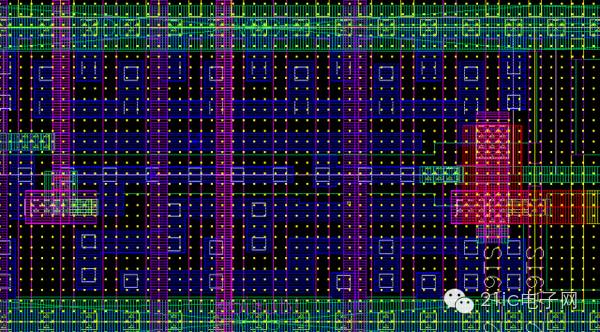

再放大...

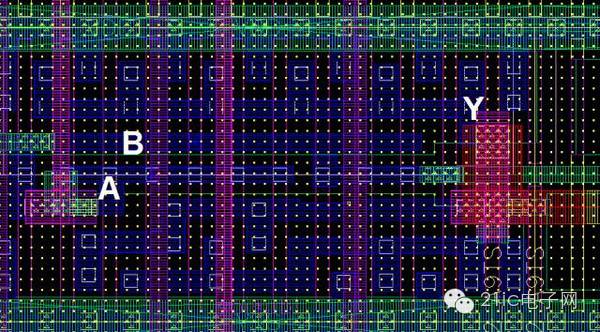

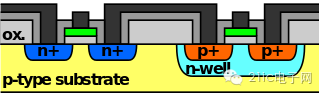

我们终于看到一个门电路啦! 这是一个NAND Gate(与非门), 大概是这样:

图片按照生产步骤排列. 但是步骤总结单独写出

1、湿洗(用各种试剂保持硅晶圆表面没有杂质)

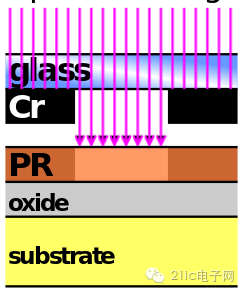

2、光刻(用紫外线透过蒙版照射硅晶圆, 被照到的地方就会容易被洗掉, 没被照到的地方就保持原样. 于是就可以在硅晶圆上面刻出想要的图案. 注意, 此时还没有加入杂质, 依然是一个硅晶圆. )

3、 离子注入(在硅晶圆不同的位置加入不同的杂质, 不同杂质根据浓度/位置的不同就组成了场效应管.)

4.1、干蚀刻(之前用光刻出来的形状有许多其实不是我们需要的,而是为了离子注入而蚀刻的. 现在就要用等离子体把他们洗掉, 或者是一些第一步光刻先不需要刻出来的结构, 这一步进行蚀刻).

4.2、湿蚀刻(进一步洗掉, 但是用的是试剂, 所以叫湿蚀刻).--- 以上步骤完成后, 场效应管就已经被做出来啦~ 但是以上步骤一般都不止做一次, 很可能需要反反复复的做, 以达到要求. ---

5、等离子冲洗(用较弱的等离子束轰击整个芯片)

6、热处理,其中又分为:

6.1、快速热退火 (就是瞬间把整个片子通过大功率灯啥的照到1200摄氏度以上, 然后慢慢地冷却下来, 为了使得注入的离子能更好的被启动以及热氧化)

6.2、退火

6.3、热氧化 (制造出二氧化硅, 也即场效应管的栅极(gate) )

7、化学气相淀积(CVD),进一步精细处理表面的各种物质

8、物理气相淀积 (PVD),类似, 而且可以给敏感部件加coating

9、分子束外延 (MBE)如果需要长单晶的话就需要这个..

10、电镀处理

11、化学/机械表面处理然后芯片就差不多了, 接下来还要:

12、晶圆测试

13、晶圆打磨就可以出厂封装了.我们来一步步看:

就可以出厂封装了.我们来一步步看:

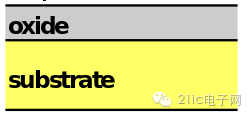

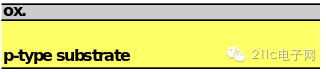

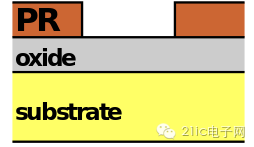

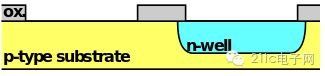

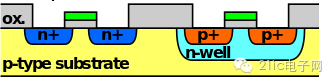

1、上面是氧化层, 下面是衬底(硅) -- 湿洗

2、一般来说, 先对整个衬底注入少量(10^10 ~ 10^13 / cm^3) 的P型物质(最外层少一个电子), 作为衬底 -- 离子注入

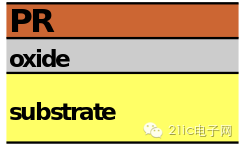

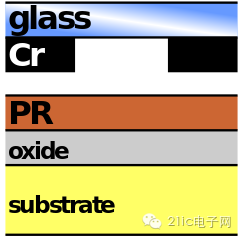

4、上掩膜! (就是那个标注Cr的地方. 中间空的表示没有遮盖, 黑的表示遮住了.) -- 光刻

5、紫外线照上去... 下面被照得那一块就被反应了 -- 光刻

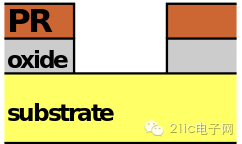

6、撤去掩膜. -- 光刻

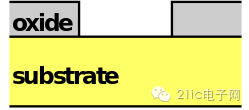

7、把暴露出来的氧化层洗掉, 露出硅层(就可以注入离子了) -- 光刻

8、把保护层撤去. 这样就得到了一个准备注入的硅片. 这一步会反复在硅片上进行(几十次甚至上百次). -- 光刻

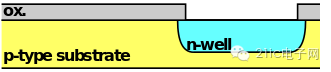

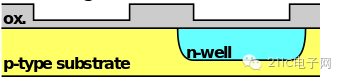

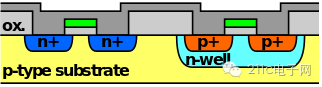

9、然后光刻完毕后, 往里面狠狠地插入一块少量(10^14 ~ 10^16 /cm^3) 注入的N型物质就做成了一个N-well (N-井) -- 离子注入

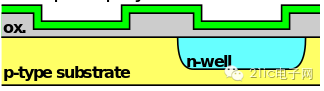

10、用干蚀刻把需要P-well的地方也蚀刻出来. 也可以再次使用光刻刻出来. -- 干蚀刻

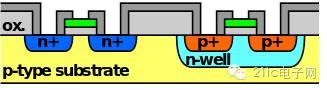

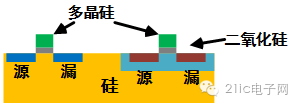

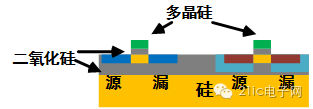

11、上图将P-型半导体上部再次氧化出一层薄薄的二氧化硅. -- 热处理

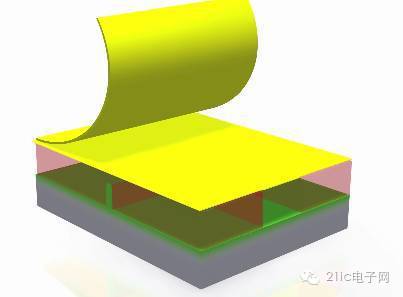

12、用分子束外延处理长出的一层多晶硅, 该层可导电 -- 分子束外延

13、进一步的蚀刻, 做出精细的结构. (在退火以及部分CVD) -- 重复3-8光刻 + 湿蚀刻13 进一步的蚀刻, 做出精细的结构. (在退火以及部分CVD) -- 重复3-8光刻 + 湿蚀刻

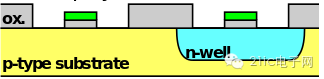

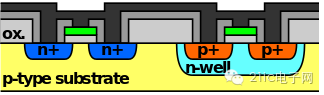

14、再次狠狠地插入大量(10^18 ~ 10^20 / cm^3) 注入的P/N型物质, 此时注意MOSFET已经基本成型. -- 离子注入

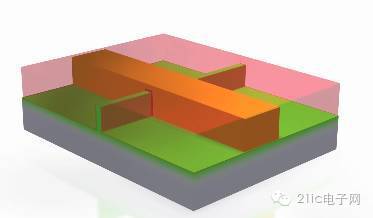

15、用气相积淀 形成的氮化物层 -- 化学气相积淀

16、将氮化物蚀刻出沟道 -- 光刻 + 湿蚀刻

17、物理气相积淀长出 金属层 -- 物理气相积淀

书名: << IC Fabrication Technology >> By BOSE

细说一下光刻. 题主问了: 小于头发丝直径的操作会很困难, 所以光刻(比如说100nm)是怎么做的呢?

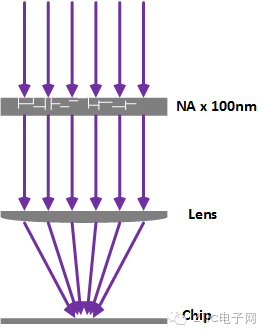

比如说我们要做一个100nm的门电路(90nm technology), 那么实际上是这样的:

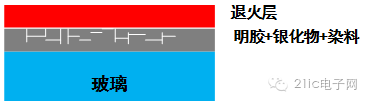

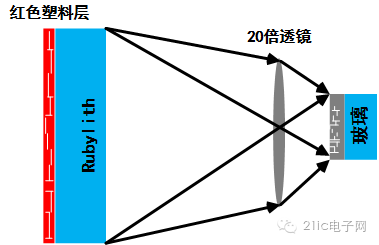

这层掩膜是第一层, 大概是10倍左右的Die Size有两种方法制作: Emulsion Mask 和 Metal MaskEmulsion Mask:

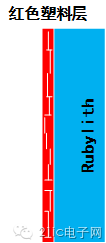

这货分辨率可以达到 2000line / mm (其实挺差劲的... 所以sub-micron ,也即um级别以下的 VLSI不用... )这货分辨率可以达到 2000line / mm (其实挺差劲的... 所以sub-micron ,也即um级别以下的 VLSI不用... )制作方法: 首先: 需要在Rubylith (不会翻译...) 上面刻出一个比想要的掩膜大个20倍的形状 (大概是真正制作尺寸的200倍), 这个形状就可以用激光什么的刻出来, 只需要微米级别的刻度.

给!它!照!相! , 相片就是Emulsion Mask! 给!它!照!相! , 相片就是Emulsion Mask! 如果要拍的"照片"太大, 也有分区域照的方法. Metal Mask:

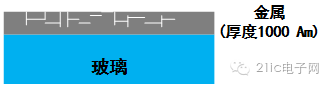

制作过程:

1、先做一个Emulsion Mask, 然后用Emulsion Mask以及我之前提到的17-18步做Metal Mask! 瞬间有种Recursion的感觉有木有!!!

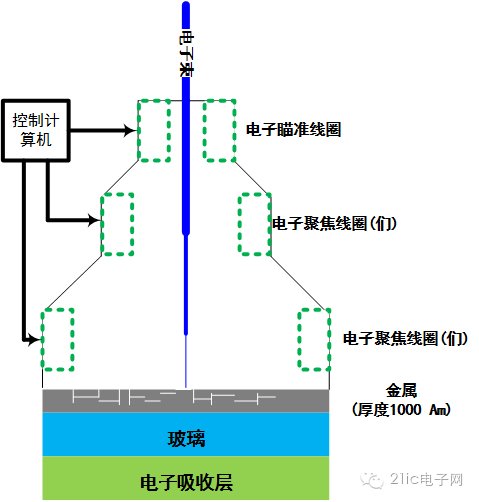

2、Electron beam:

大概长这样

就像打印机一样把底下打一遍.

好处是精度特别高, 目前大多数高精度的(<100nm威廉希尔官方网站 )都用这个掩膜. 坏处是太慢...

做好掩膜后:

Feature Size = k*lamda / NA

k一般是0.4, 跟制作过程有关; lamda是所用光的波长; NA是从芯片看上去, 放大镜的倍率.

以目前的威廉希尔官方网站 水平, 这个公式已经变了, 因为随着Feature Size减小, 透镜的厚度也是一个问题了

Feature Size = k * lamda / NA^2

恩.. 所以其实掩膜可以做的比芯片大一些. 至于具体制作方法, 一般是用高精度计算机探针 + 激光直接刻板. Photomask(掩膜) 的材料选择一般也比硅晶片更加灵活, 可以采用很容易被激光汽化的材料进行制作.

这个光刻的方法绝壁是个黑科技一般的点! 直接把Lamda缩小了一个量级, With no extra cost! 你们说吼不吼啊!

Food for Thought: Wikipedia上面关于掩膜的版面给出了这样一幅图, 假设用这样的掩膜最后做出来会是什么形状呢?

附图的步骤在每幅图的下面标注, 一共18步.

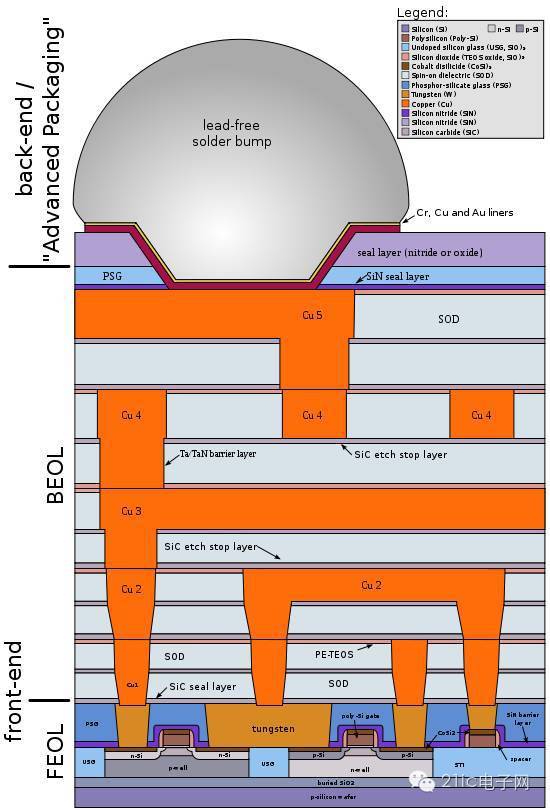

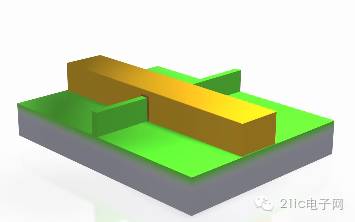

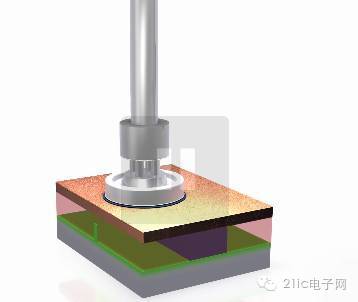

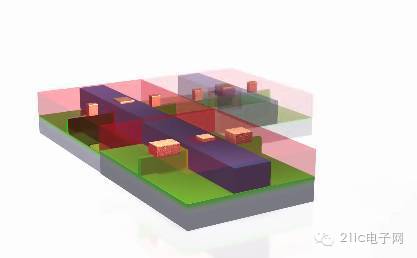

最终成型大概长这样:

其中, 步骤1-15 属于 前端处理 (FEOL), 也即如何做出场效应管

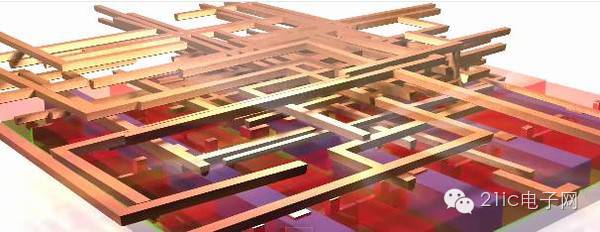

步骤16-18 (加上许许多多的重复) 属于后端处理 (BEOL) , 后端处理主要是用来布线. 最开始那个大芯片里面能看到的基本都是布线! 一般一个高度集中的芯片上几乎看不见底层的硅片, 都会被布线遮挡住.

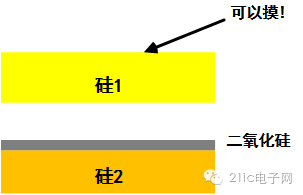

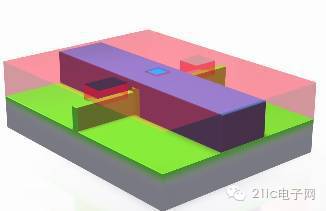

SOI (Silicon-on-Insulator) 威廉希尔官方网站 :

传统CMOS威廉希尔官方网站 的缺陷在于: 衬底的厚度会影响片上的寄生电容, 间接导致芯片的性能下降. SOI威廉希尔官方网站 主要是将 源极/漏极 和 硅片衬底分开, 以达到(部分)消除寄生电容的目的.

传统:

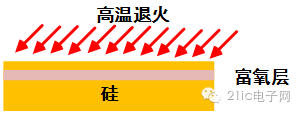

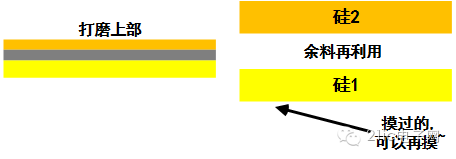

制作方法主要有以下几种(主要在于制作硅-二氧化硅-硅的结构, 之后的步骤跟传统工艺基本一致.)1. 高温氧化退火:

等氧离子渗入硅层, 形成富氧层

成型.

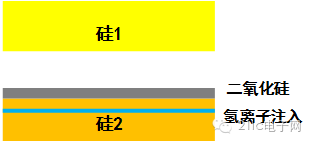

或者是2. Wafer Bonding(用两块! )不是要做夹心饼干一样的结构吗? 爷不差钱! 来两块!

来两块!

对硅2进行表面氧化

对硅2进行氢离子注入对硅2进行氢离子注入

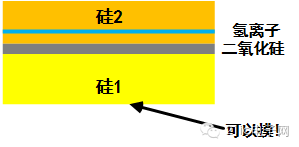

翻面

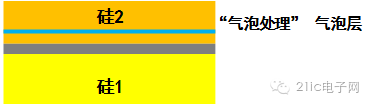

将氢离子层处理成气泡层将氢离子层处理成气泡层

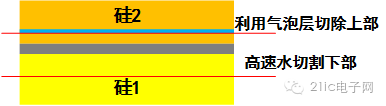

切割掉多余部分切割掉多余部分

成型! + 再利用

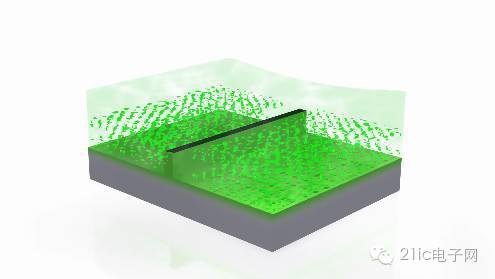

光刻

微观图长这样:

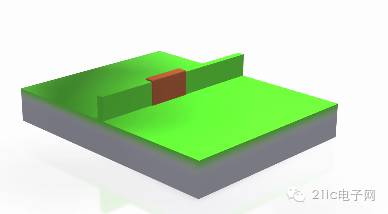

再次光刻+蚀刻

撤去保护, 中间那个就是Fin撤去保护, 中间那个就是Fin

门部位的多晶硅/高K介质生长门部位的多晶硅/高K介质生长

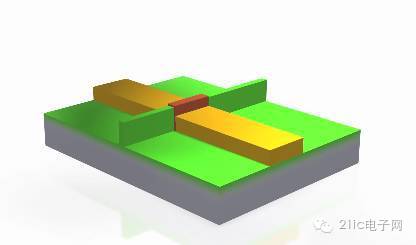

门部位的氧化层生长门部位的氧化层生长

长成这样

源极 漏极制作(光刻+ 离子注入)

初层金属/多晶硅贴片

蚀刻+成型

物理气相积淀长出表面金属层(因为是三维结构, 所有连线要在上部连出)

机械打磨(对! 不打磨会导致金属层厚度不一致)

成型! 成型!

大概就是酱紫...

-

芯片

+关注

关注

455文章

50812浏览量

423583 -

晶体管

+关注

关注

77文章

9692浏览量

138178

原文标题:芯片里面的几千万的晶体管是怎么装进去的?

文章出处:【微信号:weixin21ic,微信公众号:21ic电子网】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Multisim里面雪崩晶体管的过压击穿怎么放着

晶体管电路设计

芯片里面100多亿晶体管是如何实现的

什么是晶体管 晶体管的分类及主要参数

芯片上如何集成晶体管 晶体管的结构特点有哪些

晶体管和芯片的关系

芯片内部晶体管的工作原理

详细解析芯片里面的几千万的晶体管的实现

详细解析芯片里面的几千万的晶体管的实现

评论