说到射频的难点不得不提杂散,杂散也是射频被称为“玄学”的来源。杂散也是学习射频必经的一个难点。本篇文章就来讲一下杂散。

杂散是什么?

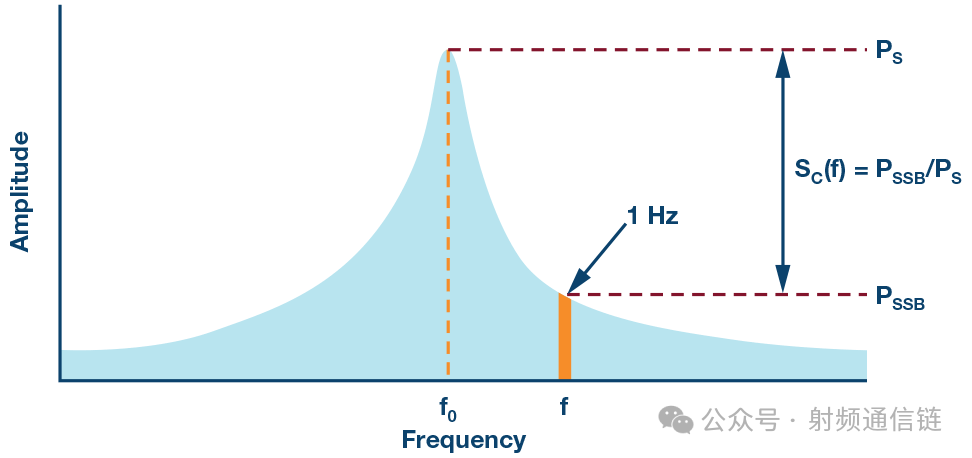

杂散(Spurious Emissions),指的是必要带宽之外的一个或多个频率上的发射,其发射电平可以降低而不致影响相应信息的传递。杂散发射包含谐波发射、寄生发射、互调产物及变频产物,但带外发射除外。具体来说,杂散发射是在使用标准信号调制时,在除载频和由于正常调制和切换瞬态引起的边带以及邻道以外离散频率上的辐射。这些杂散信号可能会干扰其他通信系统,降低系统性能,并违反无线电通信法规。

简单来说,杂散(Spurious)指的是不需要的信号或噪声。

杂散有什么影响?

杂散的危害有分两大类,一类是对自己的设备有影响;二是对其他设备有影响。

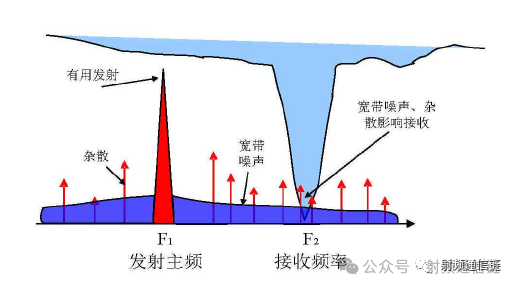

对自己的设备有影响典型的例子就是FDD模式,频分双工,发射的杂散落到接收机,对接收机的灵敏度有影响,降低接收机的灵敏度。

杂散从哪里来?

要想解决“玄学”问题,必须要知道它从哪里来,不需要的信号都不是凭空产生的,都是有来源的,抓住主要矛盾,就会有应对的方法。

一般来说杂散来源有五个:

一、非线性

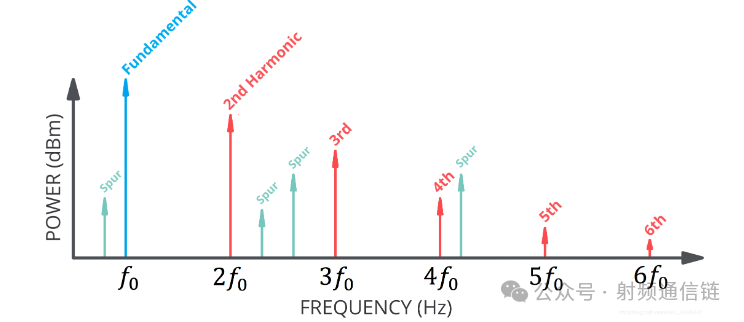

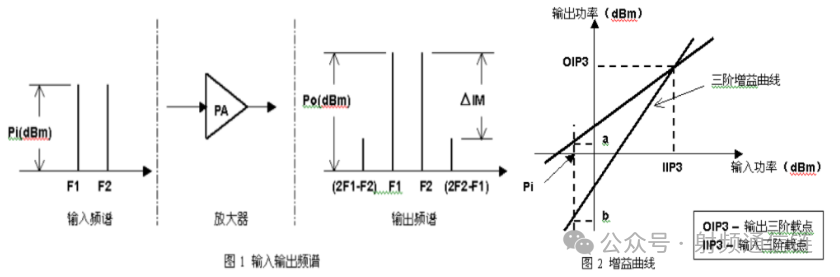

功率放大器的非线性,放大器是一个非线性器件,单音输入会产生谐波;双音输入不仅有谐波,还有交调。

二、混频器

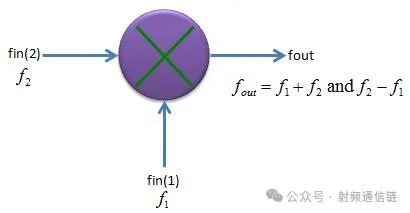

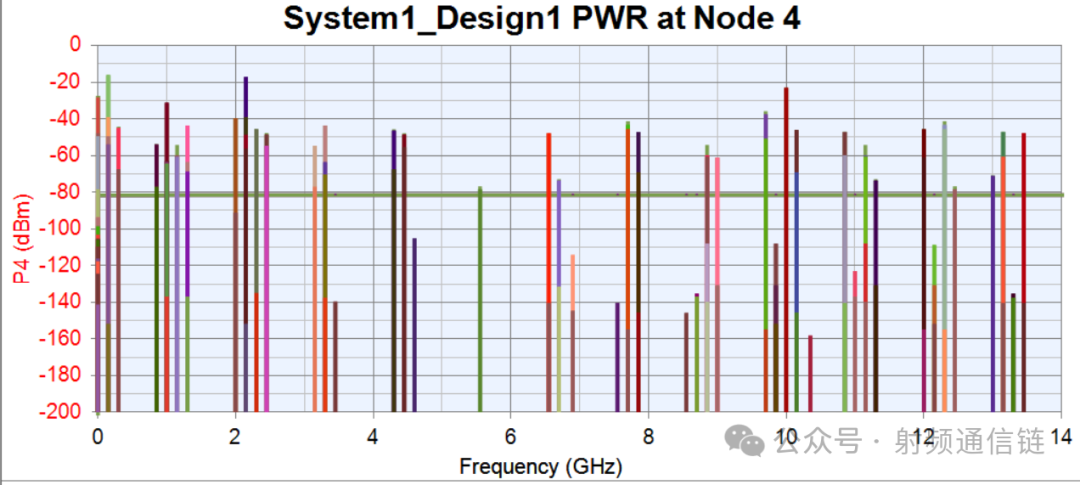

混频器是射频电路中的一个关键器件,也是一个典型的非线性器件。它可以产生丰富的混频杂散mRF±nLO.

三、频率源

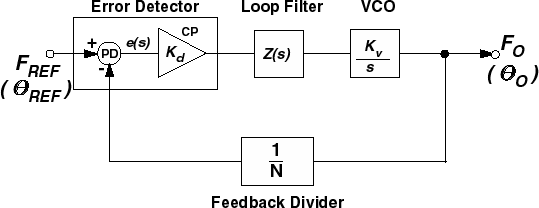

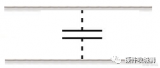

为了频率的精度,一般电路中都会采用频率源,频率源一般采用锁相环形式,锁相环的原理图如下图所示

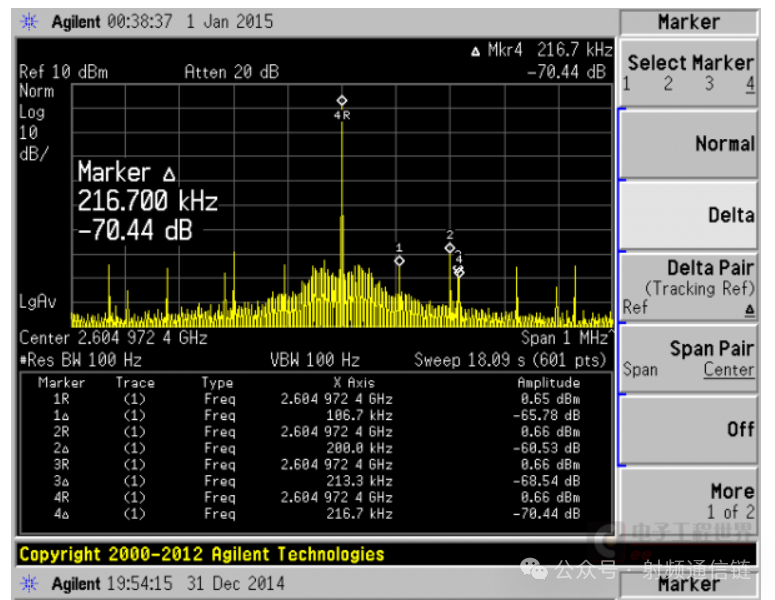

锁相环的组成是通过参考源来调整VCO实现频率的锁定,而鉴相一般就是整数分频或者小数分频,所以锁相环就会有以下杂散

参考杂散:这是PLL中最常见的杂散信号,主要由于电荷泵源电流与汇电流的失配、电荷泵漏电流以及电源退耦不够而增大。这些杂散信号会与其他干扰信号混频,可能产生有用信号频率,从而降低接收机的灵敏度。

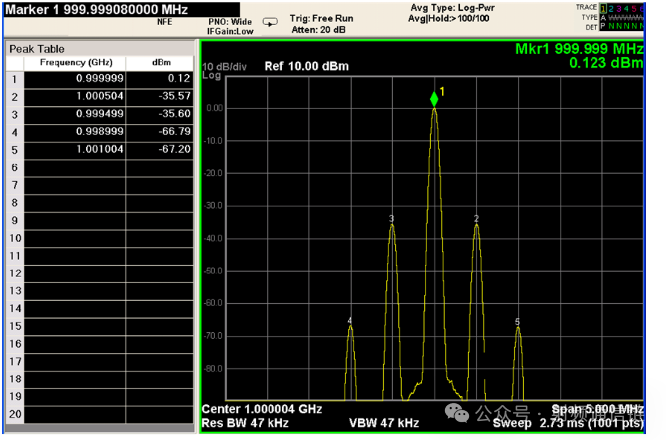

整数边界杂散:当PLL的输出频率接近参考频率的整数倍时,会产生此类杂散。这种杂散无法被环路滤波器滤除,因此会在输出频率附近产生显著的杂散信号。例如,如果参考输入为20 MHz,而输出频率为1000.1 MHz,那么就会产生1000 MHz的整数杂散。

小数杂散:小数PLL是目前锁相环的主流应用,小数杂散的来源主要有鉴相杂散和泵电流杂散。降低小数杂散主要通过改变小数分频比和鉴相频率,目的是改变小数杂散的相对位置,然后通过低通滤波器进行压制。

电荷泵杂散:PLL电荷泵存在泄漏,如参考频率、鉴相频率、数字时钟干扰等,这些都可能以杂散的形式表现。

电源杂散:电源存在纹波和DC-DC共模干扰,这些也可能引起PLL的杂散。

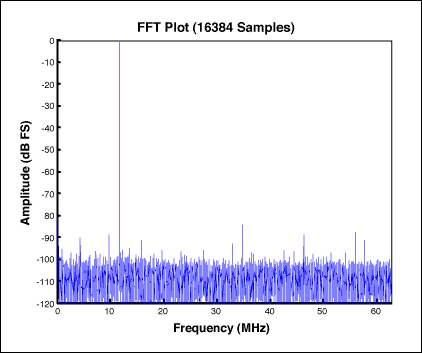

电路中一般都会有AD/DA来实现interwetten与威廉的赔率体系 数字的转换,模拟数字的转换和混频一样,也会产生杂散

ADC会产生混叠杂散

DAC会产生因为非线性,串扰,匹配产生杂散

五、电源杂散

DCDC电源是通过开关切换实现电源的输出。DCDC的开关有频率,会生成开关频率杂散。

DC-DC开关频率越高,输出滤波电容容值越小;负载电流越大,输出滤波电容容值越大;输入电压与输出电压差越大,输出滤波电容容值越大。DC-DC效率越高,开关转换速度越快,高次谐波越丰富

杂散的解决

杂散的来源就是以上几个来源,定位到杂散的来源就可以针对性进行优化

1.放大器的非线性杂散

增加滤波器的阶数,实现对谐波的抑制

2.混频器

对于混频杂散,最好的方式是通过频率规划,将杂散规划到离主频较远的地方通过滤波器来抑制。

3.频率源

通过改变环路滤波器设计、泵电流大小、分频比来实现杂散的抑制

4.ADC/DAC杂散

使用抗混叠滤波器、提升采样率、优化阻抗匹配

5.电源杂散

通过优化DCDC滤波器电路,优化纹波设计

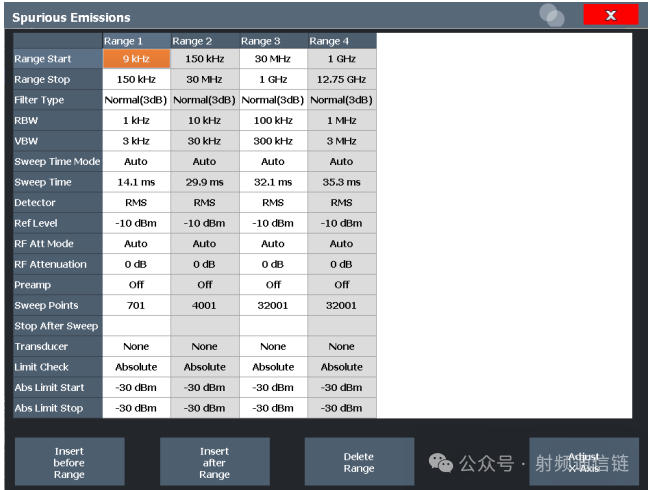

杂散的测试

杂散的测试一般采用频谱仪测试,为了测量低电平杂散,通常需要降低分辨率带宽,而这会增加测量时间、也可能会漏掉某些杂散。现在频谱仪厂家都提供了杂散测试模版,根据测试要求可以自动测试杂散幅度和频点。

-

放大器

+关注

关注

143文章

13584浏览量

213368 -

射频

+关注

关注

104文章

5574浏览量

167695 -

接收机

+关注

关注

8文章

1180浏览量

53455 -

混频器

+关注

关注

10文章

679浏览量

45668

原文标题:射频基础—杂散是什么?

文章出处:【微信号:射频美学,微信公众号:射频美学】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

最麻烦的PLL杂散信号——整数边界杂散

PCB杂散电容大小计算方法 PCB杂散电容怎么消除

杂散有什么影响?杂散从哪里来?

杂散有什么影响?杂散从哪里来?

评论