文章来源:学习那些事

原文作者:小陈婆婆

在半导体制造流程中,晶圆测试是确保产品质量和性能的关键环节。与此同时封装过程中的缺陷对半导体器件的性能和可靠性具有重要影响,本文就上述两个方面进行介绍。

晶圆测试

对于碳化硅(SiC)材料而言,由于其独特的物理和化学性质,测试过程尤为重要。以下是以碳化硅晶圆为例,对其电学测试系统的详细解析。

测试系统概述

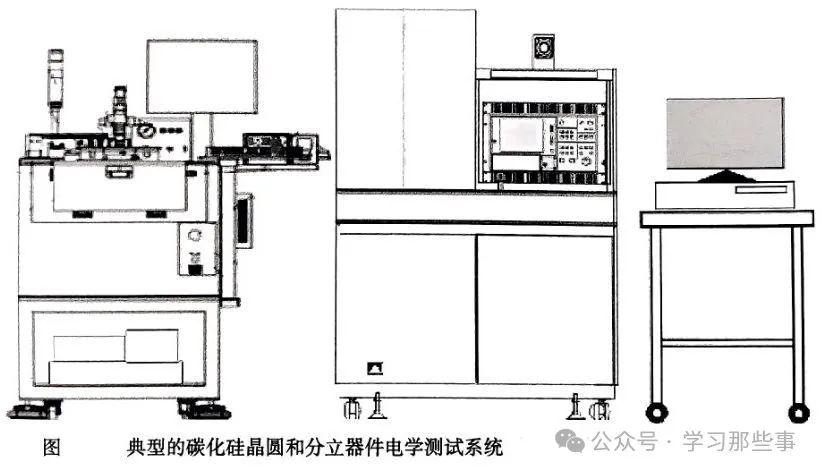

如上图所示,一个典型的碳化硅晶圆和分立器件电学测试系统主要由三部分组成:电学检测探针台、晶体管检测仪以及控制用计算机。这三部分协同工作,共同构成了完整的测试系统。

探针台解析

探针台如图所示,是测试系统的核心部件之一,主要负责晶圆的电学检测。它主要由载物台、探卡、绝缘气体供应设备等组成。

载物台:用于放置晶圆,可以兼容4~8寸的晶圆。载物台上设有真空气孔,能够牢固地吸附住晶圆,防止在测试过程中晶圆发生移位。

探卡:通过探针与晶圆上的电极接触,实现电信号的传输和检测。

绝缘气体供应设备:提供压缩空气和N₂等绝缘气体,用于防止在测试高压过程中发生“打火”现象。此外,还可以将晶圆浸泡在氟油中进行测试,以提高测试的绝缘效果和准确性。氟油测试法不仅测试效果优于压缩空气绝缘,而且测试完成后氟油容易挥发,不会污染晶圆表面。

曲线追踪仪功能

曲线追踪仪,如图所示是测试系统的另一个重要部件,主要用来输出高电压和大电流,并通过连线传导到探针上。

电源配置:仪器内部含有集电极电源和步进式信号源两组电源,可通过线路配置将电压加到集电极、发射极和基极上,以满足不同的测试需求。

测试电路:设备中包含7种固定的测试电路,可用于完成不同的测试项,如正向电压测试、反向漏电流测试等。

测试实例分析

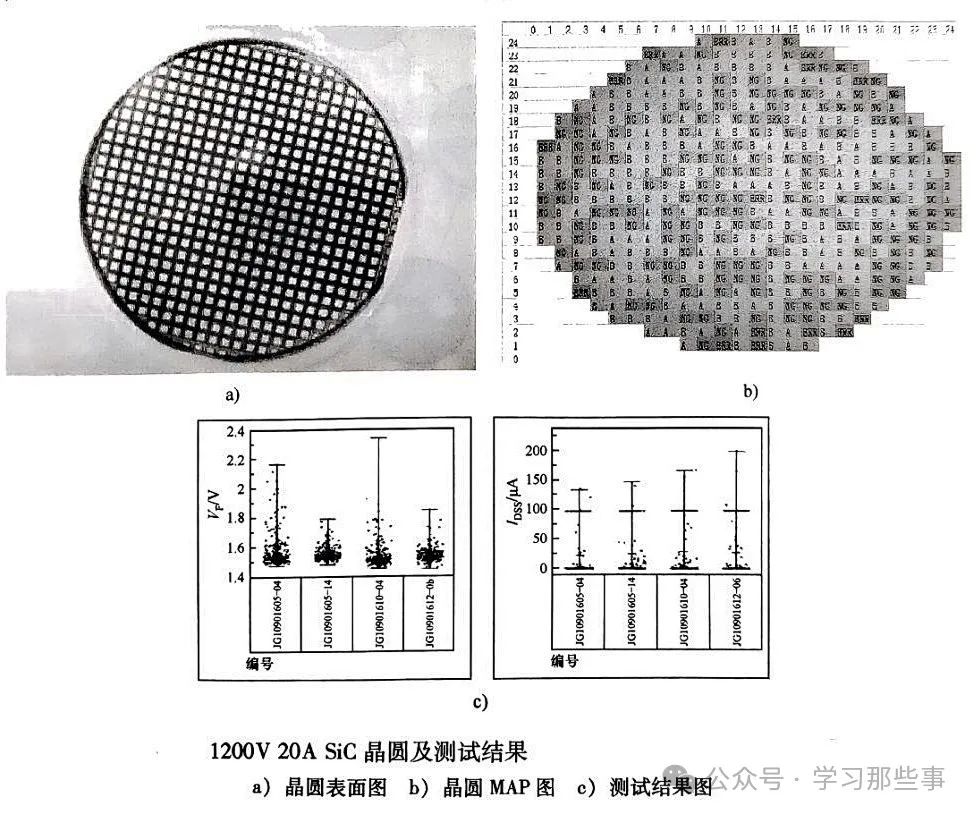

晶圆结构:如图a所示,1200V 20A SiC SBD晶圆正面为阳极,背面为阴极。

测试过程:探针台内的步进式电机带动载物台对晶圆进行点测。通过步进式扫描,可以得到晶圆上每个测试点的电学性能数据。

测试结果:如图b所示,通过等级MAP图可以直观地看到晶圆上各测试点的性能分类(A、B、NG、ERR)。对5块晶圆的测试结果进行汇总(如图c所示),可以看出VF基本都在1.5~1.6V之间,反向IDSS漏电流大部分都在10μA以下。这表明晶圆正向分布的一致性良好,但反向特性仍有进一步提升的空间。

综上所述,硅晶圆电学测试系统是一个复杂而精细的系统,通过合理的配置和精确的测试,可以确保晶圆的质量和性能符合设计要求。

封装过程缺陷解析

封装过程是半导体器件制造中的关键环节,其质量直接影响器件的性能和可靠性。以下是封装过程中常见的缺陷及其详细解析:

装片空洞

定义:装片空洞是指在封装过程中,由于密封不良、装片机参数设置不当或芯片表面存在异物(如氧化物)等原因,导致芯片与框架基岛之间未能形成良好的黏结或钎接,从而产生空洞。

影响:空洞的存在会严重影响功率器件的导电性,导致RDS(ON)值超标,进而影响器件的性能。此外,空洞还会降低芯片的导热效率,形成热量聚集点,增加器件在温度和功率循环过程中的受力不均匀性,从而引发焊料层裂纹,进一步影响封装产品的可靠性。

控制标准:一般功率芯片对空洞的大小和总面积有严格规定,非车规级产品中要求总面积不超过芯片面积的10%,单个空洞不超过5%。

键合不良

定义:键合不良包括引线短路、弹坑损伤、第二焊点虚焊或键合强度弱等问题。

影响:引线短路会导致不同极性的焊线之间发生击穿,造成功率器件失效。弹坑损伤和虚焊会降低键合强度,使得器件在受到交变应力时容易发生接触不良,进而影响器件的可靠性和使用寿命。

预防措施:在封装体设计时,应确保不同极性的焊线之间的距离足够大,以避免击穿短路。同时,应严格控制封装过程中的工艺参数,以减少对芯片的机械冲击,并确保焊料厚度和冷却速率合适,以减少热应力冲击。

封装破裂

定义:封装破裂是指在封装过程中,由于机械冲击、热应力等因素导致的芯片内部或表面出现裂纹。

影响:封装破裂可能导致器件的瞬间电气失效,尤其是当裂纹生长到影响电路连接时。裂纹还会降低器件的可靠性,因为裂纹的扩展需要时间,所以即使初始时能通过功能检测,也可能在后续的使用环境中出现问题。

预防措施:应严格控制封装过程中的工艺参数,以减少对芯片的机械冲击。同时,应确保有足够的焊料厚度来阻止裂纹的扩展,并选择合适的冷却速率来减少热应力冲击。此外,还应严格控制划片过程中的崩角大小,以防止裂纹的产生。

综上所述,在封装过程中应严格控制各项工艺参数和条件,以确保封装质量符合设计要求。同时,还应加强质量检测和控制手段,及时发现并处理潜在的缺陷问题。

-

半导体

+关注

关注

334文章

27300浏览量

218138 -

晶圆

+关注

关注

52文章

4894浏览量

127936 -

碳化硅

+关注

关注

25文章

2748浏览量

49020

原文标题:晶圆测试与缺陷解析

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

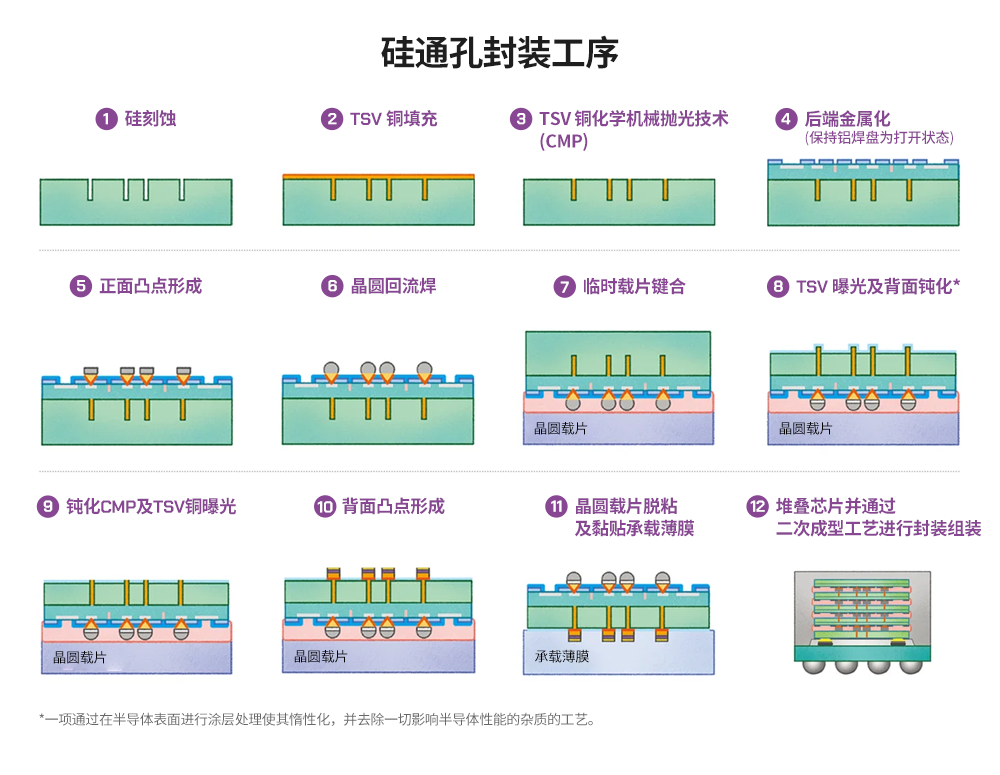

晶圆级多层堆叠威廉希尔官方网站 及其封装过程

什么是晶圆级封装?

LED封装过程中的存在缺陷检测方法介绍

晶圆封装过程缺陷解析

晶圆封装过程缺陷解析

评论