在高速实时或者非实时信号处理系统当中,使用大容量存储器实现数据缓存是一个必不可少的环节,也是系统实现中的重点和难点之一。SDRAM(同步动态随机访问存储器)具有价格低廉、密度高、数据读写速度快的优点,从而成为数据缓存的首选存储介制裁。但是SDRAM存储体结构与RAM有较大差异,其控制时序和机制也较复杂,限制了SDRAM的使用。目前,虽然一些能家长微处理器提供了和SDRAM的透明接口,但其可扩展性和灵活性不够,难以满足现实系统的要求,限制了SDRAM的使用。

在详细阐读SDRAM数据文档的前提下,参考ALTERA公司的IP core,利用可编程器件(CPLD,FPGA)设计了一种通用的SDRAM控制器。它具有很高的灵活性,可以方便地和其它数据采集分析系统中,如图1所示。在该系统中,以SDRAM存储阵列缓存中频来的高速数据。存满后,数据被慢速读出至数据处理模块。下面将对SDRAM控制模块的设计进行详细的描述。

1 SDRAM内存条的结构

SDRAM内存条由SDRAM内存芯片构成,根据内存条的容量大小决定内存条上内存芯片的个数。现以MICRON公司生产的TIM16LSDT6464A型SDRAM内存条为例,简要介绍SDRAM的结构。

MIT16LSDT6464A内存条容量为512M Byte,由16片容量为32M Byte的内存芯片MT46LC32M8A2构成。16片内存芯片被分为两级,每个芯片的数据位宽为8bit.8片一组,64bit数据宽度。每个内存芯片的数据线和控制均是复用的。对内存条的读写操作,是以内存芯片组为单位的,通过内存条的片选信号S0、S1、S2、S3决定组号。S0、S2控制芯片组1,S1、S3控制芯片组2.

SDRAM内存芯片的主要信号有控制信号、控制信号、数据信号,均为工作时钟同步输入、输出信号。

控制信号主要有:CS(片选信号),CKE(时钟使能信号),DQM(输入、输出使能信号),CAS、RAS、WE(读写控制命令字)。通过CAS、RAS、WE的各种逻辑组合,可产生各种控制命令。

地址信号有:BA0和BA1页地址选择信号,A0~A12地址信号,行、列地址选择信号。通过分时复用决定地址是行地址还是列地址。在读写操作中,在地线上依次给出页地址、行地址、列地址,最终确定存储单元地址。

数据信号有:DQ0~DQ7,双向数据。其使能受DQM控制。

SDRAM的工作模式通过LOAD MODE REGISTER命令对工作模式寄存器进行设置来选择。设置参量有Reserved(备用的人)Write Burst Mode(WB,写突发模式)、Operation Mode(Op Mode,工作模式)、CAS Latency(CAS延迟)、Burst Type(BT,突发类型)、Burst Length(突发长度)。

2 SDRAM的基本读写操作

SDRAM的基本读操作需要控制线和地址线相配合地发出一系列命令来完成。先发出BANK激活命令(ACTIVE),并锁存相应的BANK地址(BA0、BA1给出)和行地址(A0~A12给出)。BANK激活命令后必须等待大于tRCD(SDRAM的RAS到CAS的延迟指标)时间后,发出读命令字。CL(CAS延迟值)个工作时钟后,读出数据依次出现在数据总线上。在读操作的最后,要向SDRAM发出预充电(PRECHARGE)命令,以关闭已经激活的页。等待tRP时间(PRECHARGE)命令,以关闭已经激活的页。等待tRP时间(PRECHAREG命令后,相隔tRP时间,才可再次访问该行)后,可以开始下一次的读、写操作。SDRAM的读操作只有突发模式(Burst Mode),突发长度为1、2、4、8可选。

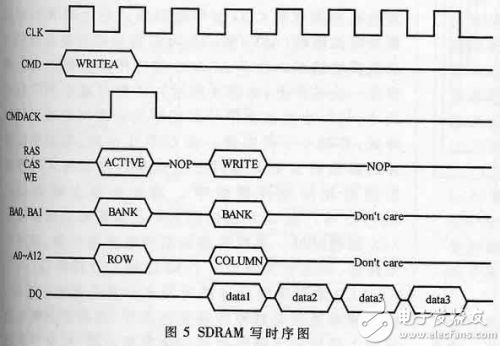

SDRAM的基本写操作也需要控制线和地址线相配合地发出一系列命令来完成。先发出BANK激活命令(ACTIVE),并锁存相应的BANK地址(BA0、BA1给出)和行地址(A0~A12给出)。BANK激活命令后必须等待大于tRCD的时间后,发出写命令字。写命令可以立即写入,需写入数据依次送到DQ(数据线)上。在最后一个数据写入后延迟tWR时间。发出预充电命令,关闭已经激活的页。等待tRP时间后,可以展开下一次操作。写操作可以有突发写和非突发写两种。突发长度同读操作。

tRCD、tRP、tWR的具体要求,详见SDRAM厂家提供的数据手册。所等待的工作时钟个数由tRCD、tRP、tWR的最小值和工作时钟周期共同决定。

由以上介绍可以得出,SDRAM的读、写操作均由一系列命令组成,因此读、写操作是有时钟损耗的,工作时钟速率不等于SDRAM能达到的读、写速率。但是由于SDRAM有突发读、写模式,也就是说可以读出和写入一串地址连续的数据,从而提高了效率。当突发长度为整页时,读、写速度达到最快。随机读、写速度的计算公式为:

furite/read=工作时钟频率(HzHzHhdkkdk ss dkkdkdkd,,,m,mddddd)×数据宽度(bytes)×突发读写长度/操作所需的时钟数

为了提高存储密度,SDRAM采用硅片电容存储信息。电容总会有漏电流流过,所以为了不使信息丢失,必须定期地给电容刷新充电。外部控制逻辑必须按要求定期向内存条发出刷新命令,保证在规定的时间内对每一个单元都进行刷新。

3 初始化操作

SDRAM在上电以后必须对其进行初始化操作,具体操作如下:

(1)系统在上电后要等待100~200μs.在待时间到了以后至少执行一条空操作或者指令禁止操作。

(2)对所有芯片执行PRECHARGE命令,完成预充电。

(3)向每组内存芯片发出两条AUTO REFRESH命令,使SDRAM芯片内部的刷新计数器可以进入正常运行状态。

(4)执行LOAD MODE REGISTER命令,完成对SDRAM工作模式的设定。

完成以上步骤后,SDRAM进入正常工作状态,等待控制器对其进行读、写和刷新等操作。

4 SDRAM控制器设计

4.1 功能说明

在以SDRAM作为缓存的系统中,使用可编程器件对其进行控制具有很强的灵活性。为了使设计具有模块化和可重复使用的优点,设计了一个简化的SDRAM接口电路。这样就屏蔽掉了SDRAM操作的复杂性,而其它逻辑模块可通过接口电路对SDRAM进行访问。此外,由于整个SDRAM控制器用VHDL语言编写,只要对其进行简单的修改就可以满足不同的需求,具有很强的灵活性。

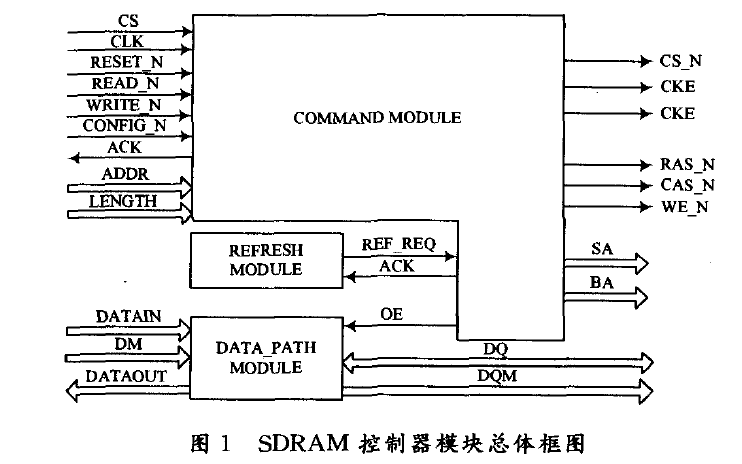

参照图2,SDRAM控制器完成的主要功能是对CMD[2:0]的命令字和ADDR端的地址进行解析,产生相应的SDRAM的控制时序。

CLK为输入的工作时钟端口。

ADDR为输入地址端口。控制器将其解析为对应的片选、页以及行、列地址。以一条MIT16LSDT6464A内存条为例,其大小为512Mbyte(2 29 byte)。数据位宽为64bit(8byte),则地址线ADDR应为26根。可以这样映射地址:ADDR[25]对应内存芯片组号;ADDR[24:23]对应页号;ADDR[22:10]对应行号;ADDR[9:0]对应列号。

DATAIN为写入数据端口,64bit位宽。

DATAOUT为读出数据端口,64bit位宽。

RD_OE为读出数据使能端口,当其为1时,表示从下一个时钟起,数据将依次出现在DATAOUT口上。

WR_OE为写入数据使能端口,当其为1时,写入数据应该依次出现在DATAIN口上。

CMD[2:0]为命令输入端口,分别表示读、写内存等待操作。其中,CMD=“000”表示无操作,内存条交给控制器管理,定其完成刷新工作;REFRESH命令由外部逻辑指定特刷新的内存芯片信号,组号由ADDR的低位给出;LOAD_MODE命令执行内存条工作寄存器初始化工作,初始化值由DATAIN的低13位决定,内存芯片组号同样由ADDR的低位给出;同理,ADDR的低位也决定了预充电操作所对应的内存芯片组号。

CMDACK为命令应答端口,表示命令已经被执行,使外部逻辑可以向控制器发出下一个动作。

4.2 状态机

图3是SDRAM控制器的状态转移图。状态图中的各个状态内均包含一系列的子状态转移(对SDRAM内存条发出连续命令),每个子状态完成一个功能操作。初始化操作包括前面介绍的内存条初始化全过程,工作寄存器的默认值在VHDL程序中指定。以后可以通过LOAD_MODE命令改变内存条的工作模式。初始化结束后,内存条进入Idel状态,刷新计数器开始工作,控制器开始响应外部逻辑的操作请求。

刷新计数器操作是一个独立的进程(process)。刷新计数器的初值由内存芯片要求、内存条个数和控制器工作频率共同决定。例如,在本次设计中,所采用的MT48LC32M8A2内存芯片要求在64ms内夏至少刷新8196次。而MIT16LSDT6464A型内存条共有两组内存芯片,也就是要求在64ms内要发出8196×2条自刷新(AUTO REFRESH)指令。系统工作时钟为46.66MHz,因此控制单条MIT16LSDT6464A时,刷新计数器初值至多为(64ms/8196/2)×6、、46.66MHz,即182.开始工作后,每当刷新计数器值减为0,便依次向内存芯片组发出刷新命令,保证SDRAM中的数据不丢失。刷新请求是内存请求;读和写操作是外部请求。在Idel状态中有请求仲裁逻辑,当内部和外部请求同时出现时,优先保证内部请求,状态转移至刷新操作。当刷新操作结束时,重新返回Idel状态,开始响应外部请求。响应外部请求后,应答信号CMDBAK出现正脉冲。它通知外部逻辑,请求已经被响应,可以撤销请求。在刷新操作状态中,也有许数器计数,其大小等于控制器管理的内存芯片信号。记录并判断此次刷新操作所对应的内存芯片的组号,产生相应的片选信号。

响应读、写请求后,状态从Idel转移到读、写状态。同时读、写地址和写入的数据锁存至控制器。控制器由读写地址解析出CS信号、页地址、行地址、列地址。向内存条发出一系列命令(ACTIVE,READ/WRITE with AUTO PRECHARGE),完成读写操作,为了简化,此控制器向SDRAM发出的都是带有AUTO PRECHARGE的读、写指令,然后由SDRAM内部逻辑自动在读、写过程末期发出PRECHARGE指令(在发READ/WRITE指令时,地址线A10赋值1,打开AUTO PRECHARGE功能)。图4和图5分别是利用该控制器完成读、写操作的时序图。读操作的CAS延迟为两个时钟。

该SDRAM控制器在中频数据海量存储系统中已得到应用。数据接收逻辑将接收到的中频采样数据整理后(拼接成64bit),通过SDRAM控制器存入SDRAM阵列。存满后,数据输出逻辑将中频数据通过SDRAM控制器从内存条中取出,传输至上位机。其VHDL代码在ATERA公司的FPGA--EP1C6Q240中通过了Quartus II的仿真、综合和布局、布线。占用499个logic cellk,消耗了8%的逻辑资源。留有丰富的资源可提供给其它逻辑单元使用。

上面介绍了SDRAM的基本工作原理和一种简单的通用SDRAM控制器的实现。SDRAM的控制机制比较复杂,具有多种突发读、写方式和工作模式(详细内容请参考SDRAM的数据手册)。但是,可以根据实现应用,实现其中的一个子集(基本读、写、刷新操作)来满足实际系统的需要。用SDRAM实现大容量的高速数据缓存具有明显的优势,使用可编程器件实现SDRAM控制器则使之具有更高的灵活性,其应用前景广阔。

-

控制器

+关注

关注

112文章

16334浏览量

177815 -

SDRAM

+关注

关注

7文章

423浏览量

55205 -

计数器

+关注

关注

32文章

2256浏览量

94479 -

vhdl

+关注

关注

30文章

817浏览量

128121

发布评论请先 登录

相关推荐

如何使用Verilog实现基于FPGA的SDRAM控制器?

存储器接口vhdl代码全集

SDRAM控制器参考设计,Lattice提供的VHDL源代码

SDRAM控制器的设备与VHDL实现

使用Verilog实现基于FPGA的SDRAM控制器

SDRAM控制器的设计

FPGA读写SDRAM的实例和SDRAM的相关文章及一些SDRAM控制器设计论文

如何使用FPGA设计SDRAM控制器

DDR SDRAM控制器的设计与实现

基于FPGA的SDRAM控制器的设计与实现简介

基于FPGA的DDR3SDRAM控制器设计及实现

VHDL工具实现SDRAM控制器的要点分享

VHDL工具实现SDRAM控制器的要点分享

评论