在激光雷达中,使用FPGA实现TDC时需要手动约束进位链的位置。这里简单记录下。

Efinity从2022.1开始支持逻辑锁定,从2022.2开始支持逻辑和布线锁定。当然锁定布线时也要锁定相应的逻辑

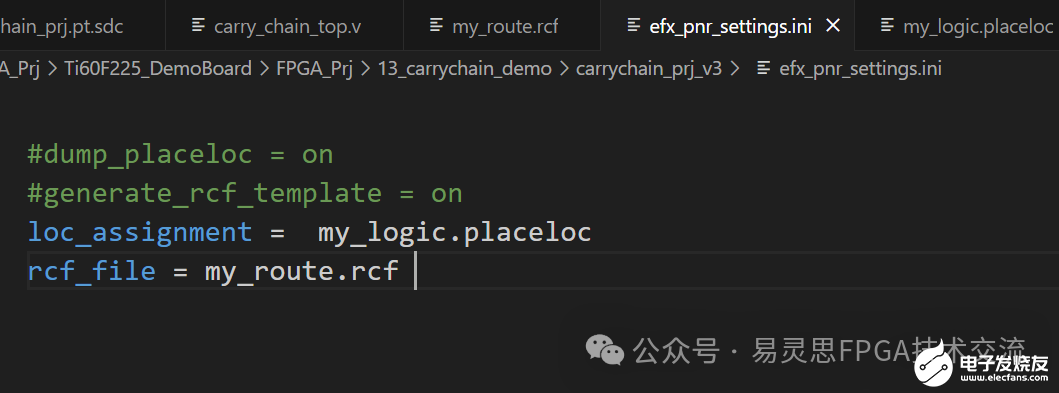

因为手动约束是处于开发阶段,Efinity 2022.1,2022.2,2023.1中需要使用.ini文件

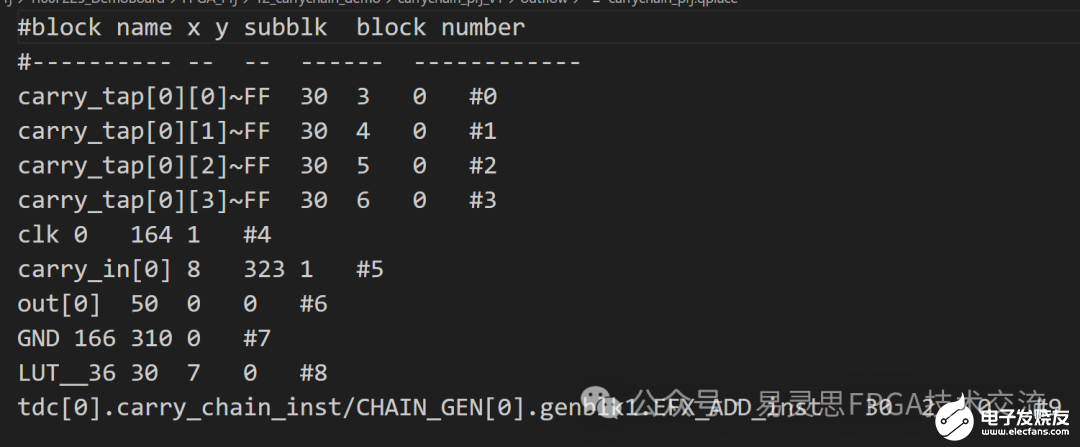

在outflow下会生成一个.qplace文件。用于指示布线的各个原语资源的分布位置 。

它的内容主是

是原语的单元名

表示水平位置,对应floorplan.

表示垂直位置 ,对应floorplan.

表示子块的位置 。目前只DSP24和DSP12可以有子块。在一个block可以指定多个字块。

是给block的一个编号,从0开始往下排。

锁定过程如下[老的方法]:

stp1:并把outflow下面的.qplace文件得到到工程目录下(可以修改名字也可以不修改,假如我们修改为carrychain.qplace)。把该qplace文件中想要锁定的block保留,其余可以删除。

stp2:在工程目录下建一个efx_pnr_settings.ini文件 。

stp3:在efx_pnr_settings.ini文件中输入

fix_pins=carrychain_prj.qplace

stp4:重新编译。

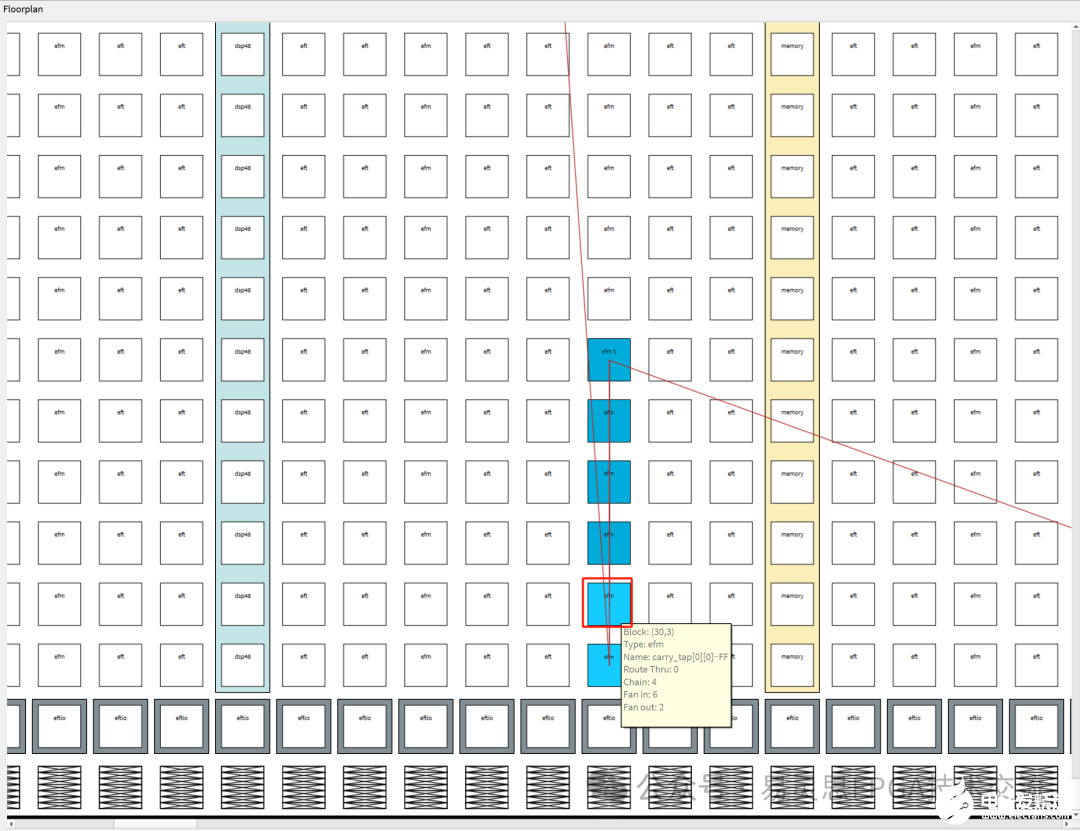

以加法进位链为例 ,上面我们生成了一个4级的加法进位链。具体约束在哪个位置可以在floorplan中确认位置 。

比如这里我们把它的位置约束到第8列。看下面的语句,第二行是进位链的输入位置用于进入进位链,第3,4,5,6依次约束进位链的carry_tap[0][x]~FF即可。

之前也有一个疑问是是否应该约束加法器,但是资源列表中并没有相应的资源,而且经过分析也认为只需要约束寄存器即可。

#block name x y subblk block number#---------- -- -- ------ ------------carry_tap[0][0]~FF 8 3 0 #0carry_tap[0][1]~FF 8 4 0 #1carry_tap[0][2]~FF 8 5 0 #2carry_tap[0][3]~FF 8 6 0 #3tdc[0].carry_chain_inst/CHAIN_GEN[0].genblk1.EFX_ADD_inst 8 2 0 #2605

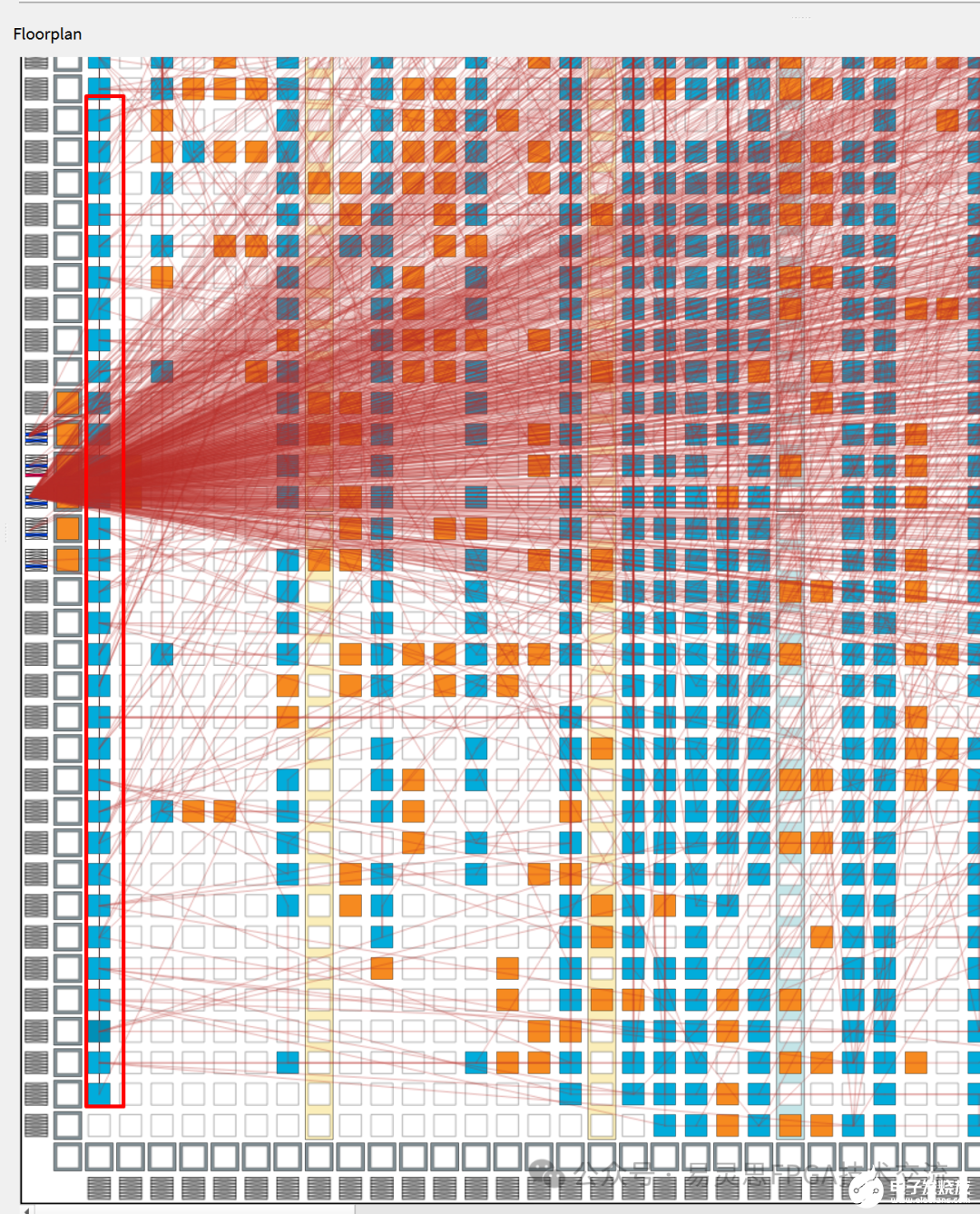

约束的效果如下:

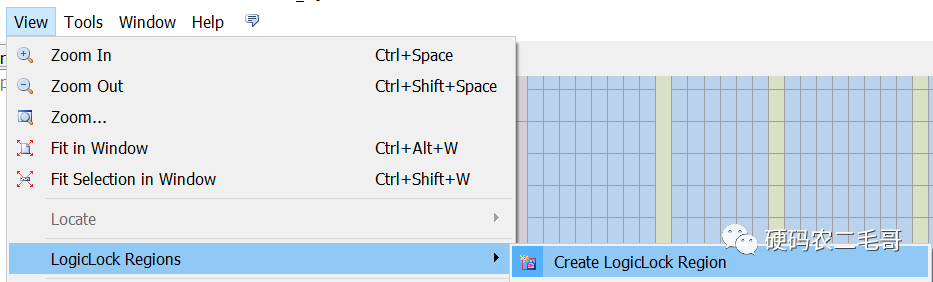

逻辑锁定【新的方法】

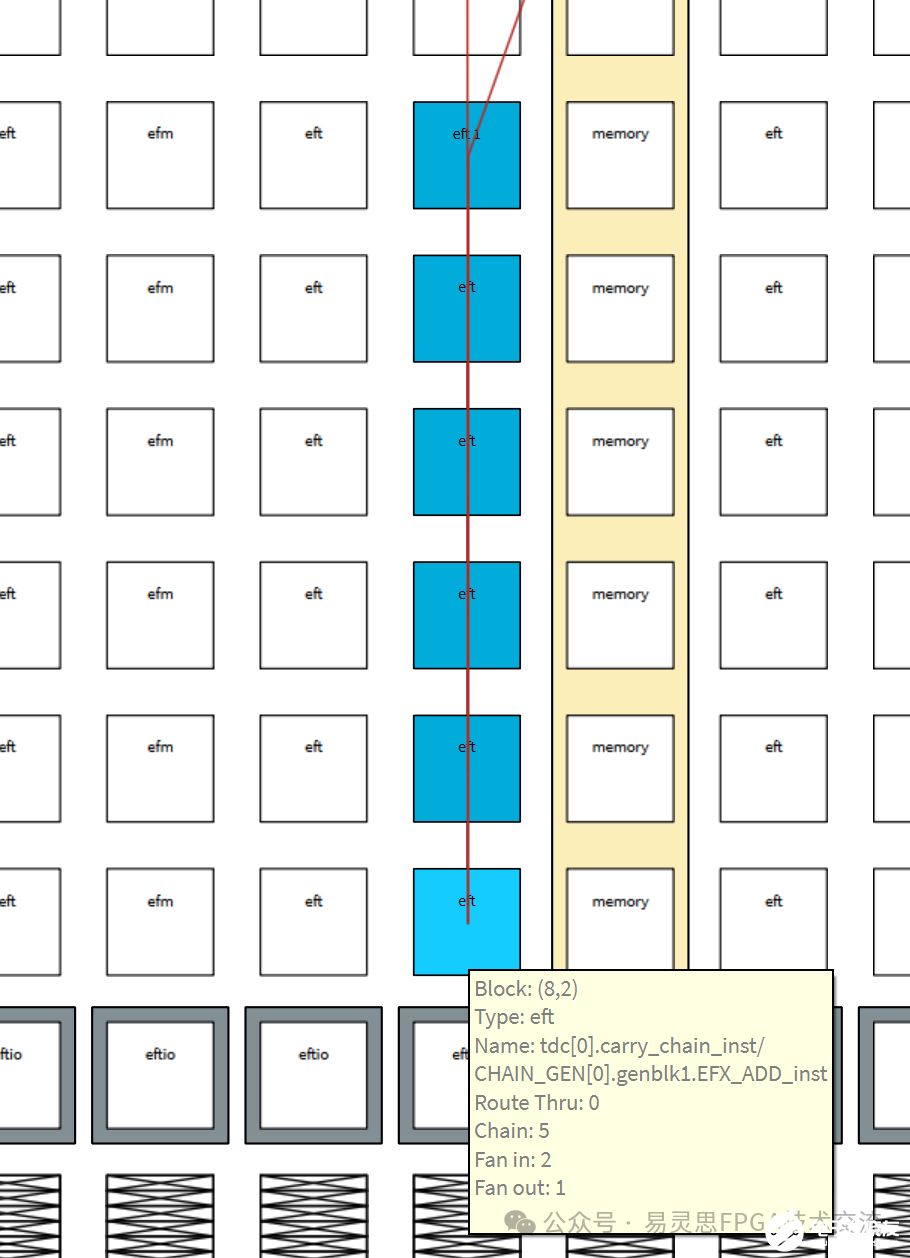

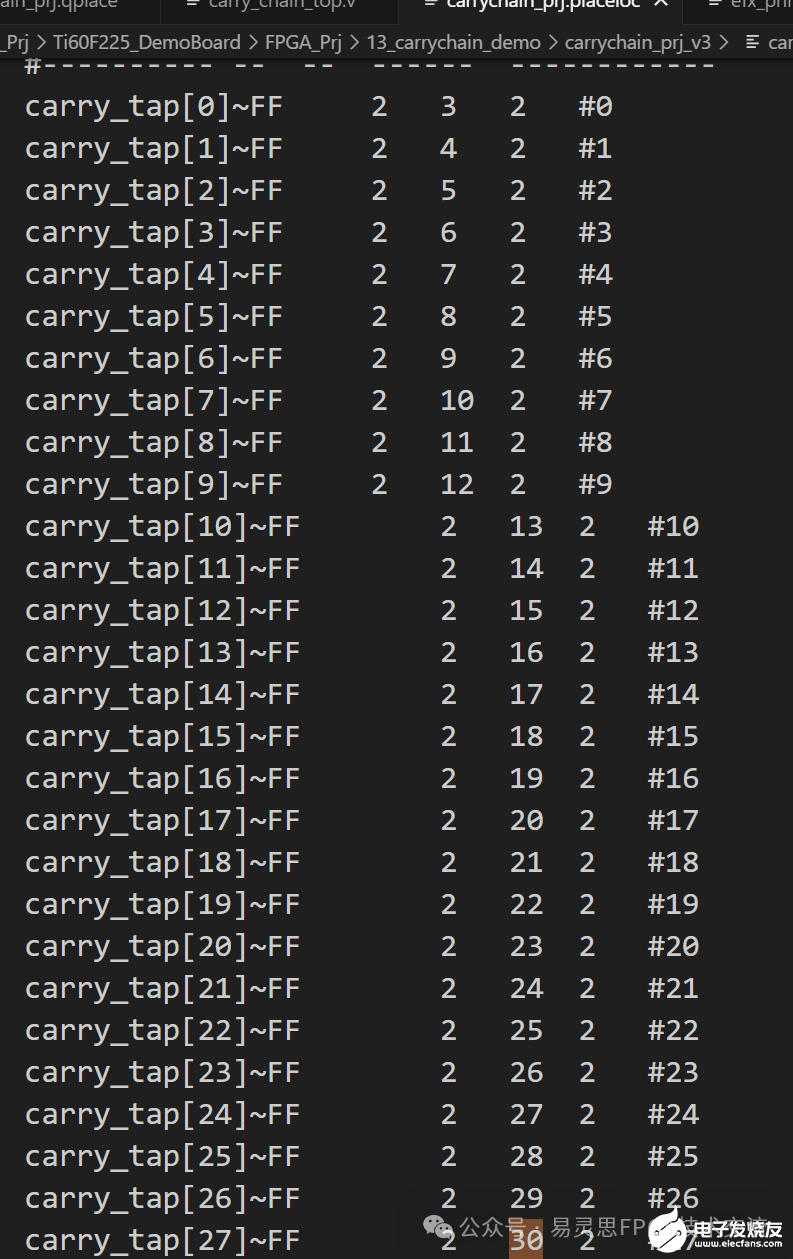

(1)在工程目录下新建一个efx_pnr_settings.ini文件,并输入dump_placeloc = on,编译;在在outflow文件夹下生成一个<工程名>.out.placeloc文件。

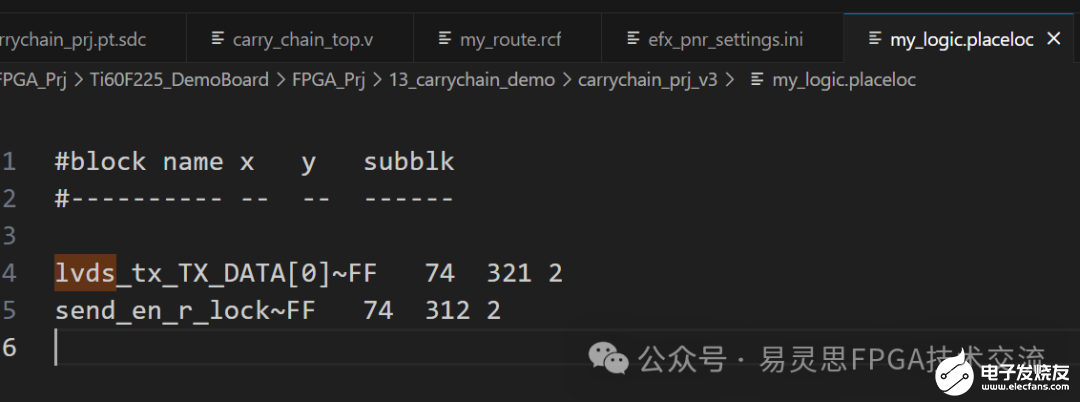

(2)新建文件my_logicloc.placeloc(文件名可以自己定义),把<工程名>.out.placeloc内部想要锁定的信息复制到my_logicloc.placeloc,下面是以进位链为例进行说明

(3)重新编译,然后打开floorplan查看,这里我们把进位链锁在第2列。

走线锁定

从v2022.2开始,截止到2024.1目前走线锁定只适用于钛金系列FPGA。

布线的锁定是要和逻辑锁定一起使用的。

(1)确认自己想要约束的路径

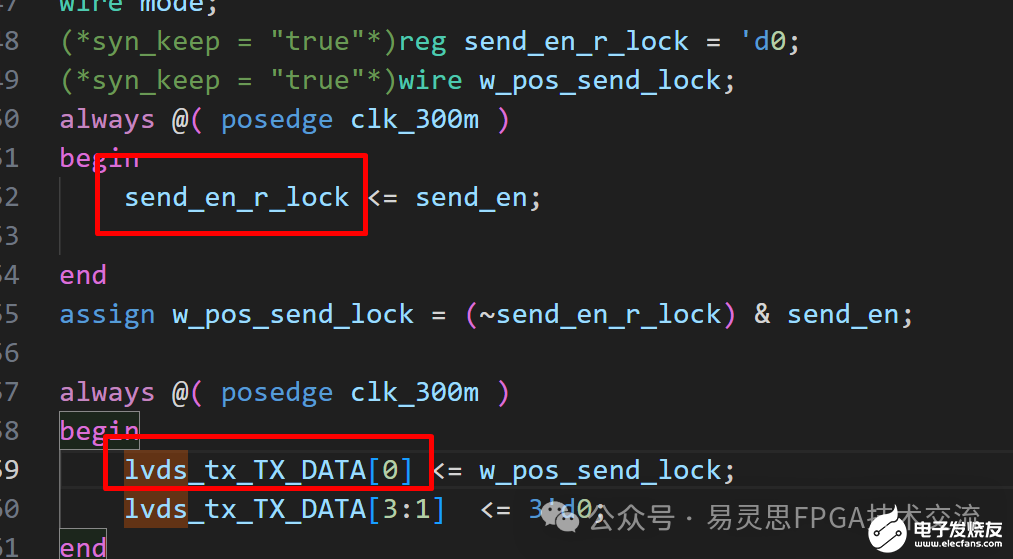

我们从程序上找一条路径,从send_en_r_lock信号到lvds_tx_TX_DATA[0]

易灵思推荐使用统一的名字对需要锁定的信号进行命名,比如netname_LOCKED,可以方便我们在模版文件中快速定位这些信号。并使用(**syn_keep = “true"*)属性防止信号被优化。当然名字是可以任意的,只要能区别清楚都是可以的。

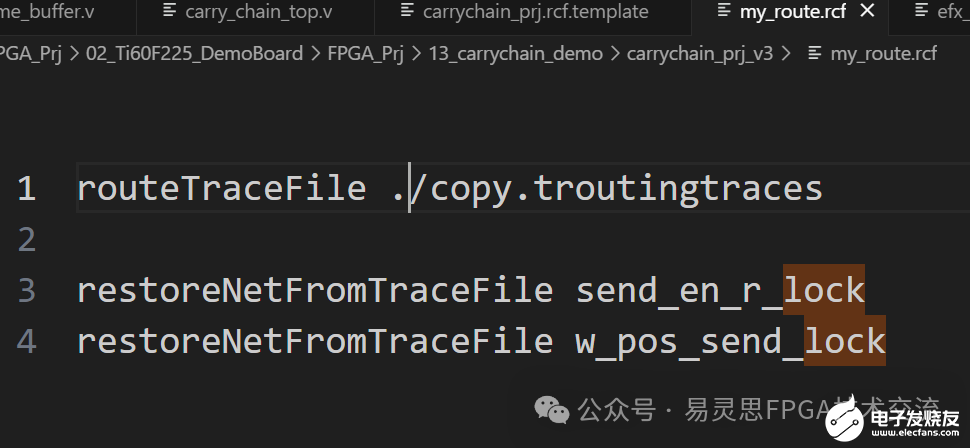

这个链路的src是send_en_r_lock,des寄存器是lvds_tx_TX_DATA[0],中间经过的路径是send_en_r_lock和w_pos_send_lock。这两条路径在.rcf.template中都能找到。

(2)在工程目录下新建一个efx_pnr_settings.ini文件,并输入

dump_placeloc = ongenerate_rcf_template = on

编译之后。在在outflow文件夹下生成一个.out.placeloc和.out.rcf文件。这两个文件分别对应布局和布线信息。还有.troutingtraces和.rcf_reference.troutingtraces

(2)把这三个文件拷备出来,比如放到工程目录下。

目前的现象是troutingtraces文件如果不修改名字会每次编译时被清除

(3)把你希望约束的cells和nets复制到自己的.placeloc和.rcf文件中。这里我们命名为my_route.rcf和my_logic.palceloc

在my_rout.rcf文件中添加了下面的语句 ,要注意自己的rcf文件中不能指定outflow文件夹下面的.troutingtraces文件 。该语句从.rcf.template中可以换到

在my_logic.placeloc中添加了要锁定的起始和结束位置

(4)并把自己的文件添加到.ini文件中。

loc_assignment =/ .placeloc rcf_file = / .rcf

efx_pnr_settings.ini文件中内部如下:

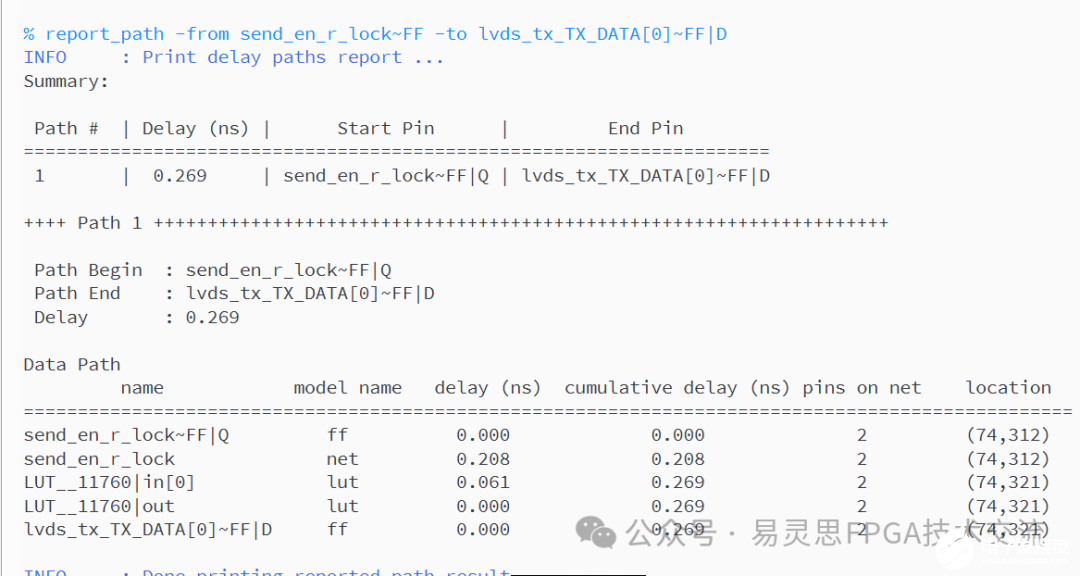

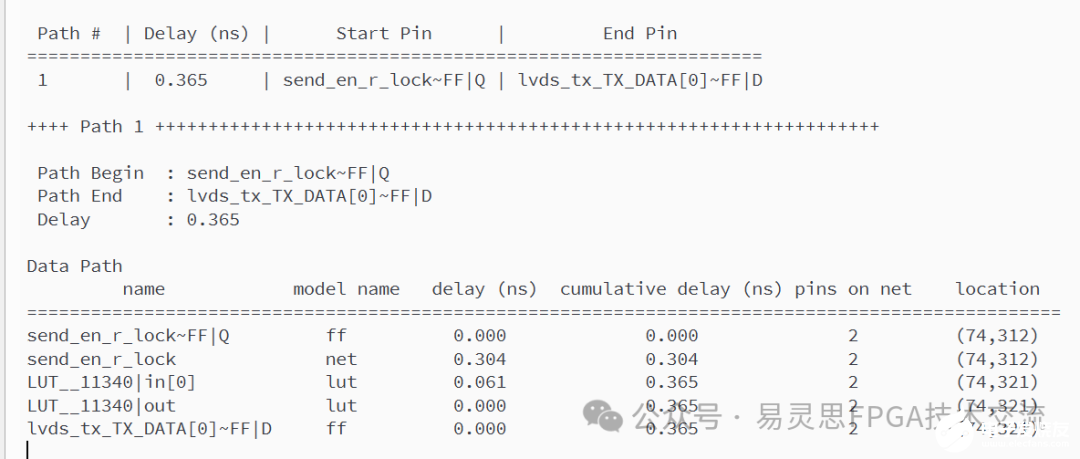

编译之后查看路径延时

% report_path -from send_en_r_lock~FF -to lvds_tx_TX_DATA[0]~FF|D

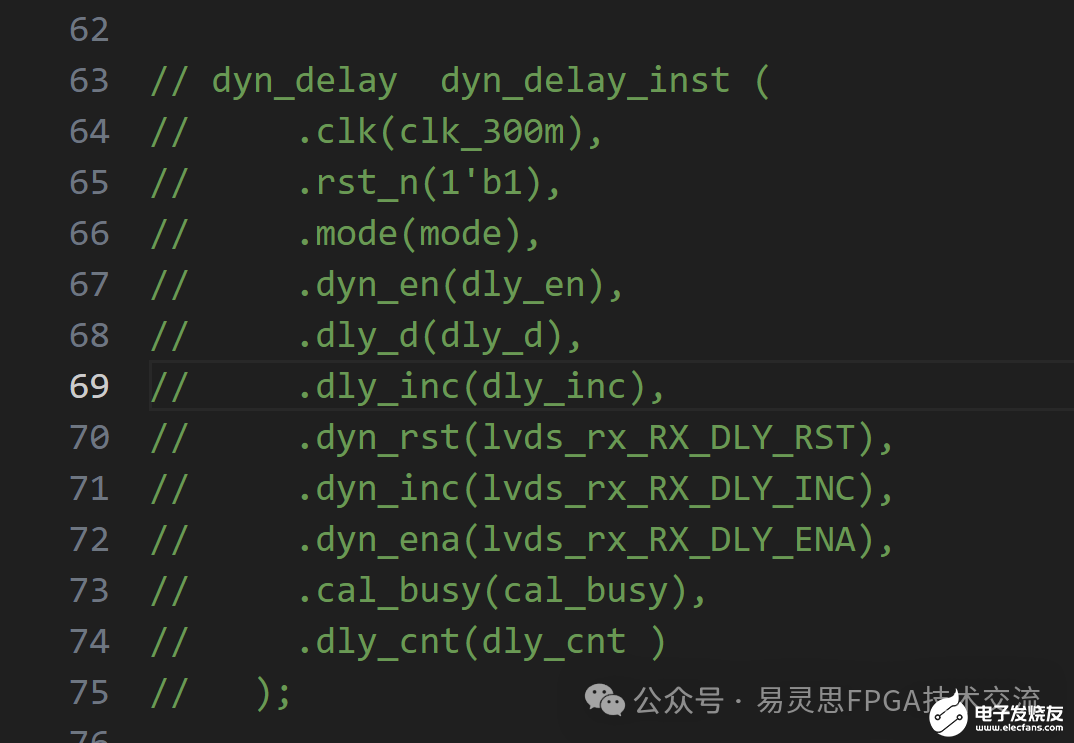

当把把程序屏蔽一部分之后走线延时能确定下来(在没有完整的使用该功能之前编译延时是会变化的):

测试程序如下:

-

FPGA

+关注

关注

1629文章

21729浏览量

603012 -

布线

+关注

关注

9文章

771浏览量

84322 -

TDC

+关注

关注

0文章

37浏览量

13776 -

易灵思

+关注

关注

5文章

46浏览量

4862

发布评论请先 登录

相关推荐

基于DSP威廉希尔官方网站 实现数字锁定放大器的设计和应用分析

ad 自动布线 如何锁定GND 让其他的自动布线

快速解决ADF5356频率锁定位

基于Altera系列器件的逻辑锁定方法学在FPGA设计中的应

LogicLock逻辑锁定简介

基于MATLAB仿真的锁定放大器的研究

如何在Vivado中实现逻辑锁定和增量编译工程实例说明

逻辑布线锁定 用FPGA实现TDC时的逻辑锁定和布线锁定

逻辑布线锁定 用FPGA实现TDC时的逻辑锁定和布线锁定

评论